UPTEC F 02 096

# Simple and Efficient Instrumentation for the DSZOOM System

OSKAR GRENHOLM

Supervisor: Zoran Radovic

Examiner: Professor Erik Hagersten

# UPPSALA UNIVERSITY

# Simple and Efficient Instrumentation for the DSZOOM System

by Oskar Grenholm

December 2002

Computer Systems Department of Information Technology Uppsala University Uppsala Sweden

Dissertation for the degree of Master of Science in Engineering at Uppsala University 2002

#### Simple and Efficient Instrumentation for the DSZOOM System

Oskar Grenholm osgr8555@student.uu.se

Computer Systems Department of Information Technology Uppsala University Box 337 SE-751 05 Uppsala Sweden

http://www.it.uu.se/

© Oskar Grenholm 2002 ISSN 1401-5757 Printed by the Department of Information Technology, Uppsala University, Sweden

# Abstract

An efficient and robust instrumentation tool (or compiler support) is necessary for an efficient implementation of fine-grain software-based shared memory systems (SW-DSMs). The DSZOOM system, developed by the Uppsala Architecture Research Team (UART) at Uppsala University, is a sequentially consistent SW-DSM originally developed using EEL (Executable Editing Library) - a binary modification tool from University of Wisconsin-Madison. In this thesis, we identify several weaknesses of this original approach and present a new and simple tool for assembler instrumentation. This tool can instrument (modify) highly optimized compiler output for the newest UltraSPARC processors. Currently, the focus of the tool is load-, store-, and load-store-instrumentation.

We also present several low-level optimization techniques that significantly improve the performance of the DSZOOM system. One of the presented techniques is a store-buffer register optimization, a latency-hiding mechanism for memory-store operations, that can lower instrumentation overheads for some applications (as much as 45% for LU-cont, running on two nodes with 8 processors each).

We also show that by using this new DSZOOM system we execute faster than the old one on all applications in the SPLASH-2 benchmark suite. Improvements range from 1.07 to 2.82 times (average 1.73).

# Contents

| 1 | Intro | oductio | on and a second s | 4  |

|---|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 | DSZ   |         | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6  |

| 3 | Targ  | get Arc | hitecture Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8  |

|   | 3.1   | Origin  | al Proof-of-Concept Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8  |

|   | 3.2   | SPAR    | C V9 ABI Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8  |

|   | 3.3   | Compi   | llers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9  |

| 4 | Nev   | v DSZC  | OM Instrumentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11 |

|   | 4.1   | Why a   | New Tool?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11 |

|   | 4.2   | The Id  | ea Behind It                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12 |

|   | 4.3   | Impler  | nentation Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14 |

|   |       | 4.3.1   | Parsing SPARC Assembler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14 |

|   |       | 4.3.2   | Liveness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16 |

|   |       | 4.3.3   | Handling Delay Slots                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18 |

|   | 4.4   | Using   | the Instrumentation Tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19 |

|   | 4.5   | Limita  | tions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21 |

| 5 | Low   | /-Level | Optimization Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23 |

|   | 5.1   | Proof-  | of-Concept Snippets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23 |

|   |       | 5.1.1   | Integer Load Snippets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23 |

|   |       | 5.1.2   | Floating-Point Load Snippets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 24 |

|   |       | 5.1.3   | Store Snippets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24 |

|   | 5.2   | New C   | Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24 |

|   |       | 5.2.1   | Reducing the Number of Instructions and the MTAG Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26 |

|   |       | 5.2.2   | Straightening Out the Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26 |

|   |       | 5.2.3   | Removing Local Memory Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27 |

|   |       | 5.2.4   | Optimization of the Store Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28 |

| 6  | Performance Study 32 |                                                 |    |  |  |  |  |

|----|----------------------|-------------------------------------------------|----|--|--|--|--|

|    | 6.1                  | Experimental Setup                              | 32 |  |  |  |  |

|    | 6.2                  | Applications                                    | 32 |  |  |  |  |

|    | 6.3                  | Performance Overview                            | 32 |  |  |  |  |

|    | 6.4                  | Performance When Removing Local Memory Accesses | 37 |  |  |  |  |

| 7  | Con                  | clusions                                        | 40 |  |  |  |  |

| Re | ferer                | ices                                            | 42 |  |  |  |  |

# 1 Introduction

Today clusters of symmetric multiprocessors (SMPs) are providing a powerful platform for executing parallel applications. To allow for shared-memory applications to run on such clusters, software distributed shared memory (SW-DSM) systems can help support the illusion of shared memory across the cluster via a software run-time layer between the application and the hardware. This approach can potentially provide a cost-effective alternative to hardware shared memory systems for executing certain classes of workloads. Also the upper scalability of large hardware distributed shared memory systems can extend by connecting several of them via SW-DSM technology.

Most SW-DSM systems keep coherence between page-sized coherence units [Li88], [CBZ91], [KCDZ94]. The normal per-page access privilege of the memory-management unit offers a cheap access control mechanism for these SW-DSM systems. But this large page-size coherence units in the earlier SW-DSM systems created extra false sharing and caused frequent page transfers of large pages between nodes. In order to avoid most of the false sharing, weaker memory models have been used to allow many update actions to be lumped to a specific point in time, such as the lazy release consistency (LRC) protocol [Kel95].

Fine-grain SW-DSM systems with a more traditional cache-line-sized coherence unit have also been implemented. Here, the access control check is either done by altering of the error-correcting codes (ECC) [SFH<sup>+</sup>96] or by in-line code *snippets* (small fragments of machine code) [SFH<sup>+</sup>96], [SGT96]. The small cache-line size reduces the false sharing for these systems, but on the other hand the explicit access-control check adds extra latency for each memory access to global data. The most efficient access check reported to date is three extra instructions adding three extra cycles for each load to global data [SFH<sup>+</sup>98].

At Uppsala University the DSZOOM-WF system has been implemented. This is a sequentially consistent fine-grain distributed software-based shared memory, between the nodes of a Sun-WildFire [HK99] system without relying on its hardware-based coherence capabilities. All loads and stores are instead performed to the node's local "private" memory. An unmodified version of executable editing library (EEL) [LS95] is used to insert fine-grain access control checks before shared-memory loads and stores in a fully compiled and linked executable. Global coherence is resolved by coherence protocol implemented in C that copies data to the nodes "private" local memory by performing loads and stores from and to remote memory.

This system has been tested and shown to work well with respect to instrumentation overhead. Still this way of instrumenting the binaries directly gives rise to a couple of problems. Mainly this is because of EEL having some limitations in its capabilities to instrument all kind of binaries. Namely EEL does not handle to instrument all cases of instructions placed in delay slots correctly, thus usually making it impossible to instrument any executables compiled with an optimization level above the lowest.

To avoid this limitation we have decided to use an alternative approach to binary instrumentation. Instead we instrument the assembler output from the compiler, and insert the snippets needed.

The compiler finishes it's job of making it all into an executable. By doing the actual instrumentation at the assembler level we can analyze the code and re-arrange the code in a way that let us avoid loads and stores in delay slots. The problem of inserting code snippets is now reduced to inserting correct assembler code, as text, into a text file containing the assembler output of the program. But this also leads to some limitations of the instrumentation tool, the biggest being that we always have to have the source code of the program we want to instrument. This is not a problem when the EEL is used.

The remainder of this paper is organized as follows. Section 2 gives an introduction to a general DSZOOM system. A presentation of the target architecture used to build DSZOOM on is given in section 3. Section 4 shows how the new Instrumentation tool works. In section 5 we have collected together all the optimizations done to the new system and finally in section 6 we give a overview of the results obtained.

# 2 DSZOOM Overview

In this section we give a short overview of the DSZOOM system. The DSZOOM proposal is described in a couple of previous papers in more detail by Radovic and Hagersten [RH01a],[RH01b].

Each DSZOOM node could either be a standard single processor machine, a symmetric multiprocessor (SMP), or a CC-NUMA cluster. The node hardware keeps coherence among the caches and the memory within each node. The different cluster nodes run different kernel instances and do not share memory with each other in a hardware-coherent way.

DSZOOM assumes a cluster interconnect with an inexpensive user-level mechanism to access memory located in other nodes, similar to the remote put/get semantics found in the cluster version of the Scalable Coherent Interface (SCI), or the emerging InfiniBand interconnect proposal that supports efficient user-level accesses to remote memory (RDMA READ/WRITE) as well as the atomic operations to smaller pieces of data (CmpSwap and FetchAdd). The remote atomic operation enables the implementation of the *blocking directory protocol*, a hardware coherence protocol implementation presented by Hagersten and Koster [HK99] that eliminates many of the potential race conditions and simplifies the verification of coherence protocols. Most of the complexity of a coherence protocol is related to the race conditions caused by simultaneous requests for the same cache line. In a blocking directory proposal, the processor that has detected the need for global coherence activity will first acquire a lock associated with the cache line before starting the coherence activity itself. The directory entry is locked with either one local atomic memory operation if the entry happens to reside in the same node, or with one remote atomic memory operation if the entry is located in remote node. By implementing the distributed version of the blocking directory protocol entirely in software, DSZOOM has demonstrated that all interrupt- and/or poll-based asynchronous protocol processing, found in almost all traditional SW-DSM implementations, is completely removed by running the entire coherence protocol in the requesting processor. This not only removes the asynchronous overhead, but also makes use of a processor that otherwise would stall.

All SW-DSM systems have to detect accesses to data that is not available locally. In contrast to page-based systems that rely on the virtual memory hardware (page faults) to detect accesses to locally unavailable data (for example, fine-grained SW-DSMs like Shasta [SGT96], [SG97a], [SG97b], Blizzard-S [SFL<sup>+</sup>94], Sirocco-S [SFH<sup>+</sup>98], or DSZOOM [RH01b] insert code snippets (small fragments of machine code) to the application binary at loads and stores to perform checks during the runtime if remote accesses are needed or not (we will refer to this operation as an *access control check*). On the upside, the fine-grained approach reduces false-sharing because coherency units are comparable to the hardware implementations, typically 64 bytes large, and accordingly minimizes the need for large unnecessary data transfers. This approach also allows quite efficient implementations of strict memory models, such as sequential consistency (SC). This is very important because many of the popular commercial architectures support only relatively strict memory consistency models, e.g., Intel's x86 architecture supports processor consistency that is a little less strict model compared to the SC. Many of the recent page-based systems use very relaxed memory models such as the lazy release consistency (LRC), in order

to solve false sharing problems that arise from page-sized coherency units. In practice, this will disallow the use of many advanced protocol optimizations for such systems in case of transparent binary execution across the cluster. On the downside, the binary instrumentation technique adds extra latency for each load or store operation to global data, independently if that data is locally available or not. On average, the speedup difference between the original DSZOOM and the hardware-based CC-NUMA system is around 30% for the studied SPLASH-2 applications [WOT<sup>+</sup>95], where the in-line checks (ILC) for global loads and stores are clearly the largest overhead [RH01b].

DSZOOM uses the executable editing library (EEL) [LS95] to insert fine-grain access control checks after shared-memory loads in a fully compiled and linked executable. This technique is usually called for binary instrumentation. Range checks and node-local MTAG lookups before global stores are also added. All global/shared memory is allocated in the G\_MEM area (starting at 0x80000000), that is why DSZOOM must dynamically check if loads and stores are targeting that area or not. Static data and stack accesses are ignored during the instrumentation phase, i.e., they will not be replaced by any snippets. If fine-grain access control check or MTAG lookup fails, the coherence routine is going to be called from DSZOOM's in-line snippets. Global coherence is resolved by a coherence protocol implemented in C that copies data to the node's private local memory by performing loads and stores from remote memory.

## 3 Target Architecture Overview

In this section some background about the system used to implement DSZOOM on is given. This refers to aspects of both the old and the new version.

#### 3.1 Original Proof-of-Concept Platform

The system used to host the original proof-of-concept DSZOOM was a Sun Enterprise E6000 SMP with 16 UltraSPARC II (250 MHz) processors running Solaris 2.6. The compiler used to compile both EEL and the SPLASH-2 benchmark programs was gcc-2.8.1. The benchmark programs were compiled without any optimization, that is given the flag -O0. This was because EEL could not instrument the binaries produced otherwise. EEL was used to instrument the binaries so that specific code snippets designed for DSZOOM was inserted at loads and stores. The snippets then performed the necessary checks and if necessary called routines implemented in C that kept coherence.

The proof-of-concept implementation was tested thoroughly on this platform and for further information on that system and the results obtained, see [RH01b].

#### 3.2 SPARC V9 ABI Restrictions

In order to make the snippets efficient with respect to register usage, we need to have some free registers at our disposal. The way this has been solved, both in the original DSZOOM and in this new one, is to compile the programs, telling the compiler not to use all of the registers. Thus, those unused registers are free to use as we like.

But for this to work we need to pay attention to be compliant with all SPARC ABI specifications, and especially with global register usage [Sun02]. Currently DSZOOM requires two free global registers at the insertion point during the instrumentation phase to pass parameters to the coherence routines in an efficient way from the in-line code snippets. On SPARC V8 (32-bit) and SPARC V8plus (64-bit) there are three global thread-private registers that are saved/restored during the thread-switching by the Solaris system libraries: %g2, %g3, and %g4; all other global registers are thread-global and are not saved during the switch. The thread-private registers are also called application registers. On SPARC V9 (64-bit) on the other hand, only %g2 and %g3 are application registers, and the %g4 register is free for general use and is volatile across function calls together with %g1 and %g5. On all targets, registers %g6 and %g7 are reserved for system software and are not used during the binary modification process. As mentioned above we need two registers to pass arguments. For this we have choose to use registers %g3 and %g4. On SPARC V8 or V8plus this leaves one extra register, %g2, to use. This register is used to make the snippet a bit more efficient, in such a way that we can take away one or two instructions. There is also another, greater optimization that can be implemented if there is an extra register free. What this is will be mentioned later on in the paper.

As seen, this implementation, only having to use two global registers in the snippet, also allows us to implement DSZOOM on SPARC V9. But then the extra optimizations, made available by the extra application register on SPARC V8 or V8plus, are no longer applicable.

#### 3.3 Compilers

The compiler used to produce the assembler output and the executables is Sun WorkShop 6 update 2 C 5.3 Patch 111679-08. To us there exist a couple of flags available for this compiler that have greater importance than the others. The flags to chose optimization level are among those and the -S flag. A brief overview of these flags, taken from the Forte Developer 6 update 2 manual [Sun01], is given here.

-S Directs cc to produce an assembly source file but not to assemble the program.

**-xregs=r[,r...]** Specifies the usage of registers for the generated code. r is a comma-separated list that consists of one or more of the following: [no%]appl, [no%]float. The -xregs values available are:

*appl*: Allows the use of the following registers: g2, g3, g4 (v8a, v8, v8plus, v8plusa, v8plusb) g2, g3 (v9, v9a, v9b) In the SPARC ABI, these registers are described as application registers. Using these registers can increase performance because fewer load and store instructions are needed. However, such use can conflict with some old library programs written in assembly code.

*no%appl*: Does not use the appl registers.

*float*: Allows using the floating-point registers as specified in the SPARC ABI. You can use these registers even if the program contains no floating-point code.

*no%float*: Does not use the floating-point registers. With this option, a source program cannot contain any floating-point code.

Example: -xregs=appl,no%float. The default is -xregs=appl,float.

-**xO[1|2|3|4|5]** Optimizes the object code; note the upper-case letter O. The levels (1, 2, 3, 4, or 5) you can use with -xO are described below.

-x01 Does basic local optimization (peephole).

-*xO2* Does basic local and global optimization. This is induction variable elimination, local and global common subexpression elimination, algebraic simplification, copy propagation, constant propagation, loop-invariant optimization, register allocation, basic block merging, tail recursion elimination, dead code elimination, tail call elimination, and complex expression expansion. The -xO2 level does not assign global, external, or indirect references or definitions to registers. It treats these references and definitions as if they were declared volatile. In general, the -xO2 level results in minimum code size.

*-xO3* Performs like *-*xO2, but also optimizes references or definitions for external variables. Loop unrolling and software pipelining are also performed. This level does not trace the effects of pointer assignments. When compiling either device drivers, or programs that modify external variables from within signal handlers, you may need to use the volatile type qualifier to protect the object from optimization. In general, the -xO3 level results in increased code size.

-xO4 Performs like -xO3, but also automatically inlines functions contained in the same file; this usually improves execution speed. If you want to control which functions are inlined, see -xinline=list. This level traces the effects of pointer assignments, and usually results in increased code size.

-xO5 Attempts to generate the highest level of optimization. Uses optimization algorithms that take more compilation time or that do not have as high a certainty of improving execution time. Optimization at this level is more likely to improve performance if it is done with profile feedback. See -xprofile=p.

**-fast** Selects the optimum combination of compilation options for speed. This should provide close to the maximum performance for most realistic applications. Modules compiled with fast must also be linked with fast. The fast option is unsuitable for programs intended to run on a different target than the compilation machine. In such cases, follow -fast with the appropriate -xtarget option. The fast option is unsuitable for programs that require strict conformance to the IEEE 754 Standard. The following table lists the set of options selected by -fast on the SPARC platform.

-dalign, -fns, -fsimple=2, -fsingle, -ftrap=%none, -xarch,

-xbuiltin=%all, -xlibmil, -xtarget=native, -xO5

fast acts like a macro expansion on the command line. Therefore, you can override the optimization level and code generation option aspects by following -fast with the desired optimization level or code generation option. Compiling with the -fast -xO4 pair is like compiling with the -xO2 -xO4 pair. The latter specification takes precedence. You can usually improve performance for most programs with this option. Do not use this option for programs that depend on IEEE standard exception handling; you can get different numerical results, premature program termination, or unexpected SIGFPE signals.

# 4 New DSZOOM Instrumentation

This section contains an argumentation of why this new tool is needed. Then it will explain what is new and how it is implemented.

#### 4.1 Why a New Tool?

As mentioned earlier there are some things with EEL that we see as a problem with regard to what we want to do. The main concern from our side is that there are a great number of binaries that EEL can not instrument. First of all EEL itself is unmaintained. This means that it does not handle to instrument newer binaries, that is programs that are compiled with one of the latest versions of compilers. This can partly be blamed on the fact that EEL is written with a lot of old code (non-ANSI C/C++). Due to this EEL itself can not be compiled using new compilers. Also EEL has a problem to handle hand-written assembler and that does usually lead EEL to make some erroneous analysis in those cases. A third set of binaries that EEL does not always handle correctly is the ones where the .code and .data segments are mixed together. In those cases it is hard knowing what is instructions and what is constants of data. On the other hand this is not a problem when doing the instrumentation at assembler level, where it is always well defined what is code and what is data. Finally, there is the problem that leads to EEL not being able to instrument all binaries compiled with any kind of optimization. Because in binaries that are optimized one of the first optimizations to be applied is the one of putting instructions in the delay slots. Since EEL has a problem instrumenting loads and stores that are placed in delay slots this leads to many optimized binaries not suitable for instrumentation by EEL in the DSZOOM case.

Besides some technical limitations to EEL there is also the issue that it is rather cumbersome to write and change snippets using EEL. What you have to do is to write a program in C/C++ (using EEL) that does the actual instrumentation and if you want to change your snippet you have to rewrite this program and compile it again. Rewriting a snippet is not as simple as you may think. If you want to just add some extra instructions, thereby making the snippet larger, and if you before had some branches you have to change the offset to branch on for all these branches. This is because all branches inserted by EEL into the binary are to an absolute address and not to a label. This is not a problem at all when inserting snippets into assembler code, here you can make up all the new labels you want (as long as they have unique names) and then just branch to them. Overall it is much easier to change and insert snippets using this new instrumentation tool. You just write the snippets in assembler code as text in a text file. Changes can be done in a text editor and then you just invoke the tool to insert these changes into the program to be instrumented.

So, in what ways does this new tool outsmart EEL? First of all it can instrument all kinds of loads and stores in delay slots, thus being able to instrument programs compiled at all optimizations levels. Also it is written to handle assembler output from one of the newest versions of Sun's Forte compiler and therefore handles code written for newer compilers. Another good thing that

comes from instrumenting at the assembler level is the one mentioned above, that you can easily insert new labels in your snippets and thereby allowing for more intelligence in the snippets. Furthermore the idea of inserting only ordinary assembler code and then letting the compiler finish its job, allows for standard binaries, instead of strange looking binaries that do not fall back on any standard, as is the result of EEL's binary instrumentation. This gives that standard tools for examining the binaries, for example the program analyzer, can perform as well as on any other binary.

#### 4.2 The Idea Behind It

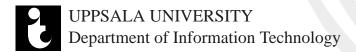

The process of making an executable suitable for the DSZOOM system earlier involved the following process: First of all the unmodified SMP application source code written with PARMACS macros is preprocessed with a m4 macro preprocessor. m4 replaces all macros with DSZOOM run-time library calls. Then the the preprocessed file is compiled and linked with the DSZOOM run-time library. The resulting file called the (Un)executable is then passed to the binary modification tool, which is based on an unmodified version of the executable editing library (EEL). The binary modification tool then inserts code snippets, containing fine-grain access control checks after shared-memory loads and range checks node-local MTAG lookups before global stores. The snippets also contain calls to the corresponding coherence protocol routines. This process is shown in Figure 1.

Figure 1: DSZOOM-WF original compilation process.

The problem with this approach comes mainly from limitations in EEL. And the main concern stems from the fact that EEL often has problems instrumenting binaries where the delay slots are

filled with anything else than nops, i.e., empty instructions. Thus if a load or a store is placed in a delay slot, it sometimes can not be instrumented. This limitation makes it impossible for EEL to instrument binaries that have been compiled with any optimization level above the lowest.

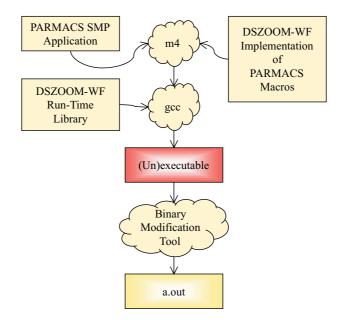

Our role in this is to implement a tool that uses a different approach on how to instrument a program and make it into an executable capable of being used in the DSZOOM system. This approach resembles the earlier process a lot, with the difference that the inserting of the code snippets is done on a higher level in the process. Here the assembler output from the compiler is instead analyzed and code snippets are inserted at loads and stores. Then the compiler is called again to finish it's job and make everything into an executable for the DSZOOM system. This executable is now a real executable and nothing further, i.e., binary modification, is needed before it can be run. The changes made to the process is shown in Figure 2.

Figure 2: The new compilation process for DSZOOM.

Actually, the changes made are quite small. In practice the same Makefiles can be used with only some minor modifications. An example of how a new Makefile can look is given in Figure 3. The compilation phase is broken in two phases. First the compiler is forced to compile the C

source code and to produce assembler output to a .s file. This is done by giving the compiler the -S flag. Then the tool instruments the .s file and produces a new .s file with all the snippets inserted at the right places. Finally the compiler is used again to compile the .s file and link it with all the necessary libraries to make the executable.

Figure 3: An example of how a part of the Makefile for FFT looks. It is using the new Instrumentation Tool.

#### 4.3 Implementation Details

In this section more specific details on how the actual parsing and instrumentation is implemented is given. Also the tools involved in this creation are described.

The instrumentation tool created for use with the DSZOOM system is just an assembler parser with ability to insert code snippets at specified locations. To aid us in the creation of the parser JavaCC [Web02] was used. JavaCC is a parser generator for use with Java applications. A parser generator is a tool that reads a grammar specification and converts it to a Java program that can recognize matches to the grammar. Much like the classic tool yacc for the C programming language. With JavaCC it is also possible to write functions and additional code in Java that can decide what to do with the parsed code. The variables can be used to hold special data during the parsing.

#### 4.3.1 Parsing SPARC Assembler

The first thing to do was to try and come up with some kind of grammar for SPARC assembler code. For doing this, and knowing that the most important thing for us was mostly to leave the code as it was and insert extra code at some places, we chose the easiest route possible. Since the code that is supposed to be fed into this parser is generated by a compiler we assumed that

it already had some structure to it. The basic idea for our grammar was to find instructions, see what kind of instruction it was, notice what kind of arguments it had and then store it. Most things that was not an instruction was stored as it was for later, without caring about what it meant. The tokens we used for instructions were of different kinds. One that we used, Instruction3, was a token that recognized generic instructions with three arguments, among others Add and Sub. And Instruction2 was instructions with two arguments, such as Mov and Cmp. Other tokens used were Branch, obviously representing branches, for which special care had to be taken, and most important of all, Loads and Stores. Besides those mentioned a couple of other Tokens were used as well. All the Tokens are built up from regular expressions. An example of how the Tokens for Stores and Registers look is given in Figure 4.

The store token:

< STORE: ("st" | "stb" | "std" | "sth" | "stx") >

The token representing registers:

< REG: "%" ["r","g","i","o","l","f","s","y"] (["0"-"9","p","o","c"])\* >

Figure 4: Two examples of how the tokens in JavaCC looks. They represent different parts of an assembler program and are built up of regular expressions.

The parser goes through the code twice, inserts code snippets at appropriate places and then writes the instrumented code into a file. Between the two passes some additional work is done. Analysis of which registers are used are done (Liveness analysis), and problems regarding the placement of loads and stores in delay slots are analyzed and solved.

First of all this new tool goes through the assembler code and parses it in one sweep. During this pass it writes all of the instructions and arguments into a for this specially created structure. There it is stored for writing back to the instrumented file later. This structure consists of two different classes, implemented in Java, called Basic Block and Control Flow Graph (CFG). The formal definitions of Basic Blocks and Control Flow Graphs [CERL01] can be found in Figure 5. A Basic Block is just a collection of individual instructions. The set of instructions is always entered at the beginning and exited at the end. This means that they start with a Label and ends with a Branch, Jump or Call, or ends with the appearance of a new Label. The algorithm for dividing a long sequence of statements into Basic Blocks is quite simple. The parser just looks for a Label, then creates a Basic Block instance and adds all the following Instructions into that, until a Branch or a new Label is found, then a new instance of Basic Block is created and the old one is ended, and so on. This procedure is done once for every function block. At the end of a Basic Block there is some information stored about where the next Basic Block that can be executed is, so that we can now know how the flow of the program will go. There are some different kind of ways that a Basic Block usually can end [CERL01]:

**one-way** the last instruction in the basic block is an unconditional jump to a Label, hence, the block has one out-edge.

**two-way** the last instruction is a conditional jump to another Label, thus, the block has two out-edges.

**call** the last instruction is a call to a procedure. There are two out-edges from this block: one to the instruction following the procedure call, and the other to the procedure that is called. Throughout analyses, the called procedure is normally not followed, unless inter-procedural analysis is required.

**return** the last instruction is a procedure return instruction. There are no out-edges from this basic block.

**fall** the next instruction is the target address of a branch instruction (i.e. the next instruction has a Label). This node is seen as a node that falls through the next one, thus, there is only one out-edge.

Our model differs slightly from those definitions. In our case we do not do any distinction between conditional and unconditional branches, both are seen as two-way. In both cases we just store the Label that the branch is to and the Label that comes directly after the store. (The instruction in the delay slot is seen to belong to the Basic Block as well.) And since we do not try to do inter-procedural analysis we don not let our Basic Blocks end with a call, we just treat them as any other instruction. When the Basic Block just falls through, the Label of the next Basic Block is stored. And finally if the Basic Block ends with a Return statement of some kind, then this indicates that the flow for this function or program ends here and accordingly information about this is stored instead.

**Definition 1:** A basic block is a sequence of consecutive statements in which flow of control enters at the beginning and leaves at the end without halt or possibility of branching except at the end.

**Definition 2:** A control flow graph G = (N; E; h) for a program P is a connected, directed graph, that satisfies the following conditions: *h* is the unique entry node to the graph,  $\forall n \in N;$  n represents a basic blocks of P, and  $\forall e = (n_i; n_j) \in E; e$  represents flow of control from basic block  $n_i$  to basic block  $n_i$ , and  $n_j; n_j \in N$ .

Figure 5: The formal definitions of Basic Blocks and Control Flow Graphs.

After the creation of all the Basic Blocks, the flow of those are analyzed and a CFG is set up. A CFG is simply just a tree list over the different execution paths of the program. One CFG is built for each function in the program. Each node in this tree has a Basic Block and pointers to the next nodes (one or two pointers depending on if the exiting point is straight code or a branch) or a NULL pointer if it is a terminating point.

#### 4.3.2 Liveness

Armed with the information in the CFGs and the Basic Blocks, we can calculate the liveness of the registers in each Basic Block. Liveness is the information about which of the registers that holds values to be used later on in the program and which that can be overwritten without altering

the execution of the program. To be able to do this we need to know exactly which registers each instructions uses and defines (defs). To clarify, an assignment to a register defines that register and an occurrence of a register on the right-hand side of an assignment (or in other expressions) uses that register. For example in the statement, add %g1, %g2, %g3, registers %g1 and %g2 are used and %g3 is defined. To support this each Instruction writes to its Basic Block which registers it uses and defs. Those are stored in the Basic Block as a hash table. Knowing the different execution paths of a function and which registers each Basic Block uses and defs there is a simple algorithm for calculating the liveness at each Basic Block. This algorithm, originally implemented in Java, is given here in pseudo-code [App98] in Figure 6. This returns an hash table for each Basic Block in every CFG that holds those registers that are live at the entering point and at the exit point of the block. To know which registers that are free to use just take the once not included in the table.

Figure 6: Pseudo-code for the algorithm used to analyze the liveness of a function.

Although liveness is a great way to find out what registers you are allowed to use in your snippets, there are some downsides with this implementation. First of all, on higher optimization levels the optimization of the usage of the registers is very good. This means that there are seldom any free registers to find. On lower optimization or at none at all the task of finding registers is a much easier one. The second problem is that the liveness analysis is only intra-procedural. This is because it is done on CFGs and those only contain information on one function in the program. To know what limits this imposes on liveness it is necessary to know how the register-convention is built up in SPARC.

On SPARC there exists 32 registers, which are grouped in four different classes: global, local, in and out (%g0-7, %l0-7, %i0-7, %o0-7). The local registers are supposed to be scratch registers, the in registers are used to send parameters to functions and out are used to return values from functions. The global registers are a bit different. They are non-windowed as opposed to the rest. The difference between windowed and non-windowed is that windowed registers automatically are saved between function calls, i.e., the local registers that have the same name in different functions are actually not the same registers. The way this is handled is that the local and out registers are a totally new set, while the out of the previous function becomes the in of the new function, and so on for every function. Non-windowed registers on the other hand are the same between functions. This means that, without us knowing it from our liveness analysis, all the registers, except the local, can be used in another function calling the one we are analyzing. Therefore it is not safe to assume that registers are free just because they seem to be that within our CFG. Most of the time it is OK to make the assumption mentioned above, but one has to

remember that it is not always strictly so.

In addition to the set of 32 ordinary registers, there also exists a set of floating-point registers, some registers to hold both integer and floating-point condition codes, as well as a number of other miscellaneous registers. At this moment the liveness analysis does not handle the floating-point registers. This is because they are all global and we can not really know if they are being used in another function. And besides we do not have any need to know if they are alive or not since we do not use them in our snippets. Registers that we on the other hand use in our snippets and therefore need to do liveness analysis for are the condition code registers. But since they just are used and defined as ordinary registers, with the exception of implicit use and definition by some instructions, they can easily be analyzed as well. All we have to do is to take special care for the instructions that branches on a condition code register or that, like Cmp, sets a condition code register. This problem is no longer present in assembler code for the SPARC V9, since there the condition code register to branch on or set when comparing has to be explicitly named.

#### 4.3.3 Handling Delay Slots

One difference between what this new instrumentation tool can do and EEL, is that it can handle and instrument instructions that are placed in the delay slots of control-flow instructions. A delay slot means that the instruction after the jump or branch instruction is executed before the jump or branch is executed. This is done to keep the processor pipeline busy. An example of how a load is placed in a delay slot is given here.

bne %reg, .LABEL

Id [addr], %reg ! <- Delay slot instruction</li>

There exists three different kinds of situations that arise with regard to delay slots. They are in principle handled in the same way, but extra care has to be taken in two of the cases. This means that some extra checks has to be performed by the parser and that additional instructions has to be added. The three cases are described in more detail below.

#### Case 1

The way that we have chosen to handle loads and stores in delay slots is quite simple. First all instructions that give rise to delay slots are identified. These are branches of all kinds, calls, jumps and returns. When an ordinary instruction is found what we do is simply, as mentioned earlier, to write that instruction unmodified into a Basic Block. This has to be changed when dealing with delay slots. Here instead when an instruction that has a delay slot after it is found it is not written to the Basic Block, but into a temporary structure. This information is then kept until the next instruction is to be written, then accordingly to what instruction this next one is the information stored is written. Here are two different strategies used. If the instruction after the branch is just an ordinary instruction, the branch is just written to the Basic Block as usual.

Otherwise, if it is a load or a store that is to be instrumented, the load/store is written first, then the branch and finally a nop (to fill the delay slot) is written to the Basic Block.

#### Case 2

In addition to this there is some extra care that has to be taken in certain cases. Sometimes it is not possible to just lift out the instruction in the delay slot and place it before the branch. If the load in the delay slot is actually loading a new value into the register used to decide to branch or not, then this simple strategy would alter the execution path of the program. To avoid this, the contents of the register is moved to a temporary, free register and then this temporary register is instead used in the branch instruction. An example on how this can look is found below.

```

Before:

1: bne %reg, .LABEL

2: ld [addr], %reg

After:

1: mov %reg, %temp_reg

2: ld [addr], %reg

3: bne %temp_reg, .LABEL

4: nop

```

If there is no free register available, a register is spillt to memory and then this register is used. Then afterwards, the original content of the register is read back from memory again.

#### Case 3

Another tricky thing to handle with regard to loads/stores in delay slots are annulling delay slots. Here, depending on if the branch is taken or not, the execution in the delay slot is executed or not. In this case, just moving the load/store is not enough, we also have to do some additional code expansion. First of all, the original branch is replaced with a branch of the same kind, but with a different destination. The new destination is a new label created by our tool. At this label the load or store in the delay slot is instrumented and executed. If the branch is not taken, we reach another new label, but here the load or store is not executed. At the end of both the new blocks a branch always is taken. In the case where the load or store was executed this is to the actual label indicated by the original branch, otherwise the branch is to the label directly following the original branch. The code expansion taken from a real program is in Figure 7.

The effect of all the changes done in this manner to the delay slots in a program has been tested and has been shown to be only a slowdown of about 2-3%.

#### 4.4 Using the Instrumentation Tool

The most important thing this new parser does is to insert the code snippets needed to keep coherence, as implemented by DSZOOM. In DSZOOM, there are three different kinds of snippets that

```

//Original branch and store

1: bl,a,pt %icc,.L900000283

2: st %00,[%g1+%l2]

! <- Store to be instrumented

3: .L77000552:

//After the code expansion

1: bl.a.pt %icc,.LX686

2: nop

3: ba .LX687

4: nop

5: .LX686:

6: //Instrumentation inserted here

7: st %o0,[%g1+%l2]

! <- Original store</p>

8: //and here

9: ba .L900000283

10: nop

11: .LX687:

12: .L77000552:

```

Figure 7: How the annulling branch case is handled.

are needed. These are, one snippet to insert at global integer loads, one snippet for global floating point loads and one snippet for global stores. The instrumentation tool is invoked as a normal java program, giving as arguments the file to instrument and a text file containing the snippets to be inserted. Among the first things the parser do is to read the text file with the snippets, parse and classify them as the proper kind of snippet, i.e., integer load, floating-point load or store. They are now available for the parser to insert at the correct places. The layout of this text file is simple. First is declared what kind of snippet that is described, using the keywords IntLoad, FloatLoad or Store. Then the specified snippet is written. This is then repeated until all snippets are described. To separate the different parts the character # is used. An example of the layout is given below.

```

IntLoad

#

!Here the snippet is given as assembler

#

FloatLoad

#

!Here the snippet is given as assembler

#

Store

!Here the snippet is given as assembler

#

```

To allow for some further flexibility in the snippets, a group of special symbols are available for use in the snippets, in addition to ordinary assembler. A description of all these symbols is in Figure 8.

Finally, another thing that can be done is to prefix certain lines of codes with the character \* and a number. Then, depending on how some conditions are met, only those lines with one of

\$1, \$2, \$3: These symbols represent the three arguments of the instruction instrumented. As an example, the instruction: Id [%g1+128], %g5, will give \$1=%g1, \$2=128 and \$3=%g5.

\$I: This represents the instruction instrumented itself. That is, with arguments and all.

\$L: This symbol is replaced with an incremented digit, representing new labels inserted by the parser.

\$R: This either returns a free register found by the liveness analysis or spills (i.e., stores) a register to memory, and thereby making it available to use in the snippet, and after the snippet, loads the earlier value back into the register from memory.

\$F: Here the same thing as with \$R is done, with the exception that the registers now looked for are the floating-point condition code registers. That is %fcc0-3.

\$D: This symbol is replaced with the type of load that is instrumented, much like the \$I, but without the arguments.

**\$S:** The same as \$D above, but for stores instead.

Figure 8: A list of all the special characters available.

the specific numbers will be inserted into the code. This is an easy way to have a little bit more intelligent snippets. The conditions on which the choices are made have to be programmed into the tool itself and can not be changed afterwards without recompiling the tool. An example of a short snippet using this technique is written out below. In this snippet, depending on if it is a single or double floating-point load, it will be either a compare single (fcmps) or a compare double (fcmpd).

```

IntLoad

#

*1 fcmps $F, $3, $3

*2 fcmpd $F, $3, $3

fbne,pn $F, .LY$L

#

```

#### 4.5 Limitations

There are some new features to this new optimization tool compared to EEL. But obviously there are also many areas where we do not perform as well as EEL. The major thing is that while EEL can instrument all types of instructions, our tool can only instrument loads and stores. Also, another limitation that we have, and that EEL does not, is that for our tool to work we need to have the source code of the program we want to instrument. This means that we can not instrument all commercial programs. On the other hand when it comes to scientific programs, the source code is often available. Another thing is that at this stage of the development of the tool, it assumes that the compiler being used is Forte V6.2. For example it can not handle compiler output produced by GNU gcc. (On the other hand implementing support for this would not be a major task.)

Today, there has been no real testing of DSZOOM on a 64-bit system. Just taking DSZOOM, with snippets and everything, and move, would not work right now. This is because that at the moment we do use all the three application registers available in the SPARC V8 or V8plus ABI. But on SPARC V9 (64-bit) there are only two application registers. On the other hand, there is no reason why this should not work if we rewrote the snippets some. Actually, we can manage well with just two application registers. The only downside being that we might have to use some extra instructions in the snippets.

Another small limitation is that you have to change all the makefiles for the programs you would want to instrument. This can easily be avoided if the cc command was overload with the commands needed to perform the instrumentation.

# 5 Low-Level Optimization Techniques

Besides implementing the new instrumentation tool for use with the DSZOOM system, a number of other changes has been done to the original system. Among those are some new optimizations to the snippets as well as optimizations to the DSZOOM runtime-system. To show what has been done, first the snippets of the original proof-of-concept system are shown, and then the new snippets with some explanations to what has been changed and why.

#### 5.1 Proof-of-Concept Snippets

Here all the snippets used within the original DSZOOM system are shown. They have been rewritten in the syntax of the new instrumentation tool.

#### 5.1.1 Integer Load Snippets

The original snippet for integer loads is given here, written in the syntax of this new instrumentation tool. The purpose of this snippet is to first check whether or not the value loaded is correct, then if not, to check if it comes a global load and if it is, to call a C routine to handle the coherence.

```

!ORIG LOAD: 1d [%07 + 892], %00

%o7, $R

mov

%07, 892, %12 ! Obs!! if %12 == %07

add

ld

[%12], %00

%o0, 1, %g3

add

%q3, 0, %q3

srl

brnz,pn

%q3, .L1

nop

%12, 29, %g3

srl

sub

%g3, 4, %g3

%g3, .L1

brnz,pn

nop

DSZOOM mem load ! %o7 changes

call

! delay slot

mov

%12, %q3

ld

[%12], %00

sth

%g4, [%g3]

.L1:

nop

$R, %07

mov

```

The problem with this snippet is that it needs to have many free registers available, besides those available from compiling without the application registers. Those can sometimes be found with the help of liveness analysis, but far too often, especially in the heavily optimized programs, it is

hard to always find free registers. This leads to the need to spill registers on to the stack, which in turn slows down the program considerably.

#### 5.1.2 Floating-Point Load Snippets

Below the floating-point load snippet used by the proof-of-concept system can be seen. The purpose of this snippet is to handle floating-point loads in much the same way as integer loads are handled.

```

!ORIG LOAD: 1d [%07], %f7

%o7, $R

mov

%07, 892, %10 ! spill %07

[%07], %f7 ! ORIG_LOAD

add

ld

%fcc1, %f7, %f7

fcmps

fbe,pt

%fccl, .Ll

nop

srl

%10, 29, %g3

%g3, 4, %g3

sub

brnz,pn %g3, .L1

call DSZOOM_mem_load ! %o7 changes

%l0, %g3 ! delay slot

mov

ld

[%l0], %f7

sth

%q4, [%q3]

.L1

$R, %o7

mov

```

The main problem with this snippet is that it uses the register %fcc1. It is not always sure that this register is free for us to use. And if not, you have to spill it to memory, getting the same disadvantages as for the integer load snippet.

#### 5.1.3 Store Snippets

The third kind of snippet used is the store snippet. This snippet handles both integer and floatingpoint stores. How the original snippet looked is shown in Figure 9.

This snippet has, like the integer load snippet, to have at least two extra free registers available. As mentioned before this is seldom true and we have to spill to the stack.

#### 5.2 New Optimizations

First of all we used the snippets that was used earlier to show that instrumenting with the new tool gave the same result as before. When this was done, we pretty quick realized that the snippets used and some of the aspects of the runtime-system was not as fine tuned as possible. The changes we have implemented are described in detail below.

```

!ORIG_STORE: st %00, [%13 + 340]

%o7, $R

mov

add

%13, 340, %g3

! g3 = eff addr

srl

%g3, 29, %g4

sub %g4, 4, %g4

brnz,pn %g4, THIS_IS_LOCAL_ST

srl %~~~

srl

%g3, 6, %g4

%g3, 6, %g4

%hi(0x9b000000), %g3 ! g3 = %MTAG_ADDR_REG

sethi

%g4, %g4, %g4

add

add %g3, %g4, %g3

ldstub [%g3], %g4

brnz,pn %g4, 0x2a384

nop

ldub

[%g3 + 1], %g4

%g4, %g2, %g4

sub

sub

brz,pn

%g4, I_AM_IN_MSTATE

%g3, %g4

! g4 = %MTAG_ADDR REG

mov

%l3, 340, %g3

add

call

DSZOOM_mem_store ! %o7 changes

nop

I AM IN MSTATE:

st %00, [%g3]

! Orig ST

%g2, [%g4]

! Unlock MTAG

sth

ba,a END

THIS IS LOCAL ST:

! Orig ST

st

%o0, [%g3]

END:

$R, %o7

mov

```

Figure 9: The store snippet.

#### 5.2.1 Reducing the Number of Instructions and the MTAG Size

We noticed that when running programs compiled on the highest optimization level, the liveness analysis seldom found enough free registers for the old snippets. Since EEL could not be used on optimized code this problem was not found earlier, since in un-optimized code free registers were easy to find. This lead to us having to spill the contents of registers to memory. The effect of this was often two extra memory accesses in every snippet, a high price to pay.

The registers we had available, without having to spill, was the registers reserved for us by the compiler when we used the no%appl flag and the registers found by the liveness analysis. Since the second set of registers often were none, we had to rely heavily on the reserved registers, that is registers %g2, %g3 and %g4. Those three registers proved to be sufficient, if we rewrote the snippet in a smarter way. No actual changes to the way the snippet worked was done during this, only in the way which registers was used and when.

Another thing we also realized was that having one byte for directory and one byte for MTAG lead to more cache pollution than was necessary. Cache pollution is when we store a lot of our runtime-system things in the cache, thereby kicking out things put in the cache by the actual program. By changing the runtime-system so that one byte could keep both the bits for the directory as well as the MTAG we not only lowered cache pollution, but also was able to remove one load instruction from each store snippet.

At this point, we still had not done any changes to the behavior of the DSZOOM system. All we had done was to duplicate the things the proof-of-concept system did, but in a slightly more efficient and robust way.

#### 5.2.2 Straightening Out the Code

It is common that most of the code in the snippet will, in most cases, never be executed. It only takes up place in the instruction cache. Thus, the idea was to "take away" the part of the code that was not used for most of the time and in this manner produce a "straighter" execution path. By this we mean that it usually just continues and seldom has to branch to the code not so often used. This leads to less extra code having to be present in the instruction cache and therefore lowering cache pollution.

This was implemented so that we broke each snippet into two parts. For the integer load snippet it worked like this: The first of these parts just performed an access check. If it was correct it just continued. Since this in most of the cases is true we only have four extra instructions inserted for each load. But when this was not true the branch at the end of the snippet was taken to the other part of the snippet. In this part the range check and call to the coherence routine was executed. This other, not so often executed, part of the snippet was then placed at the end of the routine being instrumented. There all of the so called other parts of the snippets were placed together and only brought into the cache when needed.

The other snippets are divided into halves in the same way as the integer load snippet and only

the part that is most often executed is inserted next to the instrumented instruction. An example of how the integer load snippet looks is given in Figure 10.

```

IntLoad

#

!This is the fast path

!The code is placed next to the instrumented instruction

*1 add $1,$2,%g3

ŚΙ

and $3,255,%q4

sub %g4,255,%g4

brz,pn, %g4,.LY$L

*1 nop

*2 add $1,$2,%g3

.LQ$L:

#

IntLoad2

#

!This is the slow path

!The code is placed at the end of the procedure

.LYSL:

srl %g3,28,%g4

sub %q4,8,%q4

brnz,pt %g4,.LQ$L

nop

save %sp,-112,%sp

mov %y, %10

mov %g1,%l1

mov %ccr,%l2

mov %fprs, %13

mov %g5,%l5

call DSZOOM_mem_load_real!

mov %g3,%g6

mov %10,%y

mov %11,%g1

mov %12,%ccr

mov %13,%fprs

mov %15,%g5

restore

$D [%g6],$3

stb %g4,[%g3]

ba .LQ$L

nop

#

```

Figure 10: Here the two parts of the snippet for integer loads are given.

The more detailed results achieved by this kind of "straighter" code is given in section 6.3, where it is shown that this actually leads to improved execution time of the instrumented programs and that it in average gives a speedup of 5%.

#### 5.2.3 Removing Local Memory Accesses

It can be hard at instrumentation time to know what loads and stores are really global. If we do not know this there is a risk that we instrument even some local loads and stores and this

will lead to a bigger overhead than is necessary. The first and easiest thing that is done to avoid instrumenting some of those local loads and stores is to look at the arguments given to the instruction. The idea is to find loads and stores where there exists an argument that is a constant. Those can be found via the use of the instruction sethi. This instruction sets the highest 22 bits of a register to a constant. Then, using the register assigned and another constant, expressed via lo(some\_name), a load or store from a constant address can be done. The look of such an instruction is: LD [%g1+lo(num\_rows)], %g5. Therefore, choosing not to instrument loads or stores where the argument includes a register plus a lo construct, leads to avoiding some of the local memory accesses otherwise instrumented. This strategy has also been implemented in the instrumentation tool.

But this simple approach sometimes is not enough. When profiling all the programs used in the SPLASH-2 suite we found that for some of them we still instrumented a great number of local loads and stores. This obviously gives a larger overhead than necessary, since each instrumented load and store gives rise to extra instructions executed. For the programs that were worst at this there was a larger number of local loads/stores instrumented than global loads/stores.

Realizing this we now thought that we wanted to see how good our results would get if we could totally avoid instrumenting local memory accesses. (This could for example be done if you moved the instrumentation and did it in a compiler.) The way we could check this was to cheat some. First we ran the program with a special snippet that for each load or store called a subroutine in C that checked whether or not this was a global load/store by looking at the address given as argument. The routine then wrote both an unique ID given to this instruction as well as the information if it was global or not to an array specially allocated to store this. After the program was run, another routine wrote all the information stored in the array to a file called annotate\_data. Once this file exists the program is instrumented again, but this time given the annotate\_data file as an argument. The instrumentation tool then parsed this file into a HashTable. And now for every load and store we wanted to instrument we first looked in the HashTable to see if the instruction's ID was registered as a global or a local memory access. And the instrumentation was only done if it was only global. This way only instructions that were truly global were instrumented and no unnecessary overhead were present. The proof of the fact that none local instructions were instrumented was evident in the profiling output from a second run.

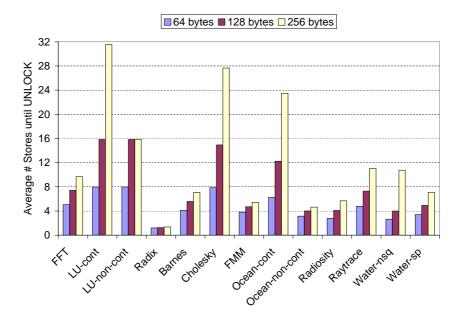

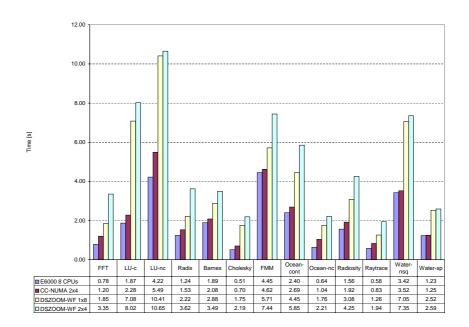

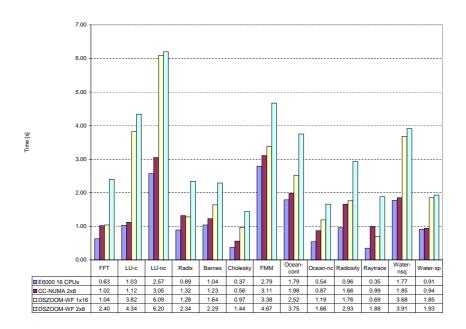

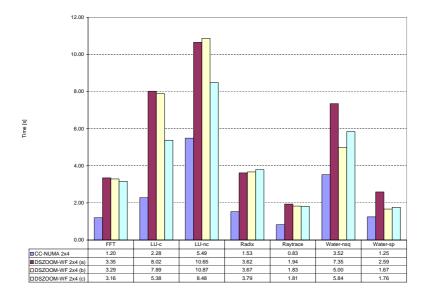

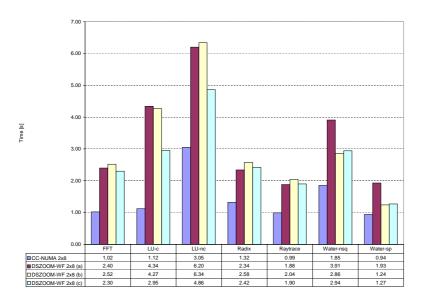

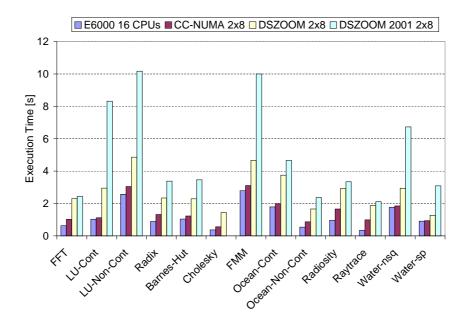

#### 5.2.4 Optimization of the Store Operations