# Validation of Cycle-Accurate CPU Simulators against Real Hardware

Master's Thesis, 3 October 2000

Sven Montán

Advisor & Examiner:

Jakob Engblom

Uppsala University/IAR Systems

Information Technology

Department of Computer Systems

Uppsala University, Sweden

## **Abstract**

One of the most important issues regarding real-time software performance is the worst case execution time (WCET). There are several methods for deducing the WCET statically; one such analysis system is currently under development by WCET researchers from Uppsala University in co-operation with Clab in Panderborn. The system uses a CPU simulator for calculating the execution time of selected parts of the target program, which creates a demand for a very cycle-accurate simulator.

In this thesis, we give a method for validating a CPU simulator against real hardware CPU. The proposed test method is a black-box test method that relies on hardware analysis for test-case generation. The validation method aims at both determining the accuracy of the simulator and to pinpoint simulator errors for improving the accuracy.

We have tested this validation method on a NEC V850 CPU core simulator, and the results show that the average error-rate drops from 11,2% to 1,3% for a set of benchmark programs.

## **Acknowledgements**

The author likes to thank Jakob Engblom, IAR Systems, Uppsala, for irreplaceable support during this work. Acknowledgements are also given the rest of the IAR staff for their help and fruitful comments. Special thanks to Eric Arbin for introduction to and support for the IAR tools and for help with the emulator installation and configuration.

The author also likes to thank IAR Systems for providing tools important to his work, such as the IAR Embedded Workbench (including the IAR C-Spy debugging tool) and the NEC V850E emulator.

## **Contents**

|    | Abstract2 |                                                   |    |  |  |  |

|----|-----------|---------------------------------------------------|----|--|--|--|

|    |           | edgements                                         |    |  |  |  |

| C  |           |                                                   |    |  |  |  |

| 1. |           | oduction and Background                           |    |  |  |  |

|    |           | WCET Analysis Tools                               |    |  |  |  |

|    | 1.2.      | Making a Cycle-accurate CPU Simulator             | .7 |  |  |  |

|    | 1.3.      | Why Formal Proofs is not an Option                | .8 |  |  |  |

|    | 1.4.      | Our Method of Validation                          | .8 |  |  |  |

|    | 1.5.      | Case Study on NEC V850E CPU Core Simulator        | .8 |  |  |  |

|    | 1.6.      | Method Evaluation and Results                     | .9 |  |  |  |

|    | 1.7.      | Paper                                             | .9 |  |  |  |

| 2. | Rela      | ted Work                                          | 10 |  |  |  |

|    | 2.1.      | Micro-benchmarking                                | 10 |  |  |  |

|    | 2.2.      | Testing WCET Analysis Results                     | 10 |  |  |  |

|    | 2.3.      | Performance Model Calibration.                    | 10 |  |  |  |

| 3. | Met       | hod Overview                                      | 12 |  |  |  |

|    | 3.1.      | Software Testing vs. CPU Simulator Validation     | 12 |  |  |  |

|    | 3.2.      | Method Restrictions on Hardware Complexity        | 12 |  |  |  |

|    | 3.2.1     |                                                   |    |  |  |  |

|    | 3.3.      | Execution Parameters                              | 13 |  |  |  |

|    | 3.4.      | Method Cookbook                                   | 13 |  |  |  |

|    | 3.4.1     | Hardware Analysis                                 | 13 |  |  |  |

|    | 3.4.2     | Reducing the Instruction Set                      | 14 |  |  |  |

|    | 3.4.3     |                                                   |    |  |  |  |

|    | 3.4.4     | Test Suite Structure                              | 14 |  |  |  |

|    | 3.4.5     | Test Code Patterns                                | 14 |  |  |  |

|    | 3.4.6     | Test Program Execution                            | 15 |  |  |  |

|    | 3.5.      | Measuring Execution Time                          | 15 |  |  |  |

|    | 3.5.1     | Problems when Comparing Measured Execution Times. | 15 |  |  |  |

| 4. | Ana       | lysis and Testing Tools                           | 17 |  |  |  |

|    | 4.1.      | The V850E User's Manual                           | 17 |  |  |  |

|    | 4.2.      | The Emulator                                      | 17 |  |  |  |

|    | 4.2.1     | Discussion on Emulator vs. Real Chip              | 18 |  |  |  |

|    | 4.3.      | Test Program Generator                            | 18 |  |  |  |

| 5. | V85       | 0E Pipeline Analysis2                             | 20 |  |  |  |

|    |           | V850E Pipeline Configuration                      |    |  |  |  |

|    |           | Instruction Prefetch                              |    |  |  |  |

|    |           | Parallel Instruction Execution (Dual issue)       |    |  |  |  |

|    |           | In-order Issue and Execution                      |    |  |  |  |

|    | 5.5.      | Pipeline Analysis Results                         |    |  |  |  |

| 6. | V85       | 0E Instruction Set Analysis                       |    |  |  |  |

|    | 6.1.      | Analysis of individual instructions               |    |  |  |  |

|    | 6.1.1     | T · · · · · · · · · · · · · · · · · · ·           |    |  |  |  |

|    | 6.1.2     |                                                   |    |  |  |  |

|    | 6.1.3     |                                                   |    |  |  |  |

|    | 6.1.4     | , ,                                               |    |  |  |  |

|    | 6.1.5     |                                                   |    |  |  |  |

|    | 6.1.6     |                                                   |    |  |  |  |

|    | 6.1.7     |                                                   |    |  |  |  |

|    | 6.1.8     | 1 2                                               | 26 |  |  |  |

|    | 6.1.9     |                                                   |    |  |  |  |

|    | 6.1.1     | 0 Bit manipulation instructions                   | 26 |  |  |  |

|    | 6.1.1     |                                                   |    |  |  |  |

|    | 6.1.1     | 2 CALLT and CTRET                                 | 27 |  |  |  |

|    | 6.1.1     |                                                   |    |  |  |  |

|    | 6.1.1     |                                                   |    |  |  |  |

|    | 6.1.1     | 5 PREPARE and DISPOSE                             | 28 |  |  |  |

| 6.1.1    | 6 HALT                                                               | 29 |

|----------|----------------------------------------------------------------------|----|

| 6.2.     | Analysis of Parallel Execution Scenarios (Dual Issue)                | 29 |

| 6.2.1    | Dual issue case 1: * / SLD                                           | 29 |

| 6.2.2    | Dual issue case 2: * / Boond                                         | 30 |

| 6.2.3    | Dual issue case 3: * / BR                                            | 30 |

| 6.2.4    | Dual issue case 4: MOV / *                                           | 30 |

| 6.3.     | Analysis of Instruction Execution Interference.                      | 30 |

| 6.3.1    | Single Issue Scenarios                                               | 31 |

| 6.3.2    | Dual Issue Scenarios                                                 | 32 |

| 6.4.     | The Equivalence Classes                                              | 34 |

| 7. Our   | Test Cases                                                           | 35 |

| 7.1.     | Test Case Families                                                   | 35 |

| 7.2.     | Test Code Patterns                                                   | 35 |

| 7.3.     | Improving Measurement and Comparison Accuracy                        | 36 |

| 8. Vali  | dation Test Results                                                  | 38 |

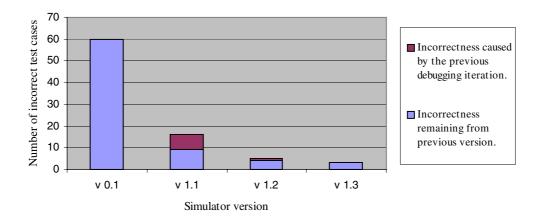

| 8.1.     | Validation and Debugging Iterations                                  | 38 |

| 8.1.1    | Omitted SLD Test Cases                                               | 39 |

| 8.2.     | Benchmark Evaluation of Simulator Improvement                        | 39 |

| 9. Con   | clusions                                                             | 42 |

| 10. Refe | rences                                                               | 43 |

| 11. App  | endix A                                                              | 44 |

| 11.1.    | Test Case Specifications                                             | 44 |

| 11.2.    | Test Programs of Test Case F0_1                                      |    |

| 12. App  | endix B                                                              | 65 |

| 12.1.    | List of the Execution Parameters                                     | 65 |

| 12.2.    | List of Dual Issue Scenario                                          | 65 |

| 12.3.    | Table B-1: Dual issue Classification (EP14)                          | 66 |

| 12.4.    | Table B-2: 16-bit Instructions with Constant Timing Behaviour        | 67 |

| 12.5.    | Table B-3: 32 and 48-bit Instructions with Constant Timing Behaviour |    |

| 12.6.    | Table B-4: Instructions with Operand Dependent Timing Behaviour      | 69 |

| 12.7.    | Table B-5: Selected Instructions                                     | 70 |

## 1. Introduction and Background

## 1.1. WCET Analysis Tools

One of the most crucial aspects of real-time software programming and testing is the determine ration of software performance. One of the most important issues regarding software performance is the estimated *worst case execution time* (WCET). The WCET is required for system modelling and verification, scheduling analysis, hardware dimensioning, etc.

Real-time software developers currently have few options for investigating performance issues such as the WCET. The industrial standard of today is to spend substantial time, perhaps hundreds of hours, running software on real hardware and measuring execution times. This problem becomes even more obvious for embedded system developers, since the applications sometimes must be burned into ROM before performance can be tested.

An estimated WCET must be safe, i.e. it must never underestimate the real value of the WCET. Using measurements for estimating the WCET can never produce a safe WCET since there is no guarantees that the real worst case scenario as been captured by the measurements. A safe estimated WCET can only be produced be formal static analysis.

The need for tools performing static WCET analysis is evident, but still very few such tools have been developed and deployed. However, one research tool for WCET analysis is the Uppsala/Paderborn Generic WCET Analysis Tool [1] currently under development by WCET researchers from Uppsala University in co-operation with C-lab in Panderborn, Germany. This analysis tool performs both advanced high-level and low-level program flow analyses to deduce the worst-case execution time scenario for a given target program. The selected parts of the target program are then run in a cycle-correct CPU simulator and the final execution timing is obtained. This means that the analysis tool is critically dependent on a correct simulator to generate safe times.

## 1.2. Making a Cycle-accurate CPU Simulator

Designing and implementing a cycle correct CPU simulator is a very difficult task. The main obstacle is probably to obtain correct and detailed CPU specifications. Such specifications are often derived directly from the CPU hardware documentation, written by the CPU manufacturer. There are several sources of errors in such a process:

- Documentation is too superficial. The simulator programmer is then forced to make assumptions about the CPU internal functionality and design.

- Real CPU implementation does not correspond to the documentation on some significant details.

Such divergences can arise from inconsistent documentation during CPU development or even simple typing errors.

The simulator specifications then become very unreliable, possibly leading to a bad simulator design. Important internal states and functions of the CPU may be modelled incorrectly or even completely omitted due to a poor abstraction.

A CPU simulator is also a complex piece of software, hence the presence of implementation bugs are probably unavoidable. Such bugs may cause the simulator to render a significantly wrong execution time result for some target programs (while others may be totally unaffected by the bugs).

These issues are only some of the problem simulator vendors must face and they clearly illustrate the need for systematic methods of simulator debugging and validation.

## 1.3. Why Formal Proofs is not an Option

A CPU simulator can be viewed as just another software program. The target hardware architecture, which the simulator is supposed to imitate, may be specified and documented using a formal hardware description language such as *VHDL* or *Verilog*. This might indicate that formal proofs could be used as validation method framework. However, we consider validation by formal proofs as an infeasible strategy. Some problems of using formal proofs in this case are:

- Insufficient specifications

- High complexity of the software, beyond current technologies

Lack of knowledge of how the architecture is implemented inside the actual hardware will certainly cause CPU simulator vendors to design and implement incorrect performance models without violating any formal specification. Formal proofs may very well be used to validate other parts of a WCET analysis tool, but in the case of simulators the gap between theoretical models and reality (physical target chip) would remain unexplored.

We believe that simulator validation by comparing the simulator to real hardware is probably the only solution to achieve an adequate validation, at least in the foreseeable future.

#### 1.4. Our Method of Validation

In this thesis we present our work on finding a systematic method for CPU simulator validation. The fundamental idea is to perform *black-box testing* in which performance results from running tests on the CPU simulator are compared to the results of the same tests on real hardware.

Each single test is a simple micro-benchmark program, which includes a short hand-written test code pattern, which is timed. The set of code patterns is derived from characteristics of the simulation target hardware architecture and aims at covering as many execution scenarios as possible. Every test code is run on real hardware and the execution times are measured. These results act as validation references and are compared to execution times calculated by the CPU simulator. Divergences indicate simulator errors and the need to correct the simulator.

The basic ideas behind this method of validation are not new. They have been proposed and tested earlier in the work by Black and Shen [2]. Their method aimed at validation of a performance model, using comparison tests between the model and the real hardware. The test suite contained unbiased test cases, as well as random and hand-written test codes. Nevertheless, some key assumptions let us take a slightly different approach, especially on test code pattern generation:

- Our method aims at CPU simulators for microcontroller chips with fairly simple architectures.

- We limit our performance parameters to only include execution time with respect to pipeline execution.

- We do not invoke other performance issues such as cache miss rates, speed of memory accesses

etc. This also let us use a simplified memory interface model, letting us assume static and wellknown timing for every single memory access.

With these restrictions on hardware complexity we believe that systematic and careful static analysis of hardware architecture can reveal the information needed to generate a complete test suite. This means that no random test cases or other unbiased tests with "ultimate covering" ambitions are necessary to establish an adequate validation test suite.

## 1.5. Case Study on NEC V850E CPU Core Simulator

We have performed a case study to investigate if such a validation method works in practice. The NEC V850E 32-bit microcontroller CPU core [6] has been used as hardware target and validation reference. The V850E CPU architecture features simple RISC instructions together with more complex instructions that are specially adapted to embedded system requirements, making it a fairly typical embedded microcontroller.

The V850E pipeline model is rather straightforward but not trivial, since it offers parallel execution of two instructions under certain conditions. The presence of on-board internal ROM and RAM and the absence of caches correspond well with our limitations on memory access.

Our subject to validation test case, the Uppsala/Paderborn V850E CPU Simulator prototype, has originally been based only on written documentation from NEC. Earlier tests [3] of this simulator have shown that the simulator may miscalculate execution time with up to 25 % for some benchmark programs and 11,2 % in average.

Ideally, we would like a perfect correspondence, which is probably not feasible for any non-trivial architecture. For use in static WCET analysis, the CPU simulator must be very close to the hardware but a small divergence can be tolerated if it is bounded. A safety margin may then be added to the WCET to account for such divergence, yielding a safe estimate that is slightly loose.

#### 1.6. Method Evaluation and Results

By comparing results for some benchmark programs before and after debugging the simulator, we are able to estimate how well our method expose simulator incorrectness. The relative improvements of simulator accuracy for these benchmarks act as a measurement on effectiveness of our method.

The results from these benchmark comparison tests show that the average simulator error has dropped from 11,2 to 1,3 % after applying our method to the simulator. These results indicate that our method may be a feasible strategy for debugging and validation of a CPU simulator.

## 1.7. Paper

Our work is presented as following:

- Related works are presented in chapter 2.

- In chapter 3 we give an overview of our method. Since we invoke testing, we discuss and define test data adequacy criteria. A method cookbook is also presented in this chapter.

- The analysis and test tools used in our case study are introduced in chapter 4.

- Chapter 5 covers the analysis of the V50E CPU pipeline, while the instruction set is analysed in chapter 6

- The structure and design of our test suite is given in chapter 7, and the validation test results are presented in chapter 8. This chapter also includes the results from the method evaluation.

## 2. Related Work

## 2.1. Micro-benchmarking

While larger benchmarks are often used with the intention of testing computer system performance under real workloads, micro benchmark aims at measuring specific features of a system. This use of micro benchmark is introduced by Saavedra, Gaines, and Carlton [4], which use micro benchmarks to extensively analyse memory performance of the KSR1 parallel computer.

## 2.2. Testing WCET Analysis Results

An interesting method of testing the correctness of the result calculated by static WCET analysis is presented by Puschner and Nossal [5]. This method is based on comparison between the result produced by the WCET analysis tool and the result from measuring execution time on real hardware. The test programs are generated automatically using a *generic algorithm* (*GA*). The generated programs are based on the results of previous test results.

This method shares the property of using comparison tests as main framework with our method. On the other hand, Pushner and Nossal test the entire WCET analyse tool, while our method narrows on testing a CPU simulator. Their main interest is in testing the dependence of input data and associated variances in program flow, and not on low-level CPU issues.

#### 2.3. Performance Model Calibration

Black and Shen propose a method of Performance Model Calibration [2], very closely related to our method. In this method a set of test code patterns are generated, each test code is run on real hardware and the execution times are measured. The performance model also calculates execution times for every test code and the results are compared. After analysing the comparison outcome, the model is debugged and the tests and comparisons are repeated.

The test code set is divided into five test suites; *Alpha, Beta* and *Gamma* test suites contains unbiased tests where each and every assembler instruction is executed individually and in combination with both the same instruction and all other instructions. Several randomised code sequences form the *Random* test suite. Finally, *hand-written* code patterns are used to trigger special hardware functionality and to check model boundary conditions.

By running a similar comparison test with large benchmarks after every debugging phase, the effectiveness at improving model accuracy can be verified.

Since the results presented on effectiveness show a much lower degree of accuracy improvement than expected by the authors, this may indicate that the proposed method is insufficient. However, Black and Shen claim in their final analysis that a larger and more advanced test suite would render an acceptable validation.

One principal point in Black and Shen's method is of course how the test suites are compiled. The Alpha, Beta and Gamma tests together with random test suite are generated automatically, using only basic information on target instruction set. We assume that no prior analysis is needed for this work. However, the special hand-written patterns require an thorough analysis of hardware, instruction set etc, in order to find as many interesting cases as possible.

In our work we have used an approach very similar to the method proposed by Black and Shen. We have adopted the basic idea of a comparison test, invoking a proper test suite, between a simulator and real hardware as the validation method framework. We have also used comparison tests on larger benchmark for evaluating the effectiveness and correctness of our method.

The main difference between Black and Shen's method and ours is the test suite generation. Our test code patterns are all hand-written based on prior analysis of the hardware architecture. No unbiased tests such as Alpha, Beta, Gamma or random tests are included in our test suite.

## 3. Method Overview

In this chapter, we discuss CPU simulator validation in terms of white-box and black-box testing.

We discuss method restrictions on hardware complexity, and a method cookbook is presented. We conclude by defining some problems regarding comparison of measured execution times.

## 3.1. Software Testing vs. CPU Simulator Validation

CPU simulator validation based on testing against real hardware share many properties with general software testing. Software testing normally involves careful analysis of the software implementation. This includes analysis of the code statements and search for possible execution paths. To reach the best possible test coverage, test criteria such as "execute each statement at least once" or "evaluate each branching structure with all possible values" is stated. This is known as structural or white-box testing, since tests primary derive from knowledge of the software's structure and how the program is implemented.

Another form of software testing is functional or black-box testing. Functional testing means that the test cases are derived only from software specifications and the test results are given by analysing input and corresponding output. Only input and output domains are analysed and classified in order to find the best test data adequacy criteria.

CPU simulator validation by testing against real hardware is very similar to software black-box testing. The simulator program is not analysed in any way and the validation result only depends on simulator input and output. In this case, the input is some assembler instruction sequence and output is the total execution time of this instruction sequence.

Since validation is based on comparison, we consider there to be only one fundamental definition of simulator correctness - the simulator should always agree on execution times (output) with real hardware for any arbitrary instruction sequence (input).

To be able to handle this infinite input set, demands for CPU hardware analysis are more or less unavoidable. Strive for optimal test coverage may also require that every relevant internal state of the simulated CPU be reached during some execution scenario. This implies a profound hardware analysis not unlike the analyses performed in white-box testing. However, if the hardware architecture is too complex, the analysis will certainly fail and other test coverage strategies are required (e.g. unbiased tests may be used).

Our method of simulator validation adopts the idea of black-box testing as the fundamental testing discipline, augmented with a white-box analysis of the hardware. We define *test data adequacy criteria* to quantify our goal of test coverage. These criteria are derived from the simulator-input domain, i.e. sequences of assembler instructions.

The final test suite composition is solely based on results from structured analyses of the real hardware architecture. Hence no unbiased or random test cases are required in our method.

## 3.2. Method Restrictions on Hardware Complexity

Constraints on hardware complexity are crucial for our method to work in practice. Hence, we have been forced to make some initial restrictions and assumptions before we started our investigation of the V850E hardware.

The memory interface model has been limited to only concern V850E on-chip RAM and ROM. These memories are accessed on independent memory buses and thus no conflicts between data and instruction accesses should ever occur.

The internal ROM holds all instructions and all memory access are completed within a single clock cycle during instruction fetch. Data memory accessing instructions normally access internal RAM only. Such accesses are also completed in a single clock cycle. The V850E instruction set includes two instructions that read data from internal ROM. This exceptional behaviour and its impact on execution timing is explored and analysed as a special case.

The above constraints narrow our analyses and tests to only include the instruction set and the execution environment, i.e. the CPU pipeline.

#### 3.2.1 Case Study Validation Reference Machine

Our method requires the ability to measure execution time on real hardware. Due to limitations in time and available equipment, we have not been able to perform such measurement on a real V850E microcontroller chip. Instead we have used a NEC V850E CPU core emulator as validation reference. The use of an emulator is of course a potential source of error since we depend on the timing accuracy of this emulator. Nevertheless, we do not believe that this has any major effects upon our proposed method. The emulator is developed by real chip manufacture NEC, and they claim to use the same core logic in the microcontroller and the emulator. This also means that even if we have used an emulator in our case study we do not believe that our method is restricted by this fact.

Overall performance monitoring has been limited to a cycle clock counter, due to lack of dedicated hardware counters. This has been quite sufficient since our method disregards performance impacts of the external memory interface, cache etc.

#### 3.3. Execution Parameters

Instead of considering single instructions to be atomic units, we are interested in invoking instructions based on their execution characteristics, e.g. what pipeline resources they use and how they utilise these resources. By analysing the instruction set, we can find these *execution parameters* (EP), and we can also, for each instruction assign *values* to all execution parameters. This means that each instruction can be associated with a *set of tuples* (EP, value). We will use these sets to find a *reduced instruction set*, which will be the set of instructions we use in our test cases.

The execution environment, i.e. the pipeline and instruction fetch mechanisms, may also have specific execution parameters. An example of scenarios where such execution parameter have impact on overall execution times may be situations where the instruction fetch mechanism fail to fetch an entire instruction due to some memory alignment constraint. These execution parameters must of course be identified in order to reach adequate test coverage.

## 3.4. Method Cookbook

We have tried to formalise our basic ideas into a validation method cookbook. Each step is described in more details below.

#### 3.4.1 Hardware Analysis

The purpose of hardware architecture analysis is to:

- Identify and classify as many significant execution parameters of the architecture as possible.

- For each instruction, determine the values of the execution parameters of instructions.

- Examine how and under which condition instructions interfere with each other during execution.

This analysis includes examining if (and under which conditions) instructions can interfere directly

with the third or the forth succeeding instruction without interfering with the intervening

instructions.

This requires a deep and structured investigation of the instruction set and pipeline design. It is very hard to give details on what to examine before the actual analysis is commenced, since it is extremely hardware-specific.

The first step will be to analyse the pipeline design, identifying pipeline stages and possible datapaths. Attention must also be paid to how instructions are fetched from instruction memory and under which conditions this may cause pipeline delays.

The next step is to analyse the instruction set, and for each instruction and instruction variant:

- Determine which actions the instruction performs during its execution.

- Match these actions to execution resources, i.e. pipeline stages.

- Analyse any potentially instruction interference scenarios.

Any action that may be suspected to have impact on execution timing is denoted as an execution parameter, and the execution parameter value is determined for each instruction. Note that this is also necessary when designing a cycle-accurate simulator.

#### 3.4.2 Reducing the Instruction Set

To reduce the number of instructions, each instruction or instruction variant is classified regarding its associated set of (EP, value)-tuples. Instructions with the same sets are grouped together into an *equivalence class*.

As a final step, a representative instruction from each equivalence class is selected. These instructions constitute a reduced instruction set, which is used for test code generation.

#### 3.4.3 Test Data Adequacy Criteria

After reduction of the instruction set, each remaining instruction will have a unique set of (EP, value) - tuples. From the instruction set analysis, we know the conditions for instruction interference. From the execution environment (pipeline) analysis, we know the conditions for execution delays caused by the execution environment EP's.

We can now define the test data adequacy criteria for our method as following:

- 1) Each instruction of the reduced instruction set should be tested when:

- a) The instruction interferes with succeeding instructions (interference conditions satisfied).

- b) The instruction does not interfere with succeeding instructions (interference conditions not satisfied).

- 2) The test suite should also include test cases where:

- Execution environment EP has impact on the execution time of the test case (condition satisfied).

- b) Execution environment EP has no impact on the execution time of the test case (condition not satisfied).

#### 3.4.4 Test Suite Structure

The test suite is divided into several specialised *test case families*, where each family is targeting closely related instructions. Individual test suite families may be derived from:

- "Natural" instruction relations, e.g. a family focusing solely on division instructions.

- Instructions with closely similar sets of (EP, value)-tuples, e.g. "simple" arithmetic instructions.

- Special execution paths such as parallel execution etc.

#### 3.4.5 Test Code Patterns

A test case family consists of a set of short hand-written code patterns. The intention is that each pattern will exercise and reveal the impact of a single or at most a few execution parameters of a target

instruction. Thus, each test case should act as a precise error indicator when it comes to debugging the CPU simulator.

The results from the analysis phase will serve as general guidelines for code pattern generation. We assume that each target instruction has some kind of "basic" execution behaviour inside the pipeline, e.g. a simple arithmetic instruction is pipelined perfectly, while a jump instruction cause a static pipeline delay of two clock cycles. Such execution scenarios are easy to find since they are common and also probably well documented. We must, however, write patterns where every unique scenario win which target instructions interfere with adjacent instruction in such a way that additional execution delays may occur. Patterns where no instruction interference is expected, and hence not triggering abnormal execution behaviours, must of course also be included. This improves coverage and helps interpreting test results with respect to simulator debugging.

The code patterns are very short instruction sequences. To be able to measure the execution times distinctly, each pattern must be repeated at least a couple of hundreds of times within each test run. Hence, execution behaviour when a pattern is repeated must be taken into account when designing the code patterns. In most cases, a "neutral" transition between repetitions is desired. In other cases, e.g. patterns with only a single instruction, pattern transition will be most significant to overall execution time.

Another important issue to address, especially with respect to pattern repetition and transition, is that every code pattern must be fully executable on real hardware. Instructions can't be allowed manipulate the contents of registers in such way that succeeding instructions may fail or cause undesired events, e.g. division by zero or overflow.

#### 3.4.6 Test Program Execution

Each test code pattern is repeated and transformed into two equal test programs, one for the CPU simulator and one for the reference machine (real CPU hardware). Some kind of code generation tool should be used to avoid small but devastating divergences between corresponding test programs, e.g. input to simulator is a sequence of one thousand ADD instructions, while real hardware code only incorporates 998 ADD's.

Every test program is executed on the reference machine and the execution time is measured. These values act as validation references; thus these programs need only be executed and measured once. Corresponding test programs are then given to the CPU simulator and the execution times, calculated by the simulator, are compared to the validation reference values. If any divergences are detected, the simulator must be corrected and the tests repeated until all divergences are eliminated.

## 3.5. Measuring Execution Time

Measuring execution time on real hardware is often very difficult. Interference of unknown or nondeterministic factors may cause large variances on test code execution time. Arriving at accuracy of a few clock cycles require a stable, deterministic and predictable test bed.

In our case study, we have used a V850E emulator as hardware reference machine. This means that we have not been forced to face the more practical difficulties arising when measuring execution time directly on the real CPU chip, and no such problems will be discussed in this thesis.

We have assumed the emulator to be stable and deterministic. All our experience with the emulator supports this assumption. Even though some emulator results have been most surprising, they always have been repeatable. The emulator is presented and discussed in more detail in the next chapter.

#### 3.5.1 Problems when Comparing Measured Execution Times.

There are some important issues regarding measuring and comparing execution time that need to be addressed. Since we want to compare the execution time result given by the simulator to the result

given by the emulator, we must ensure that the simulator and the emulator agree on what to measure, in other words:

- When should the measuring start?

- When should it be stopped?

Since we assume that the simulator and emulator are deterministic, measuring must start when the simulator and the emulator are in some equivalent, initial state. Such a "zero" -state could, as an example, be defined as a *cold pipeline* i.e. every resource inside the pipeline is free and empty, including instruction prefetch mechanisms and prefetch instruction queue. This is probably the most natural initial state for the simulator.

Unfortunately, a cold pipeline state is most likely unreachable for the emulator, and definitely unreachable if we should measure on real CPU chip. This requires us to use a *warm pipeline* as initial state i.e. there are already some instructions executing inside the pipeline when first instruction of the test code is fetched and measuring is started. This means those internal states of the emulator and the simulator must be well controlled before the test code initiate execution. In our case, we must be sure that no instructions with "nasty" execution behaviours immediately precede our test code and thereby cause unexpected or uncontrolled execution delays.

Defining the point where measuring should stop is even more difficult. It is very hard to determine at which point in time the last instruction of the test code terminates, especially if this instruction has very long individual execution time e.g. loops in some pipeline stage. The problem is to "synchronise" this point in time, if we decide to stop the emulator measuring clock when the final instruction is being fetched from instruction memory, will the simulator do the same?

Our solution to these problems is presented in chapter 7: Our Test Cases.

## 4. Analysis and Testing Tools

Our analyses have been performed through studying and interpreting the hardware documentation, and through testing and verifying this information on a hardware emulator. This chapter describes and discusses the documentation used. It also includes a brief description of the emulator and its interface. We conclude with a discussion on emulator versus real hardware chip.

#### 4.1. The V850E User's Manual

All V850E documentation used and referred in the following chapters is taken from the NEC V850/MS1 Preliminary User's Manual (UM)[6]. The essential information has been taken from following sections:

- 5.3 Instruction Set. This section includes syntactic and semantic descriptions of each instruction.

- 5.4 *Number of Instruction Execution Clock Cycles*. Includes Table 5-10, which gives some interesting information on instruction interference.

- 8, 8.1, 8.2 *Pipeline*. Include figures of general pipeline configuration and dual issue scenario.

- 8.3 *Pipeline Flow during Execution of Instructions*. Includes Execution Flow Diagrams (EFD) for each type of instruction. Also includes table of memory access timings.

Relying solely on hardware documentation may not be sufficient in order to find all relevant facts about the hardware architecture. Even documentation that can be considered unusually detailed, such as the V850E documentation, may be confusing and easy to misinterpret. During our work we have encountered ambiguous information and even some completely wrong specifications in the User's Manual. All such cases are described in this paper.

#### 4.2. The Emulator

In order to get a better understanding of the CPU, we have used a V850E Core Emulator for testing and clarifying execution behaviours whenever needed.

The emulator is programmed and monitored via the IAR V850 C-Spy debugging software [7]. This application includes monitoring of CPU registers, as well as clock cycle counter and execution trace logs. Trace logs show each executed instruction marked with a clock cycle timestamp, indicating execution time in relation to adjacent instructions.

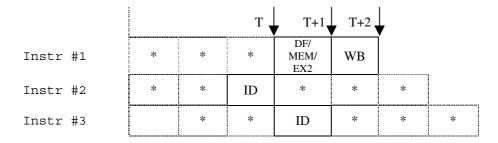

Example: A sequence of instructions with "perfect" pipeline behaviour, e.g. unrelated addition instructions, will render timestamps C, C+1, C+2 and so on. C is the timestamp value for first instruction in the sequence.

It is not always clear how the timestamps should be interpreted. We do not know which execution event sets the value of a timestamp, e.g. execution in some specific pipeline stage, or if timestamps are deduced in some other way. Hence, timestamps only show if a delay has occurred but not why or in which pipeline stage. Whenever the trace log indicates such a delay or other unusual execution timings, documentation has been consulted for clarification, and vice versa.

Figure 4-1 shows the user interface of C-Spy, running an emulator session.

To some extent, the emulator has also been used for verification of rather trivial information, gathered from V850E User's Manual. This has been very enlightening and helped us to reason about the pipeline design and implementation. In general, having an emulator with good control software is a very valuable tool for simulator validation.

Figure 4-1: User interface of IAR C-Spy[7].

#### 4.2.1 Discussion on Emulator vs. Real Chip

Considering that we used the emulator for verifying and clarifying information found in the chip documentation, questions on emulator accuracy are inevitable. We have not been able to experiment with real hardware chip during our work, thus we have no way to measure or quantify any potential incorrectness of the emulator. To handle the gap between emulator and real hardware chip, we have made the following assumption: *The emulator is always accurate and corresponds correctly to the real hardware.*

This means that whenever we encountered divergence between documentation and emulator, we have considered the information given by the emulator as correct.

Nevertheless, some test scenarios have been found in which execution results presented by the emulator are very strange and inexplicable. We have denoted these cases as "remarkable" throughout this paper. In order to maintain consistency on our emulator assumption, we have chosen to include them as relevant criteria for our final test code generation. We do not know if these exceptions indicate an incorrect emulator or an accurate emulator, emulating a real chip with odd design and undocumented features (or even bugs, which is quite common even in hardware design and implementations).

## 4.3. Test Program Generator

Each test code pattern has been derived and specified manually but the pattern specifications were translated into final test programs by a simple code-generating program (written in SML).

Since emulator programs must be fully executable, they include instruction sequences for initiating data memory and registers. Execution time for this overhead is avoided by letting dedicated instructions trigger the clock-cycle counters. The memory address of every instruction must be kept

synchronised with the corresponding simulator program so that no uncontrolled misalignment scenarios occur during execution, and thus the emulator code is loaded to the same address as the simulator uses.

Due to the design of the simulator, simulator test programs must be structured into basic block. Within a basic block, each individual instruction is encoded together with its memory address [8]. Each code pattern instance is translated into a basic block when the pattern ends with a branching instruction. Otherwise, all pattern instances can be aggregated into one large basic block. Test code wrapping sequences are always encoded into separate start and end blocks. The simulator also needs a description of the basic block execution order. This file is also produced by the code generator.

An example of equivalent emulator and simulator programs is in Appendix A: Test Programs of Test Case F0\_1.

Most patterns have been designed so that the total execution time for the final test programs can be expected as multiples of the number of pattern instances when executed on the emulator i.e. we can ascribe a certain number of cycles to each iteration of the pattern.

Exceptions are misalignment test programs, which are designed to trigger a misalignment scenario every other pattern instances. This design is chosen since it allows start address 0x2000 to be used for all test programs.

## 5. V850E Pipeline Analysis

The first step in our analyses involves a closer look at the instruction execution environment and its characteristics. All information is gathered from the V850E User's Manual. This chapter gives a brief overview of the NEC V850E pipeline configuration. This also includes

descriptions and discussion on parallel execution, so called dual issue scenarios.

## 5.1. V850E Pipeline Configuration

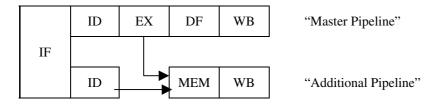

Unlike earlier models of V850 family, the V850E CPU core features both a five-stage Master Pipeline and a special four-stage pipeline dedicated for short load (short address mode) and branch instructions. In this Additional Pipeline, address calculation is performed during instruction decode stage (ID), thus no executing stage (EX) is required.

The normal data path of the Master Pipeline is split after EX. Instructions that do not access memory, such as arithmetic and logic instructions, utilise the "original" data path. Execution is then transferred by a data forwarding stage (DF) to final write back stage (WB).

Memory accessing instructions use the memory stage (MEM) and WB of the Additional Pipeline. Thus a non-blocking behaviour of memory accessing instruction is achieved. We will however not be able to investigate and test this option since data memory accesses are completed in a single clock cycle in all our test configurations.

The instruction fetch stage (IF) is shared by the Master and the Additional Pipeline. IF is designed to process at most 32 bits of instruction data per clock cycle. This implies that instructions longer than 32 bits should always cause some pipeline delay.

Figure 5-1. The V850E Pipeline Configuration [6]

#### 5.2. Instruction Prefetch

Before instructions are processed in IF they have to be fetched from instruction memory. This is performed by a dedicated Prefetch Unit, which reads four consecutive bytes from instruction memory, always from a 32-bit aligned address. If only the first 16 bits can be processed by IF, e.g. first two bytes are a 16-bit instruction and remaining two bytes are first half of a following 32-bit instruction, then remaining two bytes are stored in an instruction buffer queue.

## 5.3. Parallel Instruction Execution (Dual issue)

Dual pipelines with independent data paths also bring the possibility of two instructions executing simultaneously. Assuming that IF holds two 16-bit instructions which together constitute a possible dual issue pair, and that preceding instructions have not caused the pipelines to stall, then both instructions can be issued together during next clock cycle.

Dual issue scenarios may have a significant impact on the execution time of programs and instruction sequences. Typically, a suitable sequence of dual-issued 16 bit instructions have a CPI as low as 0.5,

while a sequence of 32-bit instruction never can reach below 1.0 CPI. This improvement raises the performance of the CPU by at least 10 %, sometimes as high as up to 30 %.

#### 5.4. In-order Issue and Execution

The older members of the V850 family implemented a strict in-order issuing policy for instruction execution. This regulates the order in which instructions are allowed to access resources of the pipeline. Interlock mechanisms allows instructions with very long execution times or "messy" pipeline behaviour, e.g. divide or bit manipulation instructions, to stall the pipeline while they execute. Succeeding instructions are never allowed to overtake executing instructions at any point.

The V850E core has inherited this pipeline policy but the introduction of parallel pipelines with dual issue has made several execution scenarios more complex and harder to predict. For instance, a dual issue scenario implies that the logical issuing order between two instructions is arbitrary. Consecutive instructions can also utilise different pipelines during execution. This may require other types of interlocking and control mechanisms than found in the V850 core.

## 5.5. Pipeline Analysis Results

Instruction length is clearly significant for instruction fetch timing as well as the possibility for 16-bit instructions to participate in dual issue scenarios. This is an indication of an individual instruction parameter and we investigate this in more detail during instruction set analysis, presented in the next chapter.

However, we have one execution parameter that depends on the execution environment itself. Assume a branch instruction is causing the instruction buffer queue to be invalidated and that branch destination instruction is 32 bits and misaligned, i.e. least significant address byte: 0x02, 0x06, 0x0A or 0x0E. Since the prefetch unit follows a strict word alignment policy when reading instruction data, prefetch will then need an extra read-cycle since only first half of the instruction is read during the first clock cycle. This will then cause an execution delay of one clock cycle.

A similar delay will occur when a branch destination instruction, also misaligned, constitutes the first 16-bit instruction of a dual issue pair. These two 16-bit instructions will not be issued together since they do not execute in IF during the one and same clock cycle.

This discovered execution parameter is denoted EP0. Since it is not a parameter of individual instruction, we can not use it for instruction classification. However, our test suite must include misalignment scenarios where this behaviour is triggered and tested.

□ EP0: Instruction prefetch misalignment after changed program execution flow.

## 6. V850E Instruction Set Analysis

This chapter gives our execution analysis of the V850E instruction set. The analysis aims at finding:

- Execution parameters (EP) of instructions and instruction variant. Execution parameters with assigned values are later used for equivalence classification and instruction set reduction. Discovered execution parameter are shown as:

- □ EP<no>: <description> (<value range>)

- Interesting execution scenarios. We are especially interested in finding scenarios where instruction interference may cause additional execution delays. We also want to find all possible dual issue scenarios. This is not trivial since the V850E documentation does not specify such scenarios at all.

- The "propagation" of instruction interference, i.e. assuming an instruction sequence of instructions A, B, and C, can there be scenarios where instruction A does not interfere directly with its successor B, but instead interfere directly with next instruction C? This is important to investigate since we want our test code patterns to be as short and as few as possible, yet including all kinds of instruction interference scenarios.

The instructions are already grouped in the V850E User's Manual [6], regarding their type and execution behaviour. We have used this basic classification for structuring our analyses.

During pipeline configuration analysis, we already found that instruction length is a significant execution parameter. The V850E instruction set includes instruction of length: 16, 32, 48, and 64 bits. The majority is 16 and 32 bits, the only exceptions are 48-bit MOVimm32 together with the 48 and 64 bit PREPARE variants.

□ EP1: Instruction length. (16/32/48/64)

## 6.1. Analysis of individual instructions

Our basic strategy has been to begin by analysing the simplest instructions, how they execute in the pipeline and how they interfere with each other. With "simplest" we mean an instruction with relatively well-known and easily understood executing behaviour, for example the 32-bit "addition with immediate" instruction (ADDI). We then move on to load/store instructions, branch/jump instructions, instructions with pipeline loops, and so on.

#### 6.1.1 No operation instruction

Analysed instruction: NOP

The simplest instruction is NOP. NOP does not do anything, and thus no execution parameters are found. The Execution Flow Diagram (EFD) of the User's Manual shows execution only in the IF and the ID stage. These are probably the stages of Master Pipeline; the EFD's are not always clear on which pipeline is used.

#### 6.1.2 Arithmetic and logical instructions

Analysed instructions: MOV, MOVEA, MOVHI, ADD, ADDI, CMP, SUB, SUBR, SETF, SASF, CMOV,

${\tt ZXB,\,ZXH,\,SXB,\,SXH,\,BSH,\,BSW,\,HSW,\,NOT,\,OR,\,ORI,\,XOR,\,XORI,\,AND,}$

ANDI, TST, SHR, SAR, SHL, SATADD, SATSUB, SATSUBI, and

SATSUBR

Includes 16 and 32-bit arithmetic, logical and saturating arithmetic instructions with simple and easily analysed pipeline execution behaviours. Multiply and divide instructions are not included in this group. Documentation indicates the following:

- Execution in Master Pipeline only.

- Read at most two general registers (GR) during ID stage

- CMOV, SASF and SETF read Program Status Word (PSW) during ID stage

- Most instructions write to PSW, presumably during EX stage

- Execution in EX stage during one clock cycle.

- Write back to at most one register in WB

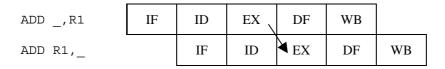

Reading and writing general registers or PSW is a potential source of pipeline execution delays, due to data hazards [9]. We must consider both data hazards and structural hazards. Structural hazards will result if the register file has too few read or write ports. Delays due to read-after-write hazards (RAW) are usually avoided since the V850E pipeline architecture includes forwarding techniques (an example shown in Figure 6-1), but there are cases when they occur.

Figure 6-1: Forwarding (arrow) eliminates RAW hazard delay.

Emulator tests verify that the type of operand (immediate or register) show no impact on execution times. This indicates that at least two registers can be read in ID during a single clock cycle. Tests also verify that in any case of RAW hazards among this group of instructions, forwarding eliminates delay cycles. We expect however RAW hazards on GR or PSW to cause delays in cases such as a load instruction followed by an arithmetic instruction.

| EP2: Instruction reading one or two GR during ID stage. | (Yes/No)  |

|---------------------------------------------------------|-----------|

| EP3: Instruction writing to GR in WB stage.             | (Yes/No)* |

\*Value range of EP3 will be redefined in section 6.1.8

□ EP4: Instruction reading PSW during ID stage. (Yes/No)

□ EP5: Instruction writing PSW during EX stage. (Yes/No)

#### 6.1.3 Enable and disable interrupt instructions

Analysed instructions: EI and DI

Sets or resets bit in Program Status Word. The EFD shows execution terminates after EX stage. This is also an indication that PSW writing occurs during EX stage. Emulator tests show no extra delays at any time due to RAW hazards on PSW.

#### 6.1.4 System Register load and store instructions

Analysed instructions: LDSR and STSR

Uses the Master Pipeline. The EFD shows normal execution in five clock cycles without causing any pipeline delays for the next instruction. Moving system registers (SR) to and from general registers may cause delay cycles. The User's Manual claims that such delays occur if system registers EIPC or FEPC are loaded by Load System Register (LDSR) and then immediate stored to a GR by Store System Register (STSR). However, our emulator tests do not show these exceptions to cause any delays at all.

□ EP6: Instruction reading SR, other than PSW.

□ EP7: Instruction writing SR, other than PSW.

(Yes/No)

#### 6.1.5 Store and load instructions

Analysed instructions: LD, ST, SLD, and SST

32-bit Store (ST), 16-bit Short format Store (SST) and 32-bit Load (LD) all execute their first three stages in the Master Pipeline. The memory address is probably calculated in the EX stage. Memory access is then performed in the MEM stage of the Additional Pipeline. Total execution time is expected to be five clock cycles in isolation since we have assumed that data memory accesses take a single clock cycle. Executing flow of LD, ST, and SST is shown in Figure 6-2a.

We also assume that the size of accessed data does not impact access times, as long as data alignment is respected. Tests in emulator confirm these assumptions.

The EFD indicates that a RAW hazard between LD and succeeding instruction will cause a single clock cycle delay. This is also verified by emulator tests.

16-bit Short format Load (SLD) executes in the four-stage Additional Pipeline. Address calculation is performed instantly during the ID stage. Total execution time in isolation is thereby only four clock cycles. Executing flow of SLD is shown in Figure 6-2b.

| IF ID | EX | MEM | WB | 1 |

|-------|----|-----|----|---|

|-------|----|-----|----|---|

Figure 6-2a: Execution flow of LD, ST, and SST.

| IF ID | MEM | WB |

|-------|-----|----|

|-------|-----|----|

Figure 6-2b: Execution flow of SLD.

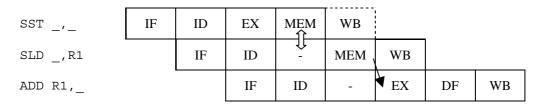

Since SLD uses the MEM stage one cycle "in advance", forwarding normally takes care of any RAW hazard, eliminating extra delays. However, if the preceding instruction also executes in the MEM stage, a structural hazard can occur and delay SLD memory access. This has impact on total execution time if a RAW hazard occurs between SLD and it's succeeding instruction. Such scenario is shown in Figure 6-3.

Figure 6-3: SST and SLD conflict in MEM stage (block arrow). ADD becomes one cycle delayed.

Emulator experiments verify the normal SLD execution time given by the User's Manual. Testing also confirm the SLD/ADD RAW delay shown in picture.

#### □ EP8: Instruction accessing memory in MEM stage. (Yes/No)\*

#### 6.1.6 Unconditional jump/branch instructions

Analysed instructions: JR, JARL, JMP, and BR

Jumps and branches change instruction flow by overwriting Program Counter (PC) unconditionally. This behaviour always causes a pipeline execution delay.

The EFD shows the instructions as terminated after the ID stage, implying that the PC is changed during execution of this stage. The succeeding instruction is also invalidated in its IF stage during this clock cycle and the branch destination instruction is fetched and executed in the IF stage during the

<sup>\*</sup>Value range of EP8 will be redefined in section 6.1.10

next cycle. A static branch delay of a single clock cycle is thereby derived from the EFD, and emulator tests verify this for JR, JARL and BR.

However, emulator tests show the static branch delay of JMP to be two clock cycles. This corresponds well to Table 5-10 of the User's Manual while the Execution Flow Diagram shows only a single delay cycle, i.e. the documentation is inconsistent. We assume that JMP modifies PC during execution of the EX stage, which is not shown in the EFD. This may also indicate that JMP execute in the Master Pipeline while JR, JARL and BR use the Additional Pipeline.

☐ EP9: Instruction modifying PC. (Uncond. with 1 cycle static delay/ Uncond. with 2 cycle static delay)\*

\*Value range of EP9 will be augmented in section 6.1.7

#### 6.1.7 Conditional branch instructions

Analysed instructions: all variants of Bcond

Conditional branch instructions (Bcond) read PSW and PC. If the PSW satisfies the branch condition, then the displacement given by the operand is added to PC value and written back to the PC. All these operations are performed in the ID stage in a single clock cycle and the Bcond instruction terminates after this. During this cycle, the succeeding instruction in the instruction memory executes in the IF stage. All Bcond execute in the Additional Pipeline according to the User's Manual.

The EFD shows two types of execution scenarios: branch not taken and branch taken.

Branch not taken: Since the branch condition is not satisfied, the succeeding instruction is valid and can continue execution. No branch delays occur. The Bcond simply becomes a NOP, except for reading PSW.

Branch taken: Similar to unconditional branch. The succeeding instruction is invalidated and the change of PC causes a branch delay of a single clock cycle.

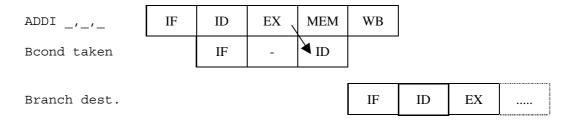

If an instruction immediate preceding Bond writes to PSW (e.g. an addition instruction), Bond is delayed in the IF stage for one extra clock cycle due to a RAW hazard on PSW. This happens only when Bond eventually decides branch taken. This scenario is shown in Figure 6-4. When branch not is taken, correct instruction is already executing and no pipeline delays occur.

We believe this execution behaviour to be reasonable, but it is not correctly documented in the User's Manual. Table 5-10 of the User's Manual indicates no delay for the PSW RAW-delay scenario, which is completely wrong.

Emulator tests verify one and two cycle delays for branch taken (depending on PSW read/write) and no delays for branch not taken scenarios, regardless of PSW read.

Figure 6-4: ADDI writes PSW in EX stage. The branch destination instruction becomes delayed one extra cycle. The example assumes that the branch destination instruction is a 16-bit instruction or a word-aligned 32-bit instruction.

We augment the value range of EP9:

□ EP9: Instruction modifying PC. (Uncond. with 1 cycle static delay/

Uncond. with 2 cycle static delay/

Cond.)

#### 6.1.8 Multiply instructions

Analysed instructions: MULH, MULHI, MUL, and MULU

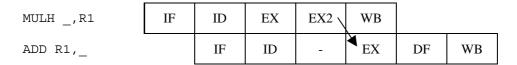

All multiply instructions execute in two consecutive and fully pipelined EX stages. These stages are not shown in the general pipeline configuration figure in the User's Manual, but we assume that the second EX stage can be viewed as corresponding to the DF stage of Master Pipeline. Emulator tests confirm that RAW hazards between multiply instructions and their succeeding instructions cause a delay of a single clock cycle. An example is shown in Figure 6-5.

Figure 6-5: Execution of MULH with special EX2 stage. RAW hazard on R1 causes a single cycle delay of ADD. (Arrow shows forwarding)

32-bit MUL and MULU potentially write to two GR. Emulator tests show that these instructions always cause a delay clock cycle, independent of any data hazard. This delay is not shown in the Execution Flow Diagram but indicated in Table 5-10 of the User's Manual.

□ EP10: Instruction execution in EX stage more than once. (Number of EX stage cycles)

**Redefinition of EP3 value range:**

□ EP3: Instruction writing to GR in WB stage. (Number of GR's)

#### 6.1.9 Divide instructions

Analysed instructions: DIVH, DIV, and DIVU

Like other arithmetic instructions, divide instructions execute in the Master Pipeline. The execution loops in the EX stage, 33 loops for unsigned divide instructions and 34 for signed. All documentation claims a static pipeline delay of 33 and 34 clock cycles for next executing instruction. This is confirmed by emulator tests.

#### 6.1.10 Bit manipulation instructions

Analysed instructions: SET1, CLR1, and TST1

This set of instructions is typical for microcontroller chips, but not present on desktop RISC designs. Their purpose is set or reset specific bits in data memory. The operation requires the instructions to loop from MEM stage back to EX stage during execution.

EFD shows that SET1, CLR1 and NOT1 perform two rounds in EX and MEM stage and then terminate, while TST1 terminates immediately after executing the second EX stage since it does not have to write back to memory.

The succeeding instruction is always delayed for two clock cycles due to the extra execution round. SET1, CLR1 and NOT1 will cause

The second execution in MEM stage for SET1, CLR1 and NOT1 will also cause a structural hazard if the next instruction is a SLD. This will have impact on total execution time if a RAW hazard occur between the SLD and its succeeding instruction. (Similar to the scenario described in section 6.1.6) This is not a fact for TST1 since it do not execute twice in MEM stage.

Emulator tests verify timings including delays for all scenarios above.

| SET1 _,_ | IF | ID | EX | MEM | EX | MEM     | WB  |    |

|----------|----|----|----|-----|----|---------|-----|----|

| SLD _,_  |    | IF | ı  | -   | ID | -<br>ît | MEM | WB |

Figure 6-6: Execution of SET1 followed by SLD. The two first cycle delays of SLD are statically delays, i.e. independent of type of instruction following SET1, but the third cycle delay is caused by a structural conflict on MEM stage (block arrow).

□ EP11: Instruction executes EX stage after MEM stage (Yes/No)

Redefinition of EP8 value range:

□ EP8: Instruction accessing memory in MEM stage. (Number of clock cycles)

#### 6.1.11 TRAP and RETI

Analysed instructions: TRAP and RETI

The execution of the TRAP instruction is shown in the Execution Flow Diagram as a six-stage pipeline with two successive ID stages. The shown usage of two ID stages is hard to interpret. It could mean that the ID stage of the Master Pipeline is used twice, but also that execution is performed in the ID stages of both Master and Additional Pipeline.

The EFD also shows execution termination after WB stage. This is strange since TRAP only read and write system registers, ending by writing PC, and the documentation indicates that all other instructions performing system register access does this in ID or EX stage.

RETI works as a return instruction and restores PC and PSW from two system registers. Execution is described in the EFD with a similar six-stage pipeline as TRAP. Execution is terminated after EX stage, however.

Both TRAP and RETI cause a two-cycle delay to the target instruction according to all documentation. This is confirmed by emulator tests. Emulator tests where adjacent instructions manipulate the system registers render no additional delays.

#### 6.1.12 CALLT and CTRET

Analysed instructions: CALLT and CTRET

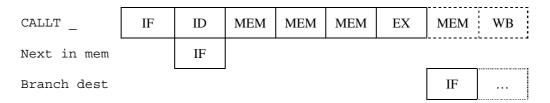

CALLT is a table indirect branch instruction. Its execution behaviour, as given by the EFD, is very hard to interpret. Execution is most likely initiated in the Additional Pipeline since a memory address is first calculated and then used in the MEM stage, which follows directly after the ID stage. Address calculation can be done in the ID stage of the Additional Pipeline even though the User's Manual generally claims that this pipeline is dedicated for SLD and branch instructions. After MEM stage, execution continues back to the EX stage of the Master Pipeline and then terminates.

All documentation in the User's Manual states a static delay of four clock cycles. Emulator tests render however a static delay of six cycles. Readings from emulator log-files indicate that CALLT suspends itself for two extra cycles. This may be related to MEM stage where internal ROM is accessed and not

data memory (internal RAM). The User's Manual states internal ROM access time in the MEM stage to three clock cycles, which correspond well to this assumption. Similar additional delay also occurs when testing SWITCH (see below), which also access internal ROM in the MEM stage.

Since the MEM stage is used immediately after the ID stage, a structural hazard in the MEM stage will occur if, for example, a ST instruction precedes CALLT. The emulator confirms an extra delay cycle for CALLT in this scenario.

Figure 6-7: Execution of CALLT. Internal ROM is accessed in MEM stage (three clock cycles).

The indirect-branch instruction CTRET is used for returning from a CALLT call. CTRET reads the return address and PSW value from the system registers CTPC and CTPSW. It is not clear when these registers are read. Emulator tests show no delays if system registers CTPC or CTPSW are written by LDSR directly before CTRET executes.

CTRET itself always causes a static two-cycle delay, similar to JMP. As for JMP, this is correctly documented in Table 5-10 of the User's Manual, but not in the Execution Flow Diagram.

#### 6.1.13 SWITCH

Analysed instruction: SWITCH

The table indirect branch instruction SWITCH executes an additional EX stage after MEM stage, similar to instruction TST1. SWITCH ends its operations by writing PC in this second EX stage and then terminates. This causes a static delay of four clock cycles according to all documentation in the UM. Since internal ROM is accessed in MEM stage, an additional pipeline delay of two clock cycles occurs when testing SWITCH execution time in the emulator.

#### 6.1.14 Move Word instruction

Analysed instruction: MOV (imm32)

The MOV imm32 instruction transfers a 32-bit immediate value, given by its operand, to a GR. Since this instruction is 48 bits long and the IF stage only handles 32 bits during a single clock cycle, a pipeline delay must occur. The EFD describes execution as taking two cycles in EX stage, thereby causing the next instruction to be delayed for one cycle. We can not interpret this diagram any further but the execution times, including delay cycle, given by the EFD and Table 5-10 of the User's Manual are confirmed by emulator tests. Assuming a delay in both IF and EX stage gives one delay cycle too much. No other delays, caused by adjacent instructions or data hazards, are found in emulator tests.

#### 6.1.15 PREPARE and DISPOSE

Analysed instructions: all variants of PREPARE and DISPOSE

These are another example of complex instructions typical for microcontroller architectures. They are normally used when entering or returning from sub-routine calls, for saving and restoring register contents on a memory stack.

The instruction length for PREPARE varies from 32 to 64 bits depending on instruction operands.

The isolated execution times for PREPARE and DISPOSE is always dependent upon the operands, typically the numbers of GR to be saved or restored.

PREPARE reads the contents of up to 12 GR and writes this to memory. Other registers, such as Stack and Element Pointer (sp, ep) are also manipulated. For all these operations, the EFD shows only a looping behaviour in MEM stage during execution. We can not analyse this execution behaviour any further since the documentation and the emulator test traces do not provide us with enough detailed information. This also embraces the execution behaviour of DISPOSE.

Emulator tests confirm execution times given in the User's Manual for all PREPARE and DISPOSE flavours. These tests also show no indications for additional pipeline delays due to adjacent instructions.

#### 6.1.16 HALT

NOT analysed instruction: HALT

The HALT instruction is not a subject of analysis since its "execution time" is completely arbitrary.

## 6.2. Analysis of Parallel Execution Scenarios (Dual Issue)

A dual issue scenario may occur when two adjacent 16-bit instructions are available to be processed in the IF stage simultaneous, e.g. fetched together by the 32-bit prefetch unit. The instructions must also execute separately in the Master and Additional Pipeline.

Dual issue is not well documented in the User's Manual. There are no clear specifications of possible dual issue pairs or under which circumstances they are valid and can execute in parallel. Only a single Execution Flow Diagram in the User's manual shows an example of a dual issue scenario, with an ADD and an unspecified "branch" instruction as dual issue pair. Our analysis, including emulator tests, indicates that this EFD is only partially correct and only if the "branch" instruction is the instruction BR. Furthermore, the "branch destination instruction" will in this case be delayed one more clock cycle than indicated in the EFD.

The given pipeline configuration in the User's Manual (reproduced in Figure 5-1) indicates SLD, Bcond instructions and BR as candidates for second instruction in dual issue pairs. We used emulator tests to search for possible companions, and we found four cases of dual issue scenarios.

#### 6.2.1 Dual issue case 1: \* / SLD

By testing each 16-bit instruction together with SLD we found that all arithmetic and logical operation instruction trigger a dual issue scenario. This includes 16-bit multiply instruction MULH and also NOP. Divide instruction DIVH is not qualified, probably due to the in-order issue/execution requirement of V850 family (see chapter 5: Pipeline Analysis), and neither are any branch/jump instructions or memory accessing instructions (i.e. SST and SLD).

We also discovered some very strange execution behaviours when valid dual issue pairs are repeated in our test codes. The instructions of the second pair and all subsequent pairs become separately issued one instruction per each clock cycle. By experimenting, we found that some instructions enable a new pair to be dual issued if such an instruction executes before the dual issue pair. Another group of instructions shares the property of disabling an already enabled dual issue scenario if executed after enabling instruction but before the dual issue pair.

These two instruction groups are very heterogeneous, i.e. instructions with very different semantics and normal execution properties. Thus we have not discovered the common factors that cause these behaviours. Instead, we strongly suspect this to be symptoms of emulator incorrectness, or plain bugs in the core pipeline.

To be consistent, we have added enabling and disabling \*/SLD dual issue to our list of execution parameters.

```

□ EP12: Instruction enables */SLD dual issue. (Yes/No)

□ EP13: Instruction disables */SLD dual issue. (Yes/No)

```

#### 6.2.2 Dual issue case 2: \* / Bcond

Bond instructions often become delayed due to PSW RAW hazards, which was found earlier. Emulator tests show clearly that instructions writing PSW can never be dual issued with Bond. This holds even if branch is not taken. Dual issue may also be disabled if the immediately preceding instruction writes PSW. This invalidates the ADD/Bond example given in the User's Manual.

Emulator experiments also show that SST and SLD are valid dual issue instruction together with Bcond. This is not expected for SLD since the User's Manual claims that SLD share the ID stage of the Additional Pipeline with Bcond.

#### 6.2.3 Dual issue case 3: \* / BR

BR is not sensitive to PSW accesses. Emulator tests show that all other 16-bit instructions can be dual issued together with BR. Exceptions are DIVH and branch/jump instructions. SLD is once again valid, which is remarkable.

#### 6.2.4 Dual issue case 4: MOV / \*

When examining the assembler code from several benchmark programs and real world applications, all compiled with the IAR compiler, we noticed a quite common instruction sequence:

```

MOV <reg1>, <reg3>

ADD <reg2>, <reg3>

```

The V850 family lacks a three-address addition instruction, i.e. that adds content from register #1 and register #2 and writes result to register #3 without corrupting registers #1 and #2. The sequence above mimics the behaviour of such a three-address ADD.

Running this sequence in the emulator render a surprising dual issue scenario. The ADD simply disappears from the instruction trace. We can not tell if this is a totally undocumented chip feature where the two instructions perhaps are translated into a "virtual" three-address ADD, or if it just is a very odd emulator bug.

Emulator tests show that operand relations must be as in the sequence above. This dual issue scenario also holds for all other 16-bit arithmetic and logical instruction variants with register read and write-semantic identical to ADD reg, reg.

This concludes the dual issue analysis. The result is presented in Appendix B: Table B-1. In this table, each 16-bit instruction is classified according to how they participate in valid dual issue scenarios. The dual issue classification is also added to the list of execution parameters.

□ EP14: Dual issue classification. (Classification number)

## 6.3. Analysis of Instruction Execution Interference.

Execution scenarios where an executing instruction interferes directly with a third or even fourth instruction without interfering with the intervening instruction are not described or clearly indicated in the V850E documentation. If such a scenario exists, then it probably must be included in our test suite, rendering more complex test code patterns. Otherwise, test code patterns can be simplified and

shortened, since they only have to be designed with regard to instruction interference between adjacent instructions.

#### 6.3.1 Single Issue Scenarios

We first analyse scenarios where each instruction is issued individually.

We make the following fundamental assumptions: