# Efficient Symbolic State Exploration of Timed Systems: Theory and Implementation

JOHAN BENGTSSON

# **Efficient Symbolic State Exploration of Timed Systems: Theory and Implementation**

BY Johan Bengtsson

May 2001

DEPARTMENT OF COMPUTER SYSTEM

INFORMATION TECHNOLOGY

UPPSALA UNIVERSITY

UPPSALA

SWEDEN

Dissertation for the degree of Licentiate of Philosophy in Computer Systems at Uppsala University 2001

# Efficient Symbolic State Exploration of Timed Systems: Theory and Implementation

Johan Bengtsson johanb@docs.uu.se

Department of Computer System

Information Technology

Uppsala University

Box 337

SE-751 05 Uppsala

Sweden

http://www.it.uu.se/

© Johan Bengtsson 2001 ISSN 1404-5117

Printed by the Department of Information Technology, Uppsala University, Sweden

### **Abstract**

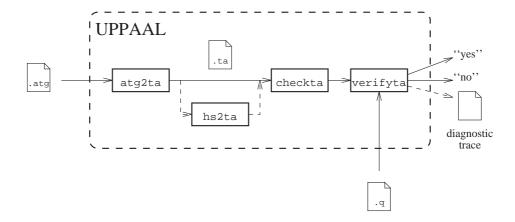

Timing aspects are important for the correctness of safety-critical systems. It is crucial that they are carefully analysed in designing such systems. UPPAAL is a tool designed to automate the analysis process. In UPPAAL, a system under construction is described as a network of timed automata and the desired properties of the system can be specified using a query language. Then UPPAAL can be used to explore the state space of the system description to search for states violating (or satisfying) the properties. If such states are found, the tool provides diagnostic information, in form of executions leading to the states, to help the desginers, for example, to locate bugs in the design.

The major problem for UPPAAL and other tools for timed systems to deal with industrial-size applications is the state space explosion. This thesis studies the sources of the problem and develops techniques for real-time model checkers, such as UPPAAL, to attack the problem. As contributions, we have developed local-time semantics for timed systems to allow partial order reductions, the notion of committed locations to model atomicity and a number of implementation techniques to reduce time and space consumption in state space exploration. The techniques are studied and compared by case studies. Our experiments demonstrate significant improvements on the performance of UPPAAL.

# Acknowledgements

First I want to thank my supervisor Wang Yi, for guiding me towards the completion of this thesis. I have learnt a lot during the years we have been working together. I also would like to thank all current and former colleagues in the "UPPAAL-group" in Uppsala, *i.e.* Tobias Amnell, Alexandre David, Elena Fersman, Fredrik Larsson, Justin Pearson and Paul Petterson. It has been a pleasure working together with you, discussing implementation issues and other problems. Further I want to thank Kim G. Larsen and the rest of the Aalborg part of the UPPAAL project for stimulating collaboration. Without your participation UPPAAL would not have been what it is today. I am also grateful to all my other co authors, *i.e.* David Griffioen, Bengt Johnsson and Johan Lilius, for fruitful discussions. It has been fun working with you.

Last but not least I want to thank my family. Without their love, support and encouragement this thesis would never have been possible.

- This thesis is based on four different publications, written between 1995 and 2001.

- **Paper A:** Johan Bengtsson. Reducing Memory Usage in Symbolic State-Space Exploration for Timed Systems. Technical Report, 2001-009, Department of Information Technology, Uppsala University, 2001.

- **Paper B:** Johan Bengtsson, Bengt Jonsson, Johan Lilius and Wang Yi. Partial Order Reductions for Timed Systems. In Proceedings, Ninth International Conference on Concurrency Theory, volume 1466, Lecture Notes in Computer Science, Springer Verlag, 1998

- Paper C: Johan Bengtsson, W. O. David Griffioen, Kåre J. Kristoffersen, Kim G. Larsen, Fredrik Larsson, Paul Pettersson and Wang Yi. Automated Analsysis of an Audio-Control Protocol using UPPAAL. In Proceedings, Ninth International Conference on Computer Aided Verification, volume 1102, Lecture Notes in Computer Science, Springer Verlag, 1996

- **Paper D:** Johan Bengtsson, Kim Larsen, Fredrik Larsson, Paul Pettersson and Wang Yi. UPPAAL a Tool Suite for Automatic Verification of Real-Time Systems. In Proceedings, Hybrid Systems III: Verification and Control, volume 1066, Lecture Notes in Computer Science, Springer Verlag, 1995

# **Comments on My Participation**

- **Paper A:** I discussed the content with Wang Yi. I implemented everything and wrote the report.

- **Paper B:** I participated in discussions and wrote part of the paper. I made a prototype implementation but it is not described in the paper.

- **Paper C:** I participated in some of the discussions and implemented committed locations in UPPAAL. I have also made minor revisions to the semantics for committed location.

- Paper D: I implemented UPPAAL together with Fredrik Larsson.

# **Contents**

| Introd | uction |                                                                    | 1  |

|--------|--------|--------------------------------------------------------------------|----|

| 1      | Back   | ground                                                             | 1  |

| 2      | The S  | State Explosion Problem for Timed Systems                          | 2  |

| 3      | Contr  | ributions                                                          | 3  |

| 4      | Conc   | lusions and Future Work                                            | 4  |

| -      |        | lucing Memory Usage in Symbolic State-Space Exploration<br>Systems | 13 |

| 1      | Introd | duction                                                            | 15 |

| 2      | Time   | d Automata and Reachability Analysis                               | 17 |

|        | 2.1    | Timed Automata Model                                               | 17 |

|        | 2.2    | Reachability Analysis                                              | 19 |

|        | 2.3    | UPPAAL Extensions                                                  | 22 |

| 3      | Repre  | esenting Symbolic States                                           | 27 |

|        | 3.1    | Normal Representation                                              | 28 |

|        | 3.2    | Packed States                                                      | 29 |

|        | 3.3    | Packed Zones with Cheap Inclusion Check                            | 32 |

| 4      | Repre  | esenting Symbolic State-Space                                      | 35 |

|        | 4.1    | Representing WAIT                                                  | 36 |

|        | 4.2    | Representing PASSED                                                | 38 |

|        | 4.3    | Supertrace PASSED for Timed Automata                               | 39 |

|             | 4.4     | Hash Compaction for Timed Automata                      | 42 |

|-------------|---------|---------------------------------------------------------|----|

| 5           | Conc    | lusions                                                 | 46 |

| A           | Exam    | ples and Experiment Environment                         | 52 |

| Paper       | B: Part | tial Order Reductions for Timed Systems                 | 55 |

| 1           | Motiv   | vation                                                  | 57 |

| 2           | Prelin  | minaries                                                | 60 |

|             | 2.1     | Networks of Timed Automata                              | 60 |

|             | 2.2     | Symbolic Global–Time Semantics                          | 62 |

| 3           | Partia  | al Order Reduction and Local-Time Semantics             | 63 |

|             | 3.1     | Symbolic Local-Time Semantics                           | 66 |

|             | 3.2     | Finiteness of the Symbolic Local Time Semantics         | 68 |

| 4           | Partia  | al Order Reduction in Reachability Analysis             | 69 |

|             | 4.1     | Operations on Constraint Systems                        | 71 |

| 5           | Conc    | lusion and Related Work                                 | 72 |

| Paper<br>PA |         | omated Analsysis of an Audio-Control Protocol using UP- | 77 |

| 1           | Introd  | luction                                                 | 79 |

| 2           | Com     | mitted Locations                                        | 81 |

|             | 2.1     | An Example                                              | 82 |

|             | 2.2     | Syntax                                                  | 83 |

|             | 2.3     | Semantics                                               | 84 |

| 3           | Com     | mitted Locations in UPPAAL                              | 86 |

|             | 3.1     | The Model-Checking Algorithm                            | 86 |

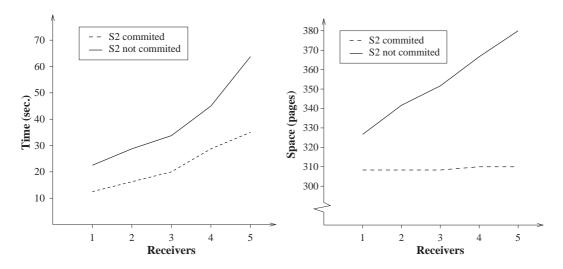

|             | 3.2     | Space and Time Performance Improvements                 | 87 |

| 4           | The A   | Audio Control Protocol with Bus Collision               | 88 |

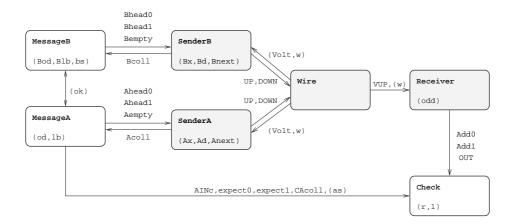

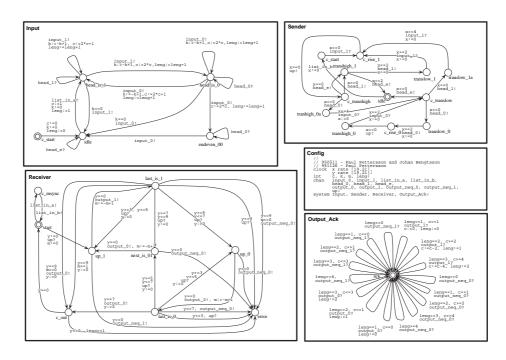

| 5           | A Fo    | rmal Model of the Protocol                              | 91 |

| 6 | Verifi            | ication in UPPAAL                                         | 93  |

|---|-------------------|-----------------------------------------------------------|-----|

| 7 | Conc              | lusions                                                   | 96  |

| A | The S             | System Description                                        | 98  |

| _ | D: UP<br>ne Syste | PAAL — a Tool Suite for Automatic Verification of Realems | 107 |

| 1 | Intro             | duction                                                   | 109 |

| 2 | An O              | Overview of UPPAAL                                        | 110 |

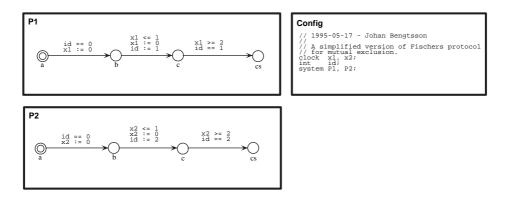

|   | 2.1               | Graphical Description of Networks of Timed Automata       | 111 |

|   | 2.2               | Textual Description of Networks of Timed Automata         | 111 |

|   | 2.3               | Linear Hybrid Systems                                     | 111 |

|   | 2.4               | Syntactical Checks                                        | 113 |

|   | 2.5               | Model-Checking                                            | 113 |

| 3 | The U             | UPPAAL Model                                              | 114 |

|   | 3.1               | Syntax                                                    | 114 |

|   | 3.2               | Semantics                                                 | 116 |

| 4 | The U             | UPPAAL Model-Checker                                      | 118 |

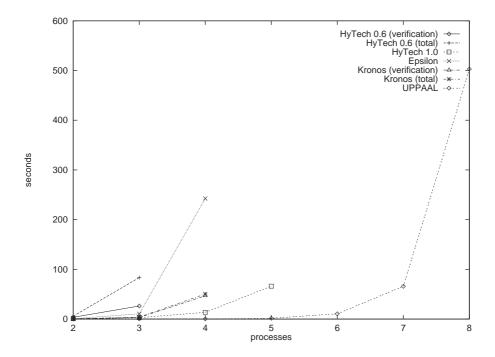

| 5 | Appli             | ications and Performance                                  | 120 |

| 6 | Conc              | Jusion and Future Work                                    | 122 |

# Introduction

# 1 Background

During the last decades, computers have become one of the most important tools in our society. They are no longer used only for word processing, banking or scientific computations. Nowadays computers are widely used in our daily life to control e.g. stereos, micro wave ovens, cars, medical equipments, aeroplanes *etc*. This change became possible due to the development of powerful micro processors that can be integrated in so called *embedded systems*. A large class of embedded systems is *real-time systems* where it is important that the control computer should deliver not only correct output, but also in time. As an example, consider an industrial robot that picks boxes from conveyor belt.

Because of the wide spread safety-critical applications of real time systems, their correct functioning has been an issue of vital importance in the system development process. Various new techniques have been developed to check the correctness of such systems. Among others, formal verification has been a promising technique to complement the traditional method by testing. The basic idea of formal verification is to describe the system under development in a formal systems and then apply rigorous methods to prove that the system meets its requirements (*e.g.* [Hoa69, Dij75, Hoa78, Rei85, Mil89, Hol91, AD90, AD94, BD91, Yi91, RR88, ACD90, CES86, AH94, HNSY92, SS95]).

In this thesis we focus on *model-checking* [CGP99]. In contrast to manual techniques, model-checking is fully automatic in the sense that the proof showing that a system satisfies a given requirement is constructed by the model-checker without manual interaction. In the past years, a large number of model-checkers have been developed by researchers for different application areas. For examples, we mention SPIN [Hol91, Hol97] for communication protocols and  $\text{Mur}\varphi$  [DDHY92] for concurrent and reactive systems, UPPAAL [LPY97, ABB+01] and KRONOS [DOTY95, Yov97, BDM+98] for timed systems and HYTECH [HHWT97] for hybrid sys-

tems. These tools have all been successfully applied to industrial-size case studies, e.g. [HLP98, JMMS98, SD95a, MMS97, LPY98, HSLL97, TY98, HWT96].

Even though the existing techniques and tools have become increasingly efficient and success stories are reported frequently, they currently do not scale up to the size of most industrial systems. The bottleneck is the state space explosion problem. The main source of the problem is that the state space of a system of parallel processes can grow exponentially with the number of components. This is due to the fact that parallelism is modelled by interleaving of steps from the processes. In the literature, various techniques have been proposed to attack the state space explosion problems e.g. partial order reductions [God90, Val90, Pel93], symmetry reductions [HJJJ84, ID96, ES97], loop reduction [LLPY97], sweep-line and state space caching methods to keep only part of the state space in main memory [Hol85, GHP95, SD96, CKM01], and probabilistic methods [Hol91, Hol98, WL93, SD95].

# 2 The State Explosion Problem for Timed Systems

During the past few years, a number of verification tools have been developed for real-time systems in the framework of timed automata (e.g. KRONOS and UP-PAAL [DOTY95, LPY97, BLL<sup>+</sup>98]). One of the major problems in applying these tools to industrial-size systems is the huge memory-usage (e.g. [BGK<sup>+</sup>96]) for the exploration of the state-space of a network (or product) of timed automata. The main reason is that the model-checkers must store a large number of symbolic states each of which contains information not only on the control structure of the automata but also the clock values specified by clock constraints or time zone. A well-known technique to represent time zone in the existing model checkers for timed systems is *Difference Bounds Matrices* [Dil89] (DBM). In DBM, the memory requirement for each state is quadratic in the number of clocks. For example, in a system with 10 clocks and 10 processes and each with 10 states, the time zone for each state requires 484 bytes in addition to 10 bytes for the control part.

It is crucial for performance to reduce the memory requirement to represent time zone. In the literature there are a few techniques that address this problem. In [DY96] live-range analysis is used to reduce the number of clocks in a model. By analysing the control structure of the model it is possible to compute, for each control location, the set of active (live) clocks. Then, for each state, only timing information regarding the active clocks need to be stored. Another approach is taken in [LLPY97]. This work is based on the observation that the DBM representation of a time zone often contain a lot of redundant information, *i.e.* the solution

set can be represented using much less constraints. The paper presents a three step procedure for computing a minimal set of constraints with the same solution set as a given DBM. One step further is presented in [BLP+99]. This paper introduce CDDs, a BDD-like structure for representation of time zones. The key feature of this structure is the possibility to store non-convex unions of zones. A CDD is a directed acyclic graph with two types of nodes: terminal nodes labelled true and false, and inner nodes labelled with pairs of clocks. The edges in this graph correspond to bounds on the difference between the clocks in source node.

# 3 Contributions

The main contribution of this thesis is in the implementation of UPPAAL. In particular, we have developed a number of efficient techniques to minimise memory usage in model checking timed systems. We study the memory consumption problem in two fronts: the data structures to store and manipulate each symbolic state and the whole state space. We present two different methods that can be used for packing states. First, we code the entire state as one large number using a multiply-and-add algorithm. This method yields a representation that is canonical and minimal in terms of memory usage but the performance for inclusion checking between states is poor. The second method is mainly intended to use for the timing part of the state and it is based on concatenation of bit strings. Using a special concatenation of the bit string representation of the constraints in a zone, ideas from [PS80] can be used to implement fast inclusion checking between packed zones. We attack the problem with large state spaces in two different ways. First, to get rid of states that do not need to be explored, as early as possible, we introduce inclusion checking already in the data structure keeping the states waiting to be explored. We also describe how this can be implemented without slowing down the verification process. Second, we investigate how supertrace [Hol91] and hash compaction [WL93, SD95] methods can be applied to timed systems. We also present a variant of the hash compaction method, that allows termination of branches in the search tree based on probable inclusion checking between states. These techniques have been implemented in the UPPAAL tool, evaluated and compared by real-life examples; their strengths and weaknesses are described.

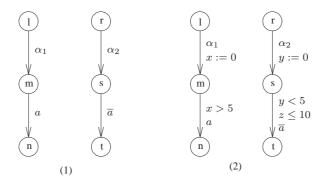

In addition, we have developed a partial-order reduction method for timed systems based on a *local-time* semantics for networks of timed automata. The main idea is to remove the implicit clock synchronisation between processes in a network by letting local clocks in each process advance independently of clocks in other processes, and by requiring that two processes *resynchronise* their local time

scales whenever they communicate. A symbolic version of this new semantics is developed in terms of predicate transformers, which enjoys the desired property that two predicate transformers are independent if they correspond to disjoint transitions in different processes. Thus we can apply standard partial order reduction techniques to the problem of checking reachability for timed systems.

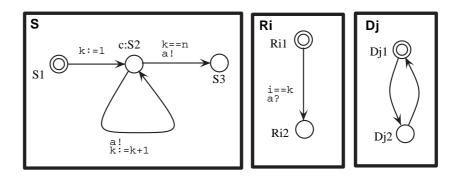

Another contribution is the notion of *committed locations*. This notion allows accurate modelling of atomic behaviours, such as atomic broadcast. More importantly committed location are utilised to guide the state-space exploration of the model checker to avoid exploring unnecessary interleavings of independent transitions. In the thesis we present a modified algorithm for state space exploration for networks of timed automata which generate a reduced number of states when committed locations are used. Our experimental results demonstrate significant time and space-savings of the modified model checking algorithm.

# 4 Conclusions and Future Work

The bottleneck for model checking technology to scale up is the state state explosion problem. For timed systems, the problem is even more critical because the model checker must keep track on not only the state space of the control structure of a system, but also timing constraints over the clock variables of the system.

This thesis summarises the implementation decisions and techniques adopted in UPPAAL. We have presented a collection of techniques to improve the performance of UPPAAL, in particular, to reduce the huge memory consumption in state space explosion. We believe that these techniques are general and applicable to other model checkers for timed systems. We would like to point out that the development of UPPAAL demonstrates it is possible today to build a model checker for timed systems that is both easy to use and capable of handling realistic, industrial size, systems.

The work presented in this thesis can be extended in several directions. As future work, we will study and develop techniques to reduce the memory requirements even further without losing performance, *e.g.* by finding better packing methods or developing hash functions for zones that still allow inclusion checking. Another challenge is to further investigate partial order reduction can be efficiently applied to timed automata. The local-time semantics is just a step on the way. Further investigations are needed to develop an efficient implementation of the technique. Hierarchical extensions to timed automata is a direction that is currently being pursued. A new challenge is how to take advantage of the hierarchical structures

to reduce the time and space consumption of the state space exploration process.

# **Bibliography**

- [ABB<sup>+</sup>01] Tobias Amnell, Gerd Behrmann, Johan Bengtsson, Pedro R. D'Argenio, Alexandre David, Ansgar Fehnker, Thomas Hune, Bertrand Jeannet, Kim G. Larsen, M. Oliver Möller, Paul Pettersson, Carsten Weise, and Wang Yi. UPPAAL Now, Next, and Future. In *Modelling and Verification of Parallel Processes*, number 2067 in Lecture Notes in Computer Science, pages 100–125. Springer-Verlag, 2001.

- [ACD90] Rajeev Alur, Costas Courcoubetis, and David L. Dill. Model-checking for real-time systems. In *Proceedings, Seventh Annual IEEE Symposium on Logic in Computer Science*, pages 414–425. IEEE Computer Society Press, 1990.

- [AD90] Rajeev Alur and David L. Dill. Automata for modeling real-time systems. In *Proceedings, Seventeenth International Colloquium on Automata, Languages and Programming*, volume 443 of *Lecture Notes in Computer Science*, pages 322–335. Springer-Verlag, 1990.

- [AD94] Rajeev Alur and David L. Dill. A theory of timed automata. *Journal of Theoretical Computer Science*, 126(2):183–235, 1994.

- [AH94] Rajeev Alur and Thomas A. Henzinger. A really temporal logic. *Journal of the ACM*, 41(1):181–204, 1994.

- [BD91] Bernard Berthomieu and Michel Diaz. Modeling and verification of timed dependent systems using timed petri nets. *IEEE Transactions on Software Engineering*, 17(3):259–273, 1991.

- [BDM<sup>+</sup>98] Marius Bozga, Conrado Daws, Oded Maler, Alfredo Olivero, Stavros Tripakis, and Sergio Yovine. Kronos: a model-checking tool for real-time systems. In *Proceedings, Tenth International Conference on Computer Aided Verification*, volume 1427 of *Lecture Notes in Computer Science*. Springer-Verlag, 1998.

- [BGK<sup>+</sup>96] Johan Bengtsson, W. O. David Griffioen, Kåre J. Kristoffersen, Kim G. Larsen, Fredrik Larsson, Paul Petterson, and Wang Yi. Verification of an audio protocol with bus collision using UPPAAL. In *Proceedings, Eigth International Conference on Computer Aided Verification*, Lecture Notes in Computer Science. Springer-Verlag, 1996.

- [BLL<sup>+</sup>98] Johan Bengtsson, Kim G. Larsen, Fredrik Larsson, Paul Pettersson, Yi Wang, and Carsten Weise. New Generation of UPPAAL. In *Int. Workshop on Software Tools for Technology Transfer*, June 1998.

- [BLP<sup>+</sup>99] Gerd Behrmann, Kim G. Larsen, Justin Pearson, Carsten Weise, and Wang Yi. Efficient timed reachability analysis using clock difference diagrams. In *Proceedings, Eleventh International Conference on Computer Aided Verification*, volume 1633 of *Lecture Notes in Computer Science*, pages 341–353. Springer-Verlag, 1999.

- [CES86] E. M. Clarke, E. A. Emerson, and A. P. Sistla. Automatic verification of finite-state concurrent systems using temporal logic specifications. *ACM Transactions on Programming Languages and Systems*, 8(3):244–263, 1986.

- [CGP99] Edmund M. Clarke, Orna Grumberg, and Doron A. Peled. *Model Checking*. The MIT Press, 1999.

- [CKM01] Søren Christensen, Lars Michael Kristensen, and Thomas Mailund. A sweep-line method for state space exploration. In *Proceedings, Seventh International Conference on Tools and Algorithms for the Construction and Analysis of Systems*, volume 2031 of *Lecture Notes in Computer Science*, pages 450–464. Springer-Verlag, 2001.

- [DDHY92] David L. Dill, Andreas J. Drexler, Alan J. Hu, and C. Han Yang. Protocol verification as a hardware design aid. In *Proceedings, IEEE International Conference on Computer Design, VLSI in Computers and Processors*, pages 522–525. IEEE Computer Society Press, 1992.

- [Dij75] E. W. Dijkstra. Guarded commands, nondeterminacy and formal derivation of programs. *Communications of the ACM*, 18(8):453–457, 1975.

- [Dil89] David L. Dill. Timing assumptions and verification of finite-state concurrent systems. In *Proceedings, Automatic Verification Methods for Finite State Systems*, volume 407 of *Lecture Notes in Computer Science*, pages 197–212. Springer-Verlag, 1989.

- [DOTY95] Conrado Daws, Alfredo Olivero, Stavros Tripakis, and Sergio Yovine. The tool kronos. In *Proceedings, Hybrid Systems III: Verification and Control*, volume 1066 of *Lecture Notes in Computer Science*. Springer-Verlag, 1995.

- [DY96] Conrado Daws and Sergio Yovine. Reducing the number of clock variables of timed automata. In *Proceedings*, 17th IEEE Real-Time Systems Symposium. IEEE Computer Society Press, 1996.

- [ES97] E. Allen Emerson and A. Prasad Sistla. Using symmetry when modelchecking under fairness assumptions: An automata theoretic approach. *ACM Transactions on Programming Languages and Systems*, 19(4), 1997.

- [GHP95] Patrice Godefroid, Gerard J. Holzmann, and Didier Pirottin. State-space caching revisited. *Journal of Formal Methods in System Design*, 7(3):227–241, 1995.

- [God90] Patrice Godefroid. Using partial orders to improve automatic verification methods. In *Proceedings, Second International Conference on Computer Aided Verification*, volume 531 of *Lecture Notes in Computer Science*, pages 176–185. Springer-Verlag, 1990.

- [HHWT97] Thomas A. Henzinger, Pei-Hsin Ho, and Howard Wong-Toi. HYTECH: A model checker for hybrid systems. *Journal on Software Tools for Technology Transfer*, pages 110–122, 1997.

- [HJJJ84] Peter Huber, Arne M. Jensen, Leif O. Jespen, and Kurt Jensen. Towards reachability trees for high-level petri nets. In *Proceedings, Advances on Petri Nets '84*, volume 188 of *Lecture Notes in Computer Science*. Springer-Verlag, 1984.

- [HLP98] Klaus Havelund, Mike Lowry, and John Penix. Formal analysis of a space craft controller using Spin. In *Proceedings, Fourth International SPIN Workshop*, 1998. Proceedings available online. URL: http://netlib.bell-labs.com/netlib/spin/ws98/program.html.

- [HNSY92] Thomas A. Henzinger, Xavier Nicollin, Joseph Sifakis, and Sergio Yovine. Symbolic model checking for real-time systems. In *Proceedings, Seventh Annual IEEE Symposium on Logic in Computer Science*, pages 394–406, 1992.

- [Hoa69] C. A. R. Hoare. An axiomatic basis for computer programming. *Communications of the ACM*, 12(10):576–580, 1969.

- [Hoa78] C. A. R. Hoare. Communicating sequential processes. *Communications of the ACM*, 21(8):666–677, 1978.

- [Hol85] Gerhard J. Holzmann. Tracing protocols. *AT&T Technical Journal*, 64(10), 1985.

- [Hol91] Gerard J. Holzmann. *Design and Validation of Computer Protocols*. Prentice-Hall, 1991.

- [Hol97] Gerard J. Holzmann. The model checker Spin. *IEEE Transactions on Software Engineering*, 23(5):279–295, 1997.

- [Hol98] Gerard J. Holzmann. An analysis of bitstate hashing. *Journal of Formal Methods in System Design*, November 1998.

- [HSLL97] Klaus Havelund, Arne Skou, Kim G. Larsen, and Kristian Lund. Formal modelling and analysis of an audio/video protocol: An industrial case study using uppaal. In *Proceedings*, 18th IEEE Real-Time Systems Symposium, pages 2–13. IEEE Computer Society Press, 1997.

- [HWT96] Thomas A. Henzinger and Howard Wong-Toi. Using hytech to synthesize control parameters for a steam boiler. In *Formal Methods* for Industrial Applications: Specifying and Programming the Steam Boiler Control, number 1165 in Lecture Notes in Computer Science, pages 265–282. Springer-Verlag, 1996.

- [ID96] C. Norris Ip and David L. Dill. Better verification through symmetry. *Journal of Formal Methods in System Design*, 9, 1996.

- [JMMS98] Wil Janssen, Radu Mateescu, Sjouke Mauw, and Jan Springintveld. Verifying business processes using SPIN. In *Proceedings, Fourth International SPIN Workshop*, 1998. Proceedings available online. URL: http://netlib.bell-labs.com/netlib/spin/ws98/program.html.

- [LLPY97] Kim G. Larsen, Fredrik Larsson, Paul Pettersson, and Wang Yi. Efficient verification of real-time systems: Compact data structure and state space reduction. In *Proceedings*, 18th IEEE Real-Time Systems Symposium, pages 14–24. IEEE Computer Society Press, 1997.

- [LPY97] Kim G. Larsen, Paul Petterson, and Wang Yi. Uppaal in a nutshell. *Journal on Software Tools for Technology Transfer*, 1997.

- [LPY98] Magnus Lindahl, Paul Pettersson, and Wang Yi. Formal Design and Analysis of a Gear-Box Controller. In *Proceedings, Fourth Workshop on Tools and Algorithms for the Construction and Analysis of*

- *Systems*, number 1384 in Lecture Notes in Computer Science, pages 281–297. Springer-Verlag, 1998.

- [Mil89] Robin Milner. *Communication and Concurrency*. Prentice Hall International Series in Computer Science. Prentice Hall, 1989.

- [MMS97] John C. Mitchell, Mark Mitchell, and Ulrich Stern. Automated analysis of cryptographic protocols using Murφ. In *Proceedings*, 1997 Conference on Security and Privacy, pages 141–153. IEEE Computer Society Press, 1997.

- [Pel93] Doron Peled. All from one, one for all: on model checking using representatives. In *Proceedings, Fifth International Conference on Computer Aided Verification*, volume 697 of *Lecture Notes in Computer Science*, pages 409–423. Springer-Verlag, 1993.

- [PS80] Wolfgang J. Paul and Janos Simon. Decision trees and random access machines. In *Logic and Algorithmic*, volume 30 of *Monographie de L'Enseignement Mathématique*, pages 331–340. L'Enseignement Mathématique, Université de Genève, 1980.

- [Rei85] Wolfgang Reisig. Petri nets. An Introduction. In *EATCS Monographs* on *Theoretical Compute Science*, volume 4. Springer Verlag, 1985.

- [RR88] G. M. Reed and A. W. Roscoe. A timed model for communicating sequential processes. *Theoretical Computer Science*, 58(1-3):249–261, 1988.

- [SD95a] Ulrich Stern and David L. Dill. Automatic verification of the SCI cache coherence protocol. In *Correct Hardware Design and Verification Methods: IFIP WG10.5 Advanced Research Working Conference Proceedings*, 1995.

- [SD95b] Ulrich Stern and David L. Dill. Improved probabilistic verification by hash compaction. In *Correct Hardware Design and Verification Methods: IFIP WG10.5 Advanced Research Working Conference Proceedings*, 1995.

- [SD96] Ulrich Stern and David L. Dill. Combining state space caching and hash compaction. In *Methoden des Entwurfs und der Verifikation digitaler Systeme: 4. GI/ITG/GME Workshop Proceedings*, 1996.

- [SS95] Oleg V. Sokolsky and Scott A. Smolka. Local model checking for real-time systems. In *Proceedings, Seventh International Conference on Computer Aided Verification*, volume 939 of *Lecture Notes in Computer Science*. Springer-Verlag, 1995.

- [TY98] Stavros Tripakis and Sergio Yovine. Verification of the fast reservation protocol with delayed transmission using the tool kronos. In *Proceedings, Fourth IEEE Real-Time Technology and Applications Symposium*. IEEE Computer Society Press, 1998.

- [Val90] Antti Valmari. A stubborn attack on state explosion. In *Proceedings*, *Second International Conference on Computer Aided Verification*, volume 531 of *Lecture Notes in Computer Science*, pages 156–165. Springer-Verlag, 1990.

- [WL93] Pierre Wolper and Dennis Leroy. Reliable hashing without collision detection. In *Proceedings, Fifth International Conference on Computer Aided Verification*, volume 697 of *Lecture Notes in Computer Science*, pages 59–70. Springer-Verlag, 1993.

- [Yi91] Wang Yi. CCS + time = an interleaving model for real time systems. In *Proceedings, Eighteenth International Colloquium on Automata, Languages and Programming*, volume 510 of *Lecture Notes in Computer Science*. Springer-Verlag, 1991.

- [Yov97] Sergio Yovine. Kronos: A verification tool for real-time systems. *Journal on Software Tools for Technology Transfer*, 1, October 1997.

# Paper A:

**Reducing Memory Usage in Symbolic State-Space Exploration** for Timed Systems

Johan Bengtsson. Technical Report, 2001-009, Department of Information Technology, Uppsala University, 2001.

# Reducing Memory Usage in Symbolic State-Space Exploration for Timed Systems

### Johan Bengtsson

**Abstract.** One of the major problems to scale up model checking techniques to the size of industrial systems is the large memory consumption. This report address the problem in the context of verifiers for timed systems and present a number of techniques that reduce the amount memory used for state space exploration in such a tool. The methods are evaluated and compared by real-life examples and their strengths and weaknesses are described. In particular we adress the memory consumption problem on two fronts, first by reducing the size of each symbolic state by means of compression and second by reducing the size of the stored state space by early inclusion checking and probabilistic methods.

# 1 Introduction

During the last ten years timed automata [AD90, AD94] has evolved as a common model to describe timed systems. This process has gone hand in hand with the development of verification tools for timed automata. The two best known of these tools are UPPAAL [LPY97, ABB+01] and KRONOS [DOTY95, Yov97]. One of the major problems in applying these tools to industrial-size systems is the large memory consumption (*e.g.* [BGK+96]) when exploring the state space of a network of timed automata. The reason is that the exploration does not only suffer from the large number of states that needs to be explored, but also from the large size of each state.

In the literature a number of approaches studying these problems have been developed, for both timed and untimed systems: Some methods do not only aim at the memory consumption but also reduce the reachable state space of a system, such as partial order reduction methods [God90, Val90, Pel93] and symmetry reductions [HJJJ84, ID93]. Other methods aim at reducing the number of states stored in the passed list. In the global reduction technique from [LLPY97] all states that are not possible loop entry points are never entered in the passed list. A related method is the sweep-line technique described in [CKM01]. Here a notion of progress is used to throw away parts of the passed list that can never be revis-

ited. The work presented in [SD98] describe how the passed list can be pushed down in the memory hierarchy, from main memory to disk, with a very small penalty in terms of increased runtime. On the border between reducing the size of the state space and reducing the size of each state we find the work presented in [DY96]. In this work, methods similar to live-range analysis in compilers are used to reduce the number of clocks in timed automata. Another method that fits into this group is the CDD technique described in [BLP+99]. Here a BDD-like structure, that can represent unions of zones efficiently, is used to store the timing information for each state.

In probabilistic methods, such as the supertrace method [Hol91] and the hash compaction method [WL93, SD95], the demand for exact verification is relaxed in order to save space. In these methods there is a probability that a part of the state space will never be visited during verification.

In this report we address both the problem of large state spaces and the problem of large states.

The problem with large symbolic states is addressed by means of compaction. We present two different methods that can be used for packing states. First, we code the entire state as one large number using a multiply-and-add algorithm. This method yields a representation that is canonical and minimal in terms of memory usage but the performance for inclusion checking between states is poor. The second method is mainly intended to use for the timing part of the state and it is based on concatenation of bit strings. Using a special concatenation of the bit string representation of the constraints in a zone, ideas from [PS80] can be used to implement fast inclusion checking between packed zones.

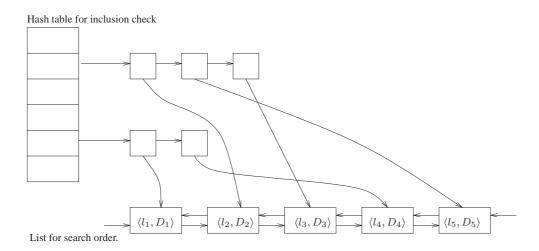

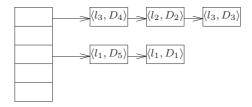

We attack the problem with large state spaces in two different ways. First, to get rid of states that do not need to be explored, as early as possible, we introduce inclusion checking already in the data structure keeping the states waiting to be explored. We also describe how this can be implemented without slowing down the verification process. Second, we investigate how supertrace [Hol91] and hash compaction [WL93, SD95] methods can be applied to timed systems. We also present a variant of the hash compaction method, that allows termination of branches in the search tree based on probable inclusion checking between states.

The rest of report is organised as follows: In section 2 we introduce timed automata as a model for timed systems and give a brief introduction on how to check properties for systems modelled as timed automata.

In section 3 we present three ways to represent the key objects used in checking timed automata, namely the symbolic states. We also give a comparison between them.

Section 4 addresses issues on the state space of a model. We describe how the wait and past lists are handled in UPPAAL. We also describe an approximation method of the past list that can be used when the complete state space of a model is too big to be stored in memory.

Finally, section 5 wraps up the report by summarising the most important results and suggests some directions for future work.

A description of the platform and examples used to evaluate the presented techniques is given in Appendix A.

# 2 Timed Automata and Reachability Analysis

In this section we briefly review the notation. A more extensive description can be found in *e.g.* [AD94, Pet99]. For clarity, we start by describing a version of timed automata which is somewhat simplified compared to the model used in UPPAAL and then extend it to the full UPPAAL model in a less formal manner.

## 2.1 Timed Automata Model

Let  $\Sigma$  be a finite set of labels, ranged over by a,b etc. A timed automaton is a finite state automaton over alphabet  $\Sigma$  extended with a set of real valued clocks, to model time dependent behaviour. Let  $\mathcal C$  denote a set of clocks, ranged over by x,y,z. Let  $\mathcal B(C)$  denote the set of conjunctions of atomic constraints of the form  $x\sim n$  or  $x-y\sim n$  for  $x,y\in \mathcal C, \infty\in\{\le,<,=,>,\ge\}$  and  $n\in\mathbb N$ . We use g and later D to range over this set.

**Definition 1 (Timed Automaton)** A timed automaton A is a tuple  $\langle N, l_0, \rightarrow, I \rangle$  where N is a set of control nodes,  $l_0 \in N$  is the initial node,  $\rightarrow \in N \times \mathcal{B}(C) \times \Sigma \times 2^C \times N$  is the set of edges and  $I: N \longrightarrow \mathcal{B}(C)$  assign invariants to locations. As a simplification we will use  $l \stackrel{g,a,r}{\longrightarrow} l'$  to denote  $\langle l, g, a, r, l' \rangle \in \rightarrow$ .

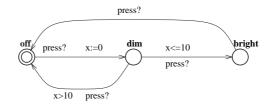

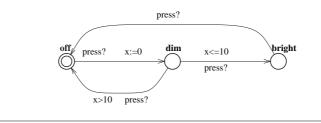

An example automaton is shown in Figure 1. The automaton is a model of a time dependent light switch. Initially the the light is off and if the switch is pressed a dim light is switched on. If the switch is pressed one more time within 10 seconds the light gets brighter but if the second press is later than 10 seconds after the first, the light is switched off. If the switch is pressed when the light is bright, the light is switched off.

Figure 1: A timed automaton modelling a light switch.

The clocks values are formally represented as functions, called clock assignments, mapping  $\mathcal C$  to the non-negative reals  $\mathbb R_+$ . We let u,v denote such functions, and use  $u\in g$  to denote that the clock assignment u satisfy the formula g. For  $d\in\mathbb R_+$  we let u+d denote the clock assignment that map all clocks x in  $\mathcal C$  to the value u(x)+d, and for  $r\subseteq \mathcal C$  we let  $[r\mapsto 0]u$  denote the clock assignment that map all clocks in r to 0 and agree with r for all clocks in r to 0.

The semantics of a timed automaton is a timed transition-system where the states are pairs  $\langle l, u \rangle$ , with two types of transitions, corresponding to delay transitions and discrete action transitions respectively:

•

$$\langle l, u \rangle \xrightarrow{\epsilon(t)} \langle l, u + t \rangle$$

if  $u \in I(l)$  and  $(u + t) \in I(l)$

•

$$\langle l, u \rangle \xrightarrow{a} \langle l', u' \rangle$$

if  $l \xrightarrow{g,a,r} l', u \in g, u' = [r \mapsto 0]u$  and  $u' \in I(l')$

It is easy to see that the state space is infinite and thus not a good base for algorithmic verification. However, efficient algorithms may be obtained using a *symbolic semantics* based on *symbolic states* of the form  $\langle l, D \rangle$ , where  $D \in \mathcal{B}(C)$  [HNSY92, YPD94]. The symbolic counterpart of the transitions are given by:

•

$$\langle l, D \rangle \leadsto \langle l, D^{\uparrow} \wedge I(l) \rangle$$

•

$$\langle l, D \rangle \leadsto \langle l', r(D \wedge g) \rangle$$

if  $l \xrightarrow{g,a,r} l'$

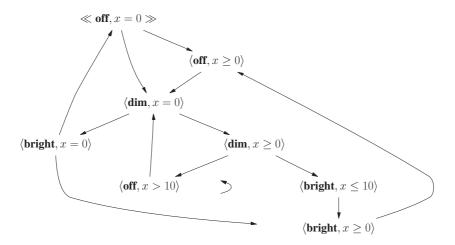

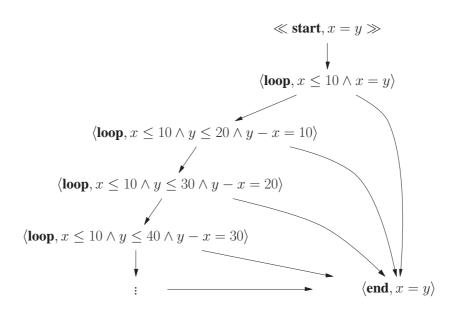

where  $D^{\uparrow} = \{u+d \mid u \in D \land d \in \mathbb{R}_+\}$  and  $r(D) = \{[r \mapsto 0]u \mid u \in D\}$ . It can be shown that the set of constraint systems is closed under these operations. Moreover the symbolic semantics correspond closely to the standard semantics in the sense that if  $\langle l, D \rangle \leadsto \langle l', D' \rangle$  then, for all  $u' \in D'$  there is  $u \in D$  such that  $\langle l, u \rangle \to \langle l', u' \rangle$ . As an example, the symbolic semantics of the lamp switch is shown in Figure 2.

Figure 2: Symbolic semantics of lamp switch automaton

Figure 3: Timed automaton with an infinite symbolic semantics

# 2.2 Reachability Analysis

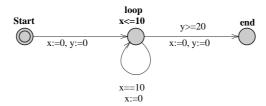

Given a timed automaton with symbolic initial-state  $\langle l_0, D_0 \rangle$  and a symbolic state  $\langle l, D \rangle$ ,  $\langle l, D \rangle$  is said to be *reachable* if  $\langle l_0, D_0 \rangle \leadsto^* \langle l, D_n \rangle$  and  $D \cap D_n \neq \emptyset$  for some  $D_n$ . This problem may be solved using a standard reachability algorithm for graphs. However the unbounded clock values may render an infinite zone graph and thus might the reachability algorithm not terminate. As an example, consider the automaton in Figure 3. The symbolic semantics of this simple automaton is shown in Figure 4. The symbolic state space is infinite because a clock drifts away unboundedly. The solution problem is to introduce a *k-normalised* version of the infinite symbolic semantics. The idea is to utilise the maximum constant appearing in clock constraints in the automaton, to render a finite symbolic semantics. For details we refer the reader to [Pet99, Rok93] but the main fact and the intuition behind it will be described here.

In order to do this we first have to introduce the notion of closed constraint sys-

Figure 4: Symbolic semantics of timed automaton in Figure 3

tems. We say that a constraint system  $D \in \mathcal{B}(C)$  is closed under entailment or just closed, for short, if no constraint in D can be strengthened without reducing the solution set.

**Proposition 1** For each constraint system  $D \in \mathcal{B}(C)$  there is a unique constraint system  $D' \in \mathcal{B}(C)$  such that D and D' have exactly the same solution set and D' is closed under entailment.

From this proposition we conclude that a closed constraint system can be used as a canonical representation of a zone.

Given a zone D and a natural number k, the k-normalisation of D, denoted  $\operatorname{norm}_k(D)$ , is computed from the closed representation of D by (a) removing all constraints of the form  $x < m, x \le m, x - y < m$  and  $x - y \le m$  where m > k, (b) replacing all constraints of the form  $x > m, x \ge m, x - y > m$  and  $x - y \ge m$  where m > k with x > k and x - y > k respectively. This can then be used to define a notion of k-normalised symbolic transitions  $(\leadsto_k)$  by modifying the transitions of the standard symbolic semantics to preserve k-normalisation. The discrete action transition already preserves this so there is no need to modify it, but the delay transition should be modified to  $\langle l, D \rangle \leadsto_k \langle l, \operatorname{norm}_k(D^\uparrow \wedge I(l)) \rangle$ .

**Proposition 2** Assume a timed automaton A with symbolic initial-state  $\langle l_0, D_0 \rangle$  and let k be the largest constant appearing in any constraint in A. Then  $\langle l, D \rangle$  is reachable from  $\langle l_0, D_0 \rangle$  if and only if there is a sequence of k-normalised transitions  $\langle l_0, D'_0 \rangle \leadsto_k^* \langle l, D'_n \rangle$  such that  $D \cap D'_n \neq \emptyset$ .

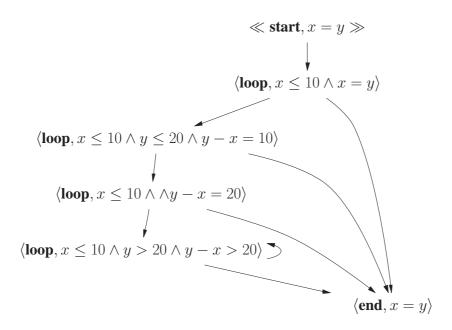

Figure 5: 20-normalised symbolic semantics for automaton in Figure 3

The intuition behind this construction is that when the value of a clock is larger than the maximum constant appearing in A it is not possible for any edge in A to distinguish the actual value of the clock, only that the value is above the maximum constant. Therefore it is not needed to keep track of the actual value of the clock when it is larger than the maximum constant. As an example we apply this to the automaton from Figure 3. For this automaton, the maximum constant is 20 (from the guard on y on the edge from **loop** to **end**). Thus we need to compute the 20-normalised symbolic semantic of the automaton to preserve the reachability properties. This semantics can be found in Figure 5.

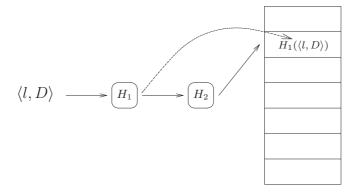

Using this we will get a finite symbolic state-space where we can apply a standard reachability algorithm for graphs, such as the one in Algorithm 1. The algorithm uses two important data structures: WAIT and PASSED. WAIT is a list of states waiting to be explored. By controlling how new states are added to WAIT the exploration order can be altered. If WAIT is organised as a queue the exploration will be breadth first, and if WAIT is organised as a stack the exploration will be depth first. When the exploration is started the initial state is placed in WAIT. PASSED is a table of states explored so far. Initially PASSED is empty. Due to the size of the state space, these structures may consume a considerable amount of main memory.

### Algorithm 1 Symbolic reachability analysis

```

Passed = \emptyset, Wait = \{\langle l_0, D_0 \rangle\}

while Wait \neq \emptyset do

take \langle l, D \rangle from Wait

if l = l_f \wedge D \cap D_f \neq \emptyset then return "YES"

if D \nsubseteq D' for all \langle l, D' \rangle \in \text{Passed} then

add \langle l, D \rangle to Passed

for all \langle l', D' \rangle such that \langle l, D \rangle \leadsto_k \langle l', D' \rangle do

add \langle l', D' \rangle to Wait

end for

end if

end while

return "NO"

```

### 2.3 UPPAAL Extensions

In UPPAAL there are some extensions to the model described above. The most important of these are networks of timed automata (to model parallel tasks), shared integer variables, urgent channels and committed locations.

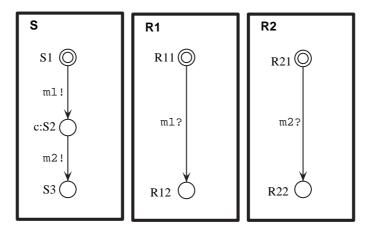

### **Networks of Timed Automata**

To model concurrent systems, UPPAAL has a notion of a *network of timed automata*, *i.e.* several timed automata (called processes) are combined into a single system. Synchronisation between the processes are performed either using the edge labels or, as will be described later, using shared integer variables.

To control synchronisation we partition the set of labels into *local labels* and *synchronising labels*. The synchronising labels are then paired two by two In UPPAAL each such pair of synchronising labels is called a channel and they share a common prefix (or channel name) followed by either! or?. A label test! will be called an *output* on channel test and test? will be called an *input* on the same channel.

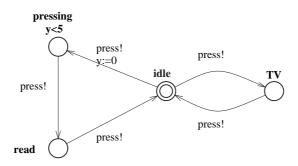

As an example, consider the network in Figure 6. Here the lamp switch model described earlier have been combined with a model of a user. This particular user have two main interests, reading and watching TV, which he may start doing at any time. If the user wants to watch TV he press the switch once to get a cosy dim light and starts to watch. If, on the other hand, the user wants to read he press the switch twice within five seconds to get a light bright enough for reading and starts to read.

Figure 6: A network of timed automata modelling a light switch and its user.

The semantics of a network is similar to the semantics of a single timed automaton; the difference is that we have to define how processes interact. A state is a pair  $\langle \bar{l}, u \rangle$ , the difference to the timed automata semantics is that the location of a network is a vector of control locations, one for each process in the system. In a network there are three types of transitions, delay transitions, local action transitions and synchronising action transitions. The delay transitions works exactly like delay transitions for single timed automata with the exception that for a network the invariant on the current location of all processes have to be taken into account. The discrete action transition type of the single timed automata is split into two types in the network case. A discrete action transition of a network is either a local action transition, where one of the processes makes a move entirely on its own, or a synchronising action transition, where two processes synchronise on a channel and move simultaneously. The transition rules are as follows:

•

$$\langle \bar{l}, u \rangle \xrightarrow{\epsilon(t)} \langle \bar{l}, u + t \rangle$$

if  $u \in I(\bar{l})$  and  $(u + d) \in I(\bar{l})$ , where  $I(\bar{l}) = \bigwedge I(l_i)$

•

$$\langle \bar{l}, u \rangle \xrightarrow{a} \langle \bar{l}[l'_i/l_i], u' \rangle$$

if  $l_i \xrightarrow{g,a,r} l'_i, u \in g, u' = [r \mapsto 0]u, u' \in I(\bar{l}[l'_i/l_i])$

$$\begin{array}{l} \bullet \ \left\langle \bar{l},u\right\rangle \xrightarrow{\tau} \left\langle \bar{l}[l_i'/l_i][l_j'/l_j],u'\right\rangle \ \text{if} \ l_i \xrightarrow{g_i,a?,r_i} l_i',l_j \xrightarrow{g_j,a!,r_j} l_j',i \neq j,u \in g_i \land g_j,u' = [r_i \cup r_j \mapsto 0]u \ \text{and} \ u' \in I(\bar{l}[l_i'/l_i][l_j'/l_j]). \end{array}$$

This concrete semantics are then easily extended to a normalised symbolic semantics that can serve as a base for model checking procedures.

#### **Shared Integer Variables**

As a convenience, the timed automata model of UPPAAL has a notion of *shared integer variables*. Each network of timed automata  $A_1|\cdots|A_n$  is augmented with a set,  $\mathcal{D}$ , of integer variables each with a bounded domain and an initial value. Predicates over the integer variables can be used as guards on the edges in any process and their values can be updated on by any process, as a part of the reset. In the current versions of UPPAAL an *integer guard* have the form  $E_1 \sim E_2$  where  $E_1, E_2$  are integer expressions over  $\mathcal{D}$ , as defined by the grammar below, and  $\sim \in \{<, \leq, =, \neq, \geq, >\}$ . An *integer reset* has the form v := E where  $v \in \mathcal{D}$  and E is an integer expression over  $\mathcal{D}$ . The integer expressions are generated by the following syntax:

$$E ::= E + E \mid E - E \mid E * E \mid E/E \mid n \mid v$$

Where  $n \in \mathbb{Z}$  is an integer value and  $v \in \mathcal{D}$  is an integer variable. This expression can easily be extended to handle function calls and procedures but it is currently not implemented.

The semantics needs to be extended to deal with the integer variables. A state of a network is now a triple  $\langle \bar{l}, d, u \rangle$  where  $\bar{l}$  and u are as before and d is a function mapping each variable in  $\mathcal{D}$  to a value in its domain. Functions such as d will be called *integer assignments*. Similar to clock assignments we use  $d \in g_i$  to denote that the integer assignment d satisfies the integer guard  $g_i$ .

Since delay does not affect the integer variables the delay transitions are the same as for networks without integer variables. The action transitions are extended in the natural way, *i.e.* for an action transition to be enabled the integer assignment must satisfy all integer guards on the corresponding edges and when a transition is taken the integer assignment is updated according to the integer resets.

However, there is one problem with this extension that needs to be considered. How should we handle the case where one of the processes participating in a synchronising transition updates a variable that is at the same time used by the other. There are three possible solutions to this problem, first it is possible to prevent this by demanding that the integer resets of the edges in a synchronising transition may not update a variable that is used or updated by the other. This property can

<sup>&</sup>lt;sup>1</sup>Used in the sense that the variable is either updated itself or its value is needed to compute the new value of another variable.

be checked, either statically or during verification, and an error can be reported to the user if the property does not hold. Second, the situation can be handled by introducing a non-determinism where either of the resets are performed before the other. However, this feature would probably be of little use to user and the extra non-determinism introduced may give a significantly larger state space. The third solution is to give a defined order between the resets on the edges. In UPPAAL resets on the edge with an output-label is performed before the resets on the edge with an input-label. The drawback is that this solution destroys symmetry properties that could have been used to optimise the state space search, but on the other hand it can be utilised to create more efficient models.

#### **Urgent Channels**

In the standard network model processes are always allowed to delay up to the time specified by the location invariants even if there are enabled synchronisation actions. Sometime this is the wanted behaviour but on other occasions the preferred behaviour would be that the synchronisation occurred as soon as it gets enabled. To allow the second type of behaviours as well as the first, UPPAAL has a notion of urgent channels. An urgent channel works much like an ordinary channel, but with the exception that if a synchronisation on an urgent channel is possible the system may not delay. Interleaving with other enabled action transitions, however, is still allowed. In order to keep the time regions representable using one normal zone we forbid clock guards on edges synchronising on urgent channels. To illustrate why this restriction is necessary we use an example.

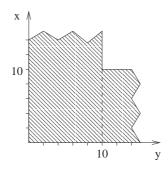

Consider the network presented in Figure 7. Both processes may independently go from their first state to their second state. In the second state the processes must delay for at least 10 time units before they are allowed to wait for synchronisation on the urgent channel u. As soon as both processes have spent 10 time units in their second state they should synchronise and move to their third state. The problem with this network arise in  $[\mathbf{S1,T1}]$ . As you see in Figure 8, the timing region for this state is not representable using a zone. Since the synchronisation occurs as soon as the transition is enabled the region won't even be convex.

For this simple example the problem can be solved by splitting the timing region into two zones (marked by a dashed line in the figure), but for a more complicated example the number of zones needed to represent one timing region may be much larger.

Figure 7: An example of a network with non convex timing regions.

Figure 8: Timing region for state [S1,T1] in the network from Figure 7.

#### **Committed Locations**

For some some models it is necessary to have a notion of atomic sequences of actions, *e.g.* to model atomic broadcast or multicast. In UPPAAL this notion is supported using so called *committed locations*. A committed location is a control location where no delay is allowed and if any process is in such a location then only transitions starting in a committed location are enabled. Thus, processes that are in committed locations may not be interleaved with processes that aren't. However, a process that is in a committed location may be interleaved with other processes that are in committed locations.

A little more formally, each process  $A_i$  in a network of timed automata has a set  $N_i^C \subseteq N_i$  of committed locations. For a location vector  $\bar{l}$  of the network, we use  $C(\bar{l})$  to denote the subset of the locations in  $\bar{l}$  that are committed. In the semantics the states have the same form as for networks without committed locations, but the transitions are somewhat different. First, delay must be forbidden if any process is in a committed location. Second, if there are processes that are in a committed location one of them must take part in the next transition. The transition rules are described in terms of the transitions for a network without committed location. In the description  $\rightarrow_c$  denote transitions for a network with committed locations and

→ denote transitions for a network without.

- $\langle \bar{l}, u \rangle \xrightarrow{\epsilon(t)}_c \langle \bar{l}, u + t \rangle$  if  $\langle \bar{l}, u \rangle \xrightarrow{\epsilon(t)} \langle \bar{l}, u + t \rangle$  and  $C(\bar{l}) = \emptyset$

- $\langle \bar{l}, u \rangle \to_c \langle \bar{l}[l_i'/l_i], u' \rangle$  if  $\langle \bar{l}, u \rangle \to \langle \bar{l}[l_i'/l_i], u' \rangle$  and either  $l_i \in C(\bar{l})$  or  $C(\bar{l}) = \emptyset$

- $\langle \bar{l}, u \rangle \xrightarrow{\tau}_c \langle \bar{l}[l_i'/l_i][l_j'/l_j], u' \rangle$  if  $\langle \bar{l}, u \rangle \xrightarrow{\tau} \langle \bar{l}[l_i'/l_i][l_j'/l_j], u' \rangle$  and either  $l_i \in C(\bar{l}), l_j \in C(\bar{l})$  or  $C(\bar{l}) = \emptyset$

# **3 Representing Symbolic States**

The symbolic states are the core objects of state space search, and one of the key issues in implementing an efficient model checker is how to represent them. The desired properties of the representation also differ in parts of the verifier, and there are potential gains in using different representations in different places.

In this section we will present different ways to represent symbolic states, explain their strengths and weaknesses and give hints on when to use them. But we start one level above, between the logical level with location vectors integer assignments and clock zones and the physical representation that is the focus of this section.

The encoding of the location vector and the integer assignment is, at this level, straight forward. For the location vector, we start by numbering the locations in each process. Then instead of a vector of locations, we get a vector of location numbers. For the integer assignment we number all the integer variables in the system and represent the assignment as a vector of integers, where the i:th element is the value of the variable with number i.

Representing the clock zone is a little trickier but starting from the constraint system representation of a zone it is possible to obtain an efficient intermediate representation. We start with the following observation:

Let 0 be a dummy clock with the constant value 0. Then for each constraint system  $D \in \mathcal{B}(\mathcal{C})$  there is a constraint system  $D' \in \mathcal{B}(\mathcal{C} \cup \{0\})$  with the same solution set as D, and where all constraints are of the form x - y < n or  $x - y \le n$ , for  $n \in \mathbb{Z}$ .

We also note that to represent any clock zone we need at most  $(|\mathcal{C} \cup \{0\}|)^2$  atomic constraints. One of the most compact ways to represent this is to use a matrix where each element represent a bound on the difference between two clocks. Each element in the matrix is a pair  $\langle n, \sim \rangle$  where n is an integer and  $\sim$  tells whether the bound is strict or not. Such a matrix is called a *Difference Bounds Matrix*, or

*DBM* for short. More detailed information about DBM:s and operations on them can be found in [Dil89].

Now we zoom in on the representation of a single bound in the DBM. Since we want a finite symbolic state space, we only consider normalised clock zones. Then, given a maximum constant k, the maximum number of significant values for any clock bound is  $2 \cdot (2k+2)$ . (Each bound is either in the interval [-k, k] or infinite, and it can be strict or non-strict<sup>2</sup>.)

## 3.1 Normal Representation

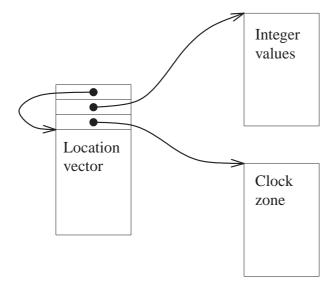

The simplest way to physically represent a symbolic state is to use a machine word for each control location, integer value or clock bound. The implementation is straight forward, but a practical tip is that if the standard library functions for memory management are used all the memory needed for one state should, if possible, be allocated in the same chunk, to minimise the allocation overhead. However, due to an early design decision, this is not the case in the UPPAAL implementation. In UPPAAL the symbolic state is split into three different objects: a state object containing a location vector and pointers to an integer assignment and a clock zone, an integer assignment object representing the integer values and an object representing the clock zone. A sketch of the connection between the objects is shown in Figure 9

The strength of this representation is its simplicity and the speed of accessing an individual control location, integer value, or clock bound. In this representation the maximum time needed to reach any individual entity is the time needed to fetch a word from the memory. This makes the representation ideal to use when we have to do operations on individual entities, *e.g.* when calculating the successors of a state. The weakness is the amount of wasted space. Here a whole machine word, typically 32-bit wide, is used to store entities where all possible values will fit in much less bits.

However this is a good base representation for states. It is ideal for states that will be modified in the near future, such as intermediate states or states in WAIT. It also works reasonably well for states in PASSED, specially for small and medium sized examples.

This representation is used for both WAIT and PASSED in the current version of UPPAAL.

<sup>&</sup>lt;sup>2</sup>For the infinite bound only strict is needed but non-strict is included for simplicity.

Figure 9: The symbolic state representation used in UPPAAL.

#### 3.2 Packed States

The second representation is on the opposite side of the spectra compared to the previous one and it can be used both for the discrete part of the states, for the clock zone and for both together. The encoding builds on a simple multiply and add scheme, similar to the position system for numbers, and it is very compact. In the description we will focus on encoding an entire symbolic state, but the parts can also be encoded separately.

First, consider the state as a vector  $v_1,\ldots,v_n$ , where each element represents a control location, the value of a variable or a clock bound. For each element  $v_i$  we can compute the number of possible values,  $|v_i|$ . For the location vector  $|v_i|$  is the number of control locations in the corresponding process, for the integer assignment  $|v_i|$  is the size of the domain of the corresponding variable and for the clock zone then  $|v_i|$  can be computed using the maximum constant k.

Now consider the vector as a number written down in a position system with a variable base, *i.e.* each element  $v_i$  is a digit and the product  $\prod_{j=0}^{i-1} |v_i|$  is its position value. Represent the state as the value of this number, *i.e.* encode the state as follows:

$$E(\langle l, D \rangle) = v_0 + \sum_{i=1}^{n} \left( v_i \cdot \prod_{j=0}^{i-1} |v_i| \right)$$

Note that in this context  $\langle l, D \rangle$  is a sequence of numbers. The encoding  $E(\langle l, D \rangle)$  is often too large to fit in a machine word and it have to be in fixed precision; some kind of bignums are needed. In our prototype implementation we used the GMP bignum package [Gra00].

**Proposition 3** The representation of states using bit string encoding is canonical and minimal in terms of space usage.

The strength of this representation is the effective use of space and the weakness is that to access an individual integer value or clock bound a number of division and modulo operations must be performed. This results in small states that are expensive to handle.

In order to test the performance of this representation, it is implemented in the PASSED structure in UPPAAL. In the implementation the packing algorithm has been re-shuffled in order to eliminate the use of temporary bignum variables. The implemented algorithm is listed as Algorithm 2.

#### Algorithm 2 Algorithm used to pack states

```

Parameters:

Location vector

Ī

Integer assignment vector

d

D

DBM representation of zone

E \Leftarrow \overline{l}[0]

for i = 1 to \#proc do

E \Leftarrow E * \# states(A_i) + \bar{l}[i]

end for

for i = 1 to \#var do

E \Leftarrow E * \operatorname{domain}(d[i]) + d[i]

end for

for i=0 to \#clock do

for j = 0 to \#clock do

if i \neq j then

E \Leftarrow E * 2k + D[i, j] + k

end if

end for

end for

```

In the experiment two different algorithms to check for visited states are used, one version where only equality checking is implemented and the other where inclusion checking is used for the clock zone part of the states. The version with only equality is straight forward. The version with inclusion checking for the clock

zone is a little more complicated. Now we have to unpack (at least) the zone part of the state in order to compare the DBMs bound by bound. This is described as Algorithm 3

**Algorithm 3** Algorithm used to compare packed states.

```

Parameters:

E_1

First state in comparison

E_2

Second state in comparison

inclusion(E_1, E_2) \Leftarrow t, inclusion(E_2, E_1) \Leftarrow t

cmp_1 \Leftarrow E_1, cmp_2 \Leftarrow E_2

for i = \#clock downto 0 do

for j = \#clock downto 0 do

if i \neq j then

inclusion(E_1, E_2) \Leftarrow inclusion(E_1, E_2) \land (cmp_1 \mod k \le cmp_2)

\mod k

inclusion(E_2, E_1) \Leftarrow inclusion(E_2, E_1) \land (cmp_2 \mod k \le cmp_1)

\mod k

cmp_1 \Leftarrow cmp_1/k

cmp_2 \Leftarrow cmp_2/k

end if

end for

end for

if cmp_1 \neq cmp_2 then

return 'E_1 is not related to E_2'

end if

case

\square inclusion(E_1, E_2) \land inclusion(E_2, E_1) \Rightarrow \mathbf{return} `E_1 = E_2`

\square inclusion(E_1, E_2) \land \neg inclusion(E_2, E_1) \Rightarrow \mathbf{return} `E_1 \subseteq E_2`

\square \neginclusion(E_1, E_2) \land inclusion(E_2, E_1) \Rightarrow return 'E_1 \supseteq E_2'

\square \neg inclusion(E_1, E_2) \land \neg inclusion(E_2, E_1) \Rightarrow \textbf{return} `E_1 \text{ is not related to}

E_2

end case

```

In Table 1 we see the performance for the packed representation with only equality checking for the clock zone. In the table the results are given both by measured numbers and relative to the current UPPAAL implementation. First, note that for the Field Bus example the verification does not terminate normally. (Denoted by  $\perp$  in the table.) The reason for this is that when only equality checking is used large parts of the state space are revisited, which makes WAIT expand until the verification process run out of memory. For the other examples the representation is very good, with space savings of up to 67% for Fischers protocol and 57% for

| Example              | Tim        | ne       | Space     |          |  |

|----------------------|------------|----------|-----------|----------|--|

|                      | real (Sec) | relative | real (MB) | relative |  |

| Field Bus (Faulty 1) |            |          |           |          |  |

| Field Bus (Faulty 2) | 上          | 上        |           |          |  |

| Field Bus (Faulty 3) | 上          | 上        |           |          |  |

| Field Bus (Fixed)    | 上          |          |           |          |  |

| B&O                  | 20.42      | 1.09     | 10.48     | 0.48     |  |

| DACAPO (big)         | 326.91     | 1.14     | 43.14     | 0.47     |  |

| DACAPO (small)       | 18.50      | 1.30     | 6.60      | 0.78     |  |

| Fischer 5            | 14.53      | 0.90     | 4.45      | 0.47     |  |

| Fischer 6            | 733.91     | 0.54     | 48.34     | 0.33     |  |

Table 1: Performance for packed states without inclusion checking

a more realistic example<sup>3</sup> at a very moderate slowdown (or even a speedup for Fischers protocol).

The result of the experiment with packed states where zone inclusion checking was implemented using division and modulo is shown in Table 2 (as absolute figures and in relation to the current PASSED implementation in UPPAAL). We note that using this representation we are able to verify all the examples and that the space performance is very good. However the time performance is very poor, for one instance Fischers protocol we notice a slowdown of almost 13 times and for one instance of the Field Bus protocol the slowdown is 8 times. The conclusion is that this representation should only be used in cases where main memory is a severe restriction.

# 3.3 Packed Zones with Cheap Inclusion Check

The main drawback of representing states using the number encoding given in section 3.2 is expensive inclusion checking. In this section we present a compact way of representing zones overcoming this drawback. The heart of this representation builds on an observation due to [PS80] that one subtraction can be used to perform multiple comparisons in parallel.

Let m denote the minimum number of bits needed to store all possible values for one clock bound. The DBM is then encoded as a long bit string, where each bound is assigned a m+1 bit wide slot. The value of the clock bound is put in the m

<sup>&</sup>lt;sup>3</sup>Fischers protocol behaves, as mentioned in Appendix A, different from all other examples, with respect to verification.

| Example              | Tim        | ne       | Space     |          |  |

|----------------------|------------|----------|-----------|----------|--|

|                      | real (Sec) | relative | real (MB) | relative |  |

| Field Bus (Faulty 1) | 541.32     | 3.70     | 23.05     | 0.30     |  |

| Field Bus (Faulty 2) | 956.55     | 4.34     | 33.80     | 0.29     |  |

| Field Bus (Faulty 3) | 10630.90   | 8.21     | 136.52    | 0.28     |  |

| Field Bus (Fixed)    | 2890.30    | 5.88     | 60.59     | 0.29     |  |

| B&O                  | 52.44      | 2.81     | 11.17     | 0.51     |  |

| DACAPO (big)         | 1379.45    | 4.81     | 34.01     | 0.37     |  |

| DACAPO (small)       | 31.67      | 2.23     | 5.55      | 0.65     |  |

| Fischer 5            | 94.31      | 5.82     | 4.18      | 0.45     |  |

| Fischer 6            | 17387.56   | 12.88    | 40.12     | 0.28     |  |

Table 2: Performance for packed states with expensive inclusion checking

least significant bits in the slot and the extra, most significant bit, is used as a *test bit*.

Since a zone D is included in another zone D' if and only if all bounds in the DBM representing D is as tight as the same bound in the DBM representation of D', inclusion checking is to check if all elements in one vector is less than or equal to the same bound in another vector. Using the new bit-string encoding of zones this can be checked using only simple operations like bitwise-and (&), bitwise-or (|), subtraction and test for equality.

Given two packed zones E(D) and E(D'), to check if  $D \subseteq D'$  first setting all the test bits in E(D) to zero and all the test bits in E(D') to one. In an implementation the test bits are usually zero in the stored states and setting them to one is done using a prefabricated mask M where all test bits are set to one. The test is then performed by calculating E(D') - E(D). The result is read out of the test bits. If a test bit is one the corresponding bound in D is at least as tight as in D' and if a test bit is zero the corresponding bound is tighter in D' than in D. Thus, if all test bits are one we can conclude that  $D \subseteq D'$  and if all the test bits are zero  $D \supset D'$ . It is worth noting that "all test bits are one" is both necessary and sufficient to conclude  $D \subseteq D'$  while "all test bits are zero" is only sufficient to conclude  $D \supset D'$ .

**Example 1** Consider a system with two clocks x, y and the maximum constant 2. In order to cut away some unnecessary detail, we don't consider strictness of bounds. The number of bits needed to store all possible values of one clock bound in this system is 3. Let  $D = \{x - y \le 1, y - x \le 1\}$  and  $D' = \{x - y \le 1, y - x \le 2\}$  be two zones that arise from a verification of this system.

| E(D)   | = | 0    | 011  | 0          | 011    | 0  | 011    | 0  | 001       | 0    | 011   | 0  | 001           |

|--------|---|------|------|------------|--------|----|--------|----|-----------|------|-------|----|---------------|

| E(D')  |   |      |      |            |        |    |        |    |           |      |       |    |               |

| H'(I)' | _ | 1 () | 1111 | $  \cap  $ | $\cap$ | () | $\cap$ | () | 1 (1(1) 1 | 1 () | -0.11 | -0 | $-0.10$ $\pm$ |

To check if  $D \subseteq D'$ , start by setting all the test bits in D' to one, e.g. by doing a bitwise or with the precomputed mask M. The extra bits set to one will serve two purposes. As mentioned above they will indicate the result of the comparison, but they will also serve as borrow bits and prevent interference between the packed bounds.

The actual comparison is then made by a subtraction. All the packed bounds will be subtracted by one subtraction operation, and since the test bits are set in the first term and unset in the second term the bounds will not interfere with each other.

Now the result of the inclusion check is read out of the test bits. Since all the test bits are one we conclude that  $D \subseteq D'$ .

In an implementation of this scheme the main issue is how to handle the bit strings. The easiest way is to let a bignum package, such as GMP, handle everything. However, this may give a considerable overhead, specially in connection with memory allocation, since the bignum packages are often tailored towards other types of applications. In UPPAAL we share the memory layout of the bignum packages, but to reduce the overhead we have implemented our own operations on top of it.

In the physical representation, *i.e.* how the bit-string is stored in memory, the bit-string is chopped up into machine-word sized chunks, or *limbs*. The limbs are then packed in big-endian order, *i.e.* the least significant limb first, in an array. If the bit string doesn't fill an even number of machine words the last limb padded with zero bits.

**Example 2** Assuming a nine-bit machine, the packed zone E(D') from Example 1 is represented as follows:

| 100110010 | 110011000 | 000001100 |

|-----------|-----------|-----------|

|-----------|-----------|-----------|

Noting that the effect of all operations needed for the inclusion check, except subtraction, is local within the limb and that subtraction only passes one borrow bit to the next more significant limb, we can implement the inclusion check in one pass through the array of limbs instead of one pass for each operation. The one pass inclusion check is shown in Algorithm 4. In the description we use E(D)[i] to denote the i:th limb of E(D) and  $-_w$  to denote a binary subtraction of machine word size.

#### Algorithm 4 Inclusion check for packed zones

```

\begin{aligned} &b \Leftarrow 0 \\ &\textbf{for } i = 1 \textbf{ to } \# \text{limbs } \textbf{do} \\ &\text{cmp} \Leftarrow (M[i] \mid E(D')[i]) -_w (E(D)[i] + b) \\ &\textbf{if } \text{cmp} \neq M[i] \textbf{ then return "false"} \\ &\textbf{if } (M[i] \mid E(D')[i]) < (E(D)[i] + b) \textbf{ then} \\ &b \Leftarrow 1 \\ &\textbf{else} \\ &b \Leftarrow 0 \\ &\textbf{end if} \\ &\textbf{end for} \\ &\textbf{return "true"} \end{aligned}

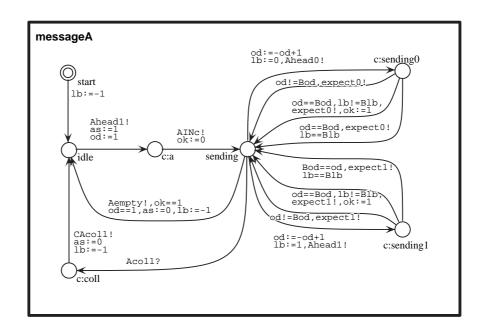

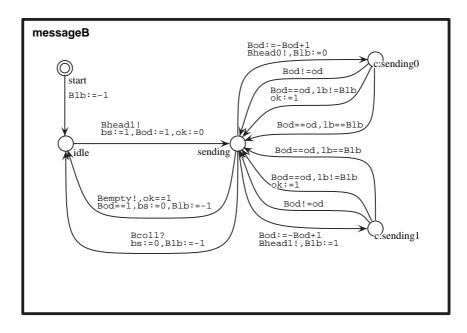

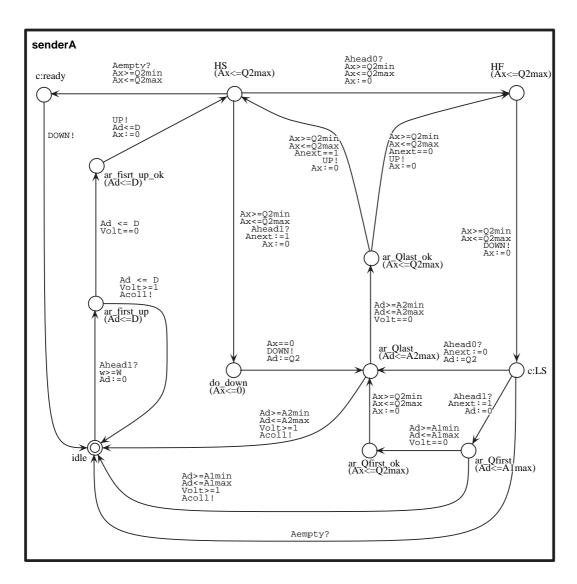

```