Why Memory Consistency Models Matter... And tools for analyzing and verifying them

Caroline Trippel & Yatin A. Manerkar

**Princeton University**

**UPMARC 2018**

While you wait:

1) Make sure you've got VirtualBox downloaded to your laptop:

https://www.virtualbox.org/wiki/Downloads

2) Make sure you have the most recent version of the Tutorial VM downloaded:

http://check.cs.princeton.edu/tutorial\_vm/Check\_Tools\_VM.ova

VM Password: mcmsarefun

http://check.cs.princeton.edu/tutorial.html

Memory Consistency Models (MCMs) Specify rules and guarantees about the <u>ordering</u> and <u>visibility</u> of accesses to shared memory [Sorin et al., 2011].

**Memory Consistency Models (MCMs)**

Specify rules and guarantees about the <u>ordering</u> and <u>visibility</u> of accesses to shared memory [Sorin et al., 2011].

Memory Consistency Models (MCMs) Specify rules and guarantees about the <u>ordering</u> and <u>visibility</u> of accesses to shared memory [Sorin et al., 2011].

Memory Consistency Models (MCMs) Specify rules and guarantees about the <u>ordering</u> and <u>visibility</u> of accesses to shared memory [Sorin et al., 2011].

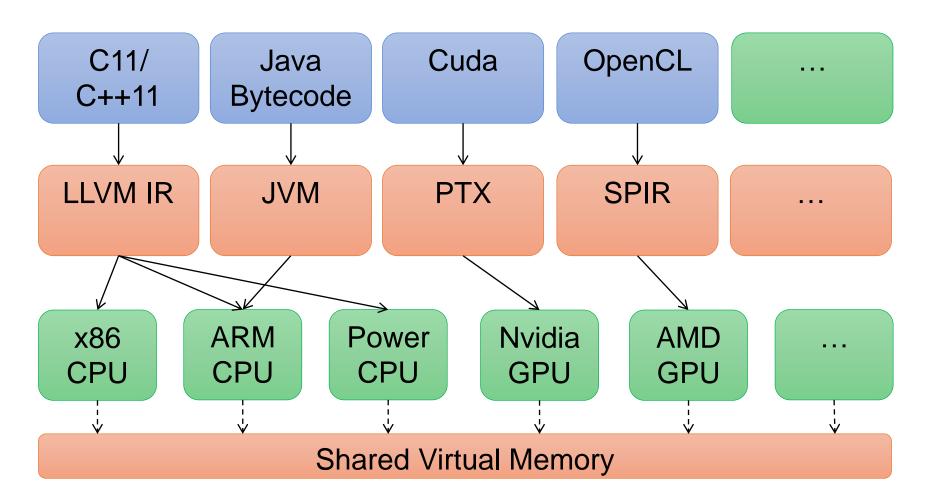

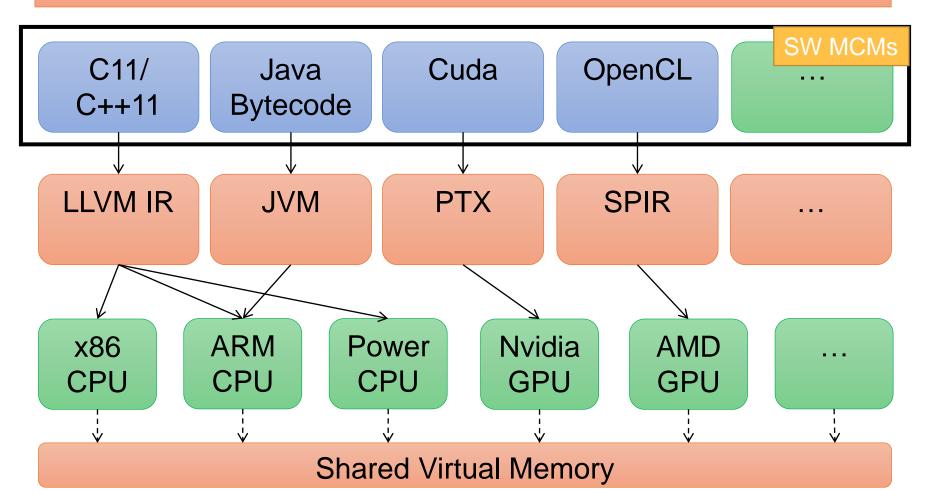

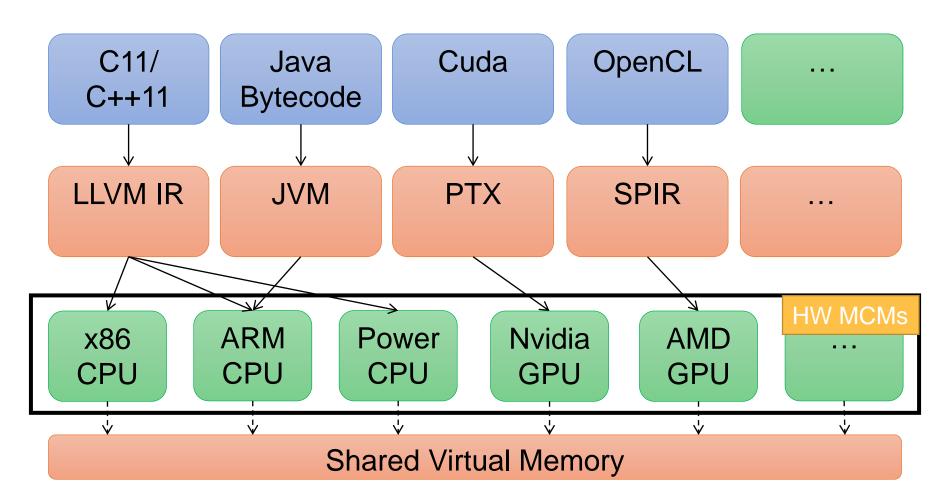

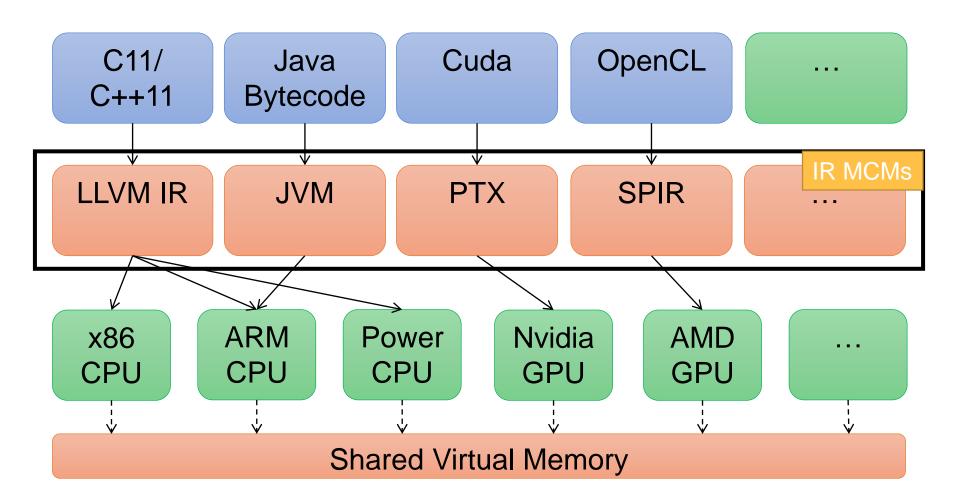

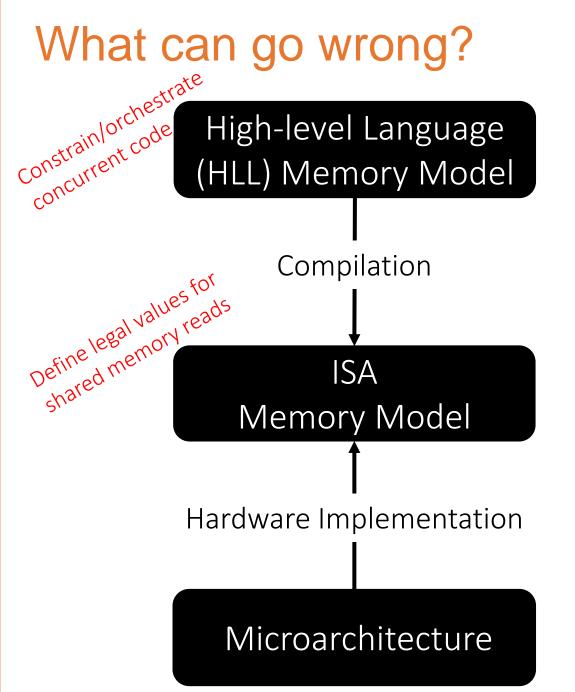

- A bug in any layer can cause a "correct" program to produce incorrect outcomes

- Ill-specified HLL memory model

- Incorrect HLL $\rightarrow$ ISA compilation

- Inadequate ISA specification

- Incorrect hardware implementation

- Benefits to verifying this stack as a whole

### Goals

- Ultimately want to write correct and efficient concurrent programs

- Concurrent programs are compiled and eventually run on hardware

- Hardware reorders instructions and state updates for performance

- Shared memory for inter-thread communication

- Memory Consistency Models (MCMs): govern inter-thread communication in the presence of shared memory

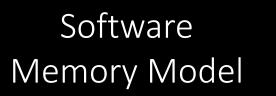

- Specified at the various layers of the hardware-software stack

- Require precise specifications, translations between layers

- MCM bugs anywhere in hardware-software stack can cause a "correct" high-level language program can produce incorrect results

## **Our Approach Today**

- Basic overview of MCMs

- Our suite of tools for MCM verification

- Hands-on verification examples

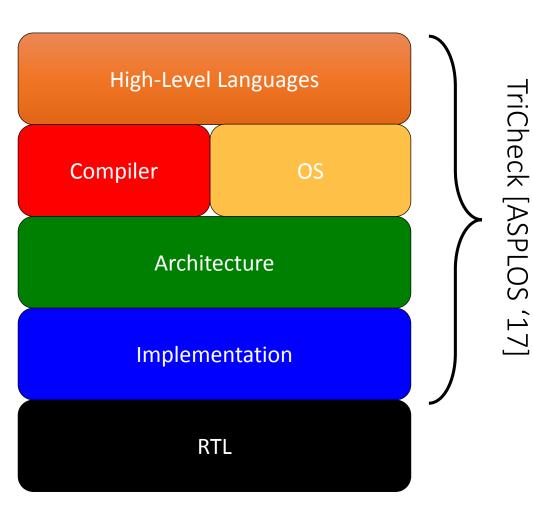

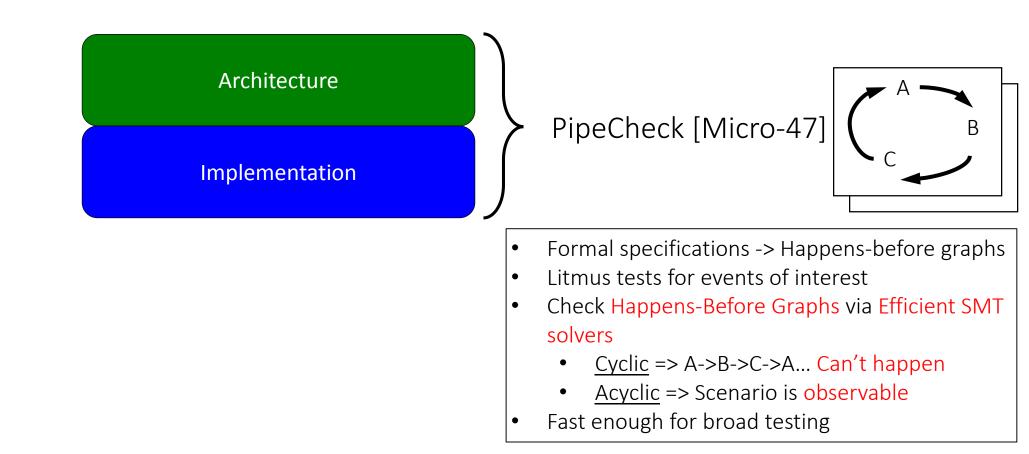

- PipeCheck: Verification of a HW design w.r.t. an ISA MCM specification

- **TriCheck:** Full-stack (HLL→Compiler→ISA→HW) MCM verification

- Provide you with a general modeling/verification approach that can be applied to other problem areas

## Outline

#### Introduction

- Motivating Example

- Overview of Our Work

- MCM Background & Our Approach

- PipeCheck: Verifying Hardware Implementations against ISA Specs

- Graph-based happens-before analysis of program executions on hardware

- µspec DSL for specifying axiomatic models of hardware

- TriCheck: Expanding to HW/SW Stack Interface Issues

- Looking forward: Other uses of tools and techniques

- CCICheck, COATCheck, SecurityCheck, ...

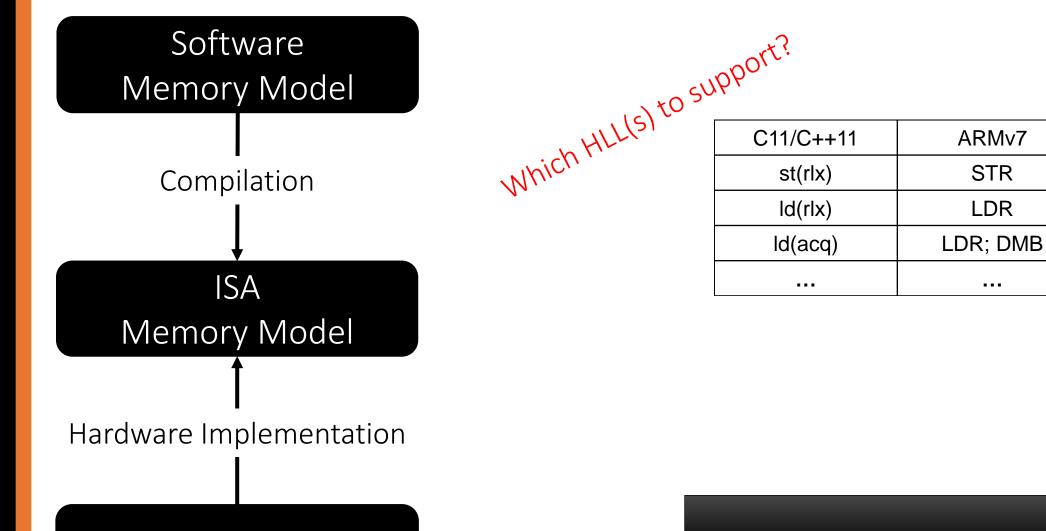

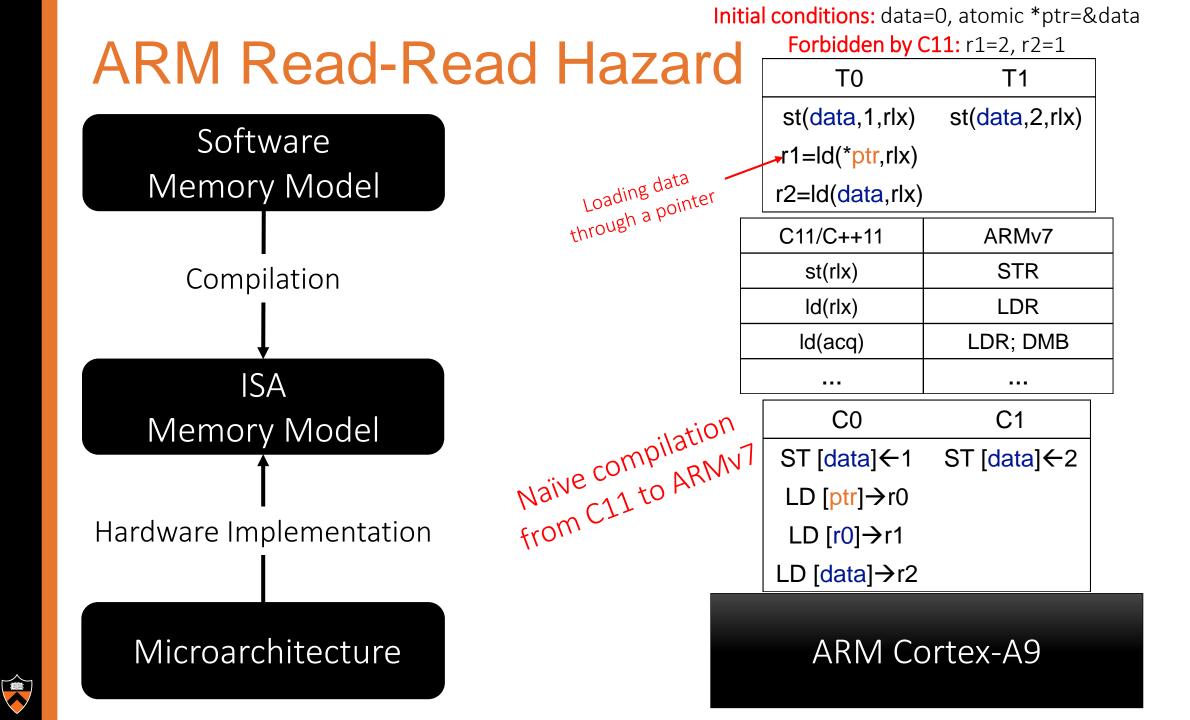

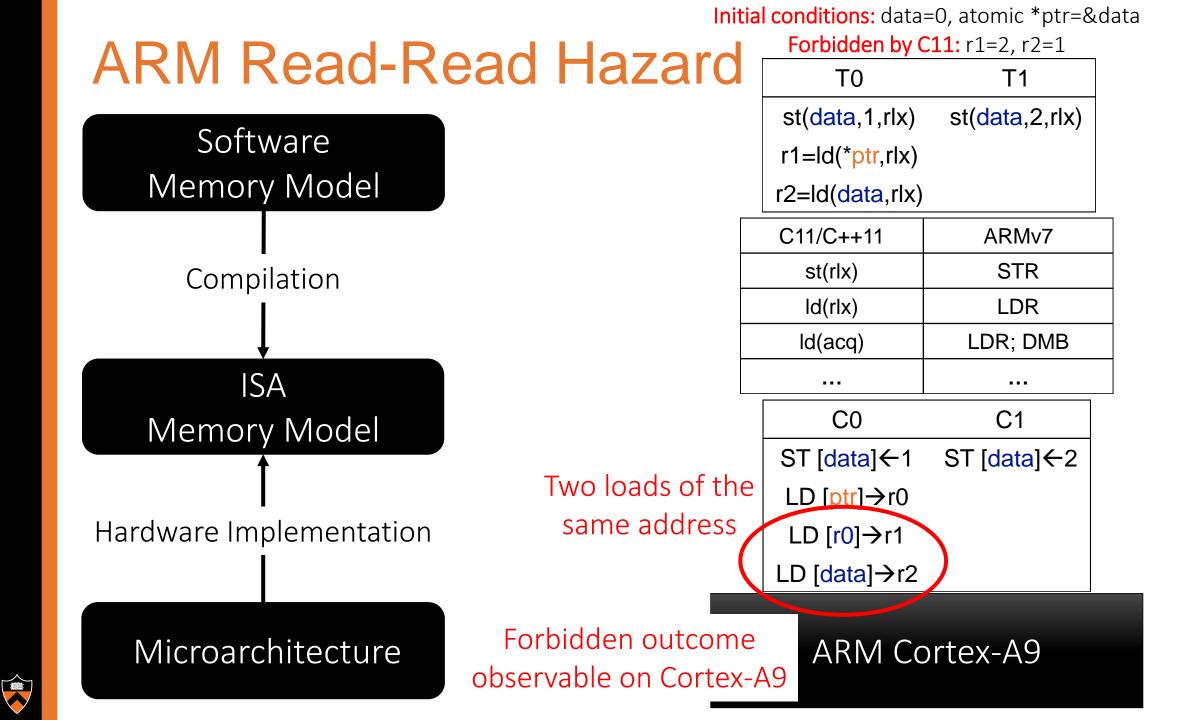

#### Motivating Example: ARM Read-after-Read Hazard

- ARM ISA spec ambiguous regarding same-address  $Ld \rightarrow Ld$  ordering:

- ARM compilers did not insert fences

- Some ARM implementations relax same-address Ld $\rightarrow$ Ld ordering

- C/C++ variables with atomic type require same-addr. Ld  $\rightarrow$  Ld ordering

- ARM issued errata1:

- Rewrite compilers to insert fences with performance penalties

- ARM had ordering instructions in ISA to guarantee correctness

<sup>1</sup>ARM. Cortex-A9 MPCore, programmer advice notice, read-after-read hazards. ARM Reference 761319., 2011. http://infocenter.arm.com/help/topic/com.arm.doc. uan0004a/UAN0004A\_a9\_read\_read.pdf.

Compilation

ISA Memory Model

Hardware Implementation

#### Microarchitecture

#### Microarchitecture

ARMv7

STR

LDR

...

### ARM Read-after-Read Hazard Demo Google Nexus 6 (Snapdragon 805)

```

std::atomic<int> z = {0};

std::atomic<int> *y = {&z};

void thread0()

{

z.store(1, std::memory_order_relaxed);

int r0 = y->load(std::memory_order_relaxed);

int r1 = z.load(std::memory_order_relaxed);

if(r0 != r1)

z.store(3, std::memory_order_relaxed);

}

void thread1()

{

z.store(2, std::memory_order_relaxed);

}

```

http://check.cs.princeton.edu/tutorial\_extras/SnapVideo.mov

## Outline

- Introduction

- Motivating Example

- Overview of Our Work

- MCM Background & Our Approach

- PipeCheck: Verifying Hardware Implementations against ISA Specs

- Graph-based happens-before analysis of program executions on hardware

- µspec DSL for specifying axiomatic models of hardware

- TriCheck: Expanding to HW/SW Stack Interface Issues

- Looking forward: Other uses of tools and techniques

- CCICheck, COATCheck, SecurityCheck, ...

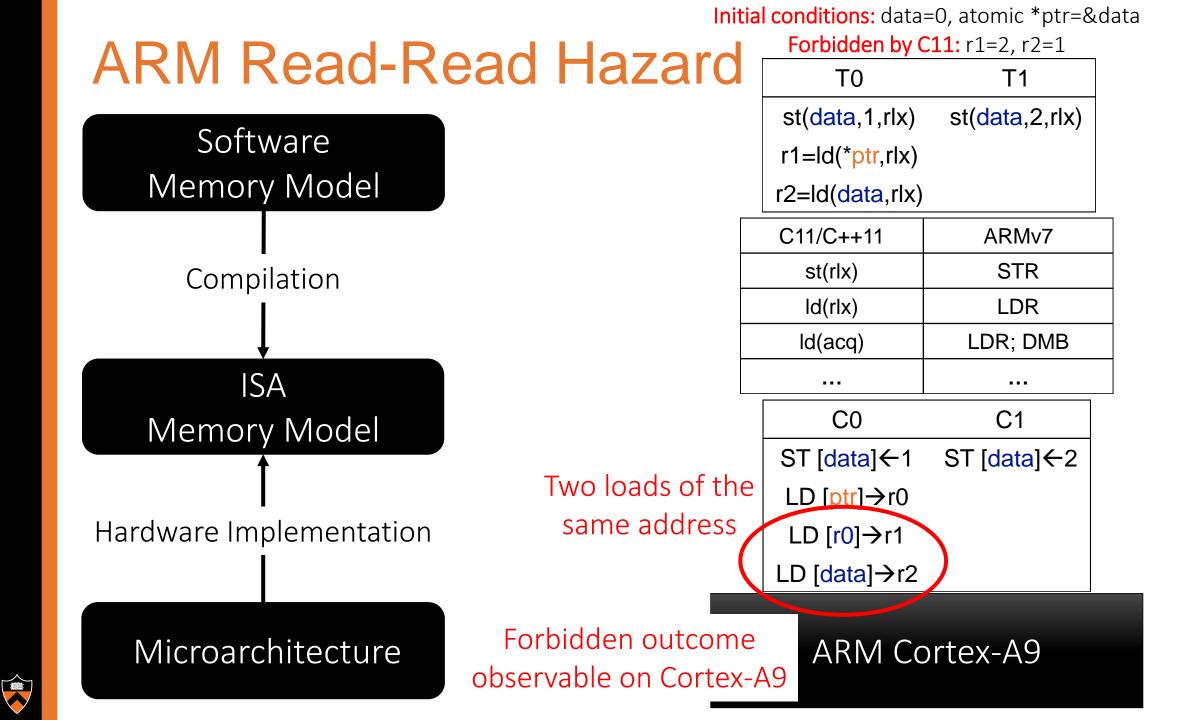

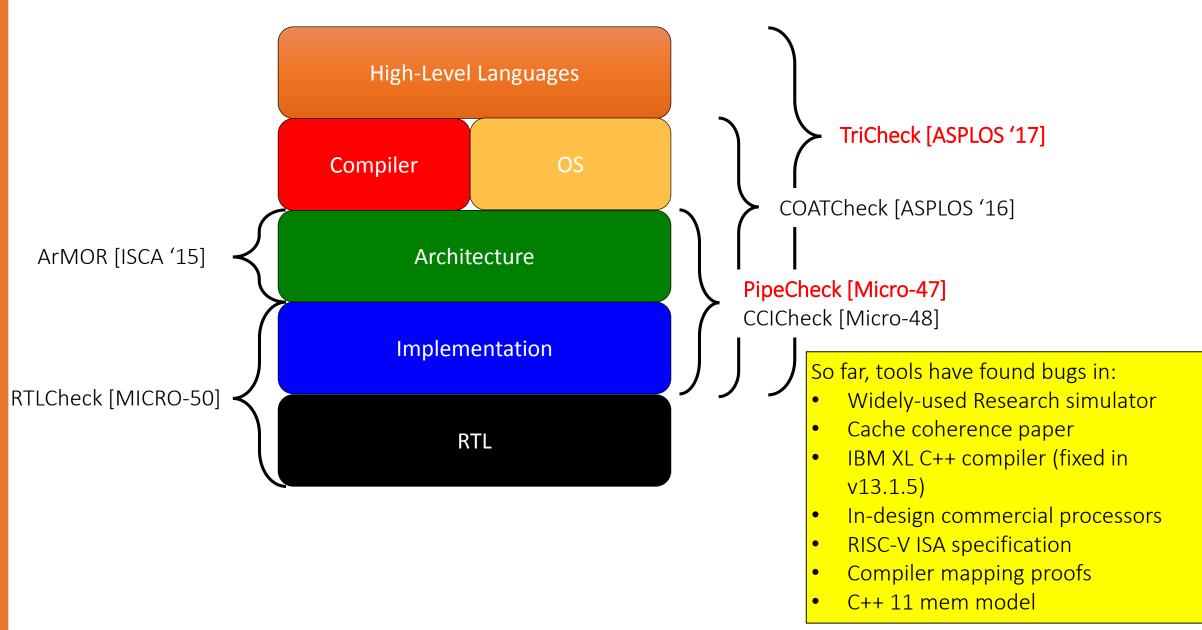

### **Benefits of Full-Stack Verification**

- Categorization & quantification of bugs in the HW-SW stack

- Effects of ISA MCM issues on the correctness of HLL programs

- Effects of desirable HW optimizations on ISA-HLL compatibility

- We have found real bugs:

- RISC-V MCM draft spec

- Compiler mappings from C11 to Power and ARMv7, leading to discovery of C11 MCM bug

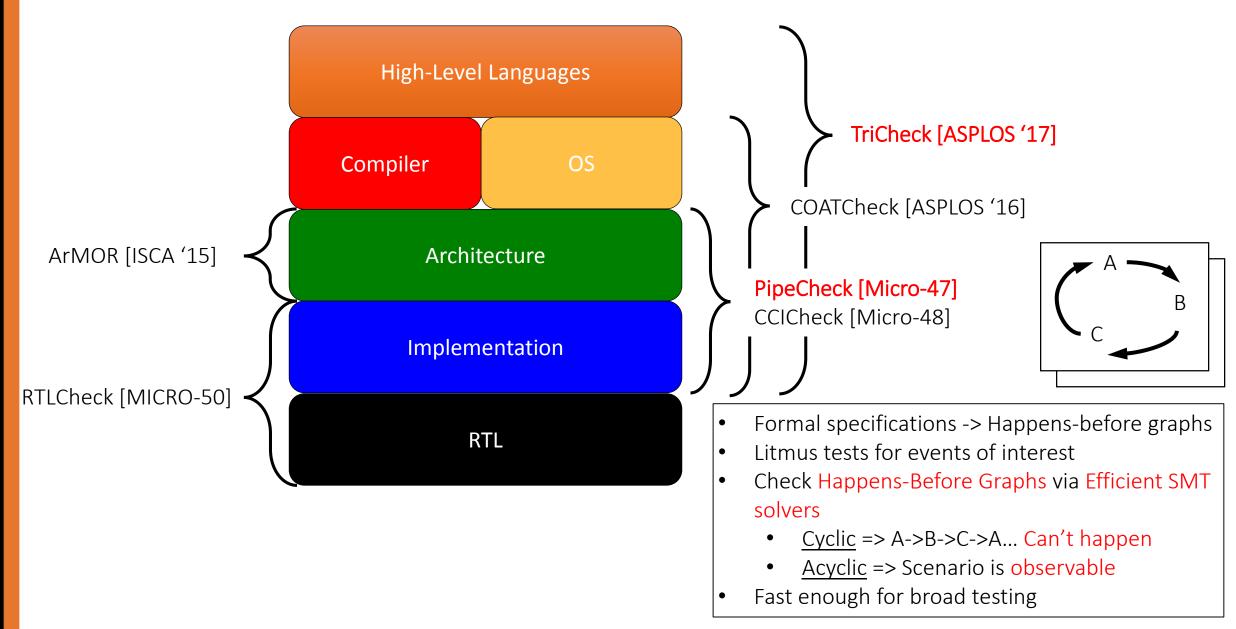

#### Full-Stack is the Result of a Whole Line of Work

#### Full Stack is the Result of a Whole Line of Work

#### Full Stack is the Result of a Whole Line of Work

## Outline

- Introduction

- Motivating Example

- Overview of Our Work

- MCM Background & Our Approach

- PipeCheck: Verifying Hardware Implementations against ISA Specs

- Graph-based happens-before analysis of program executions on hardware

- µspec DSL for specifying axiomatic models of hardware

- TriCheck: Expanding to HW/SW Stack Interface Issues

- Looking forward: Other uses of tools and techniques

- CCICheck, COATCheck, SecurityCheck, ...

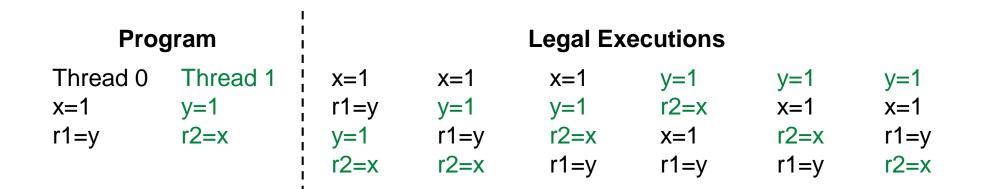

#### Sequential Consistency (SC)

Defined by [Lamport 1979], execution is the same as if: (R1) Memory ops of <u>each processor</u> appear in program order

(R2) Memory ops of <u>all processors</u> were executed in some global sequential order

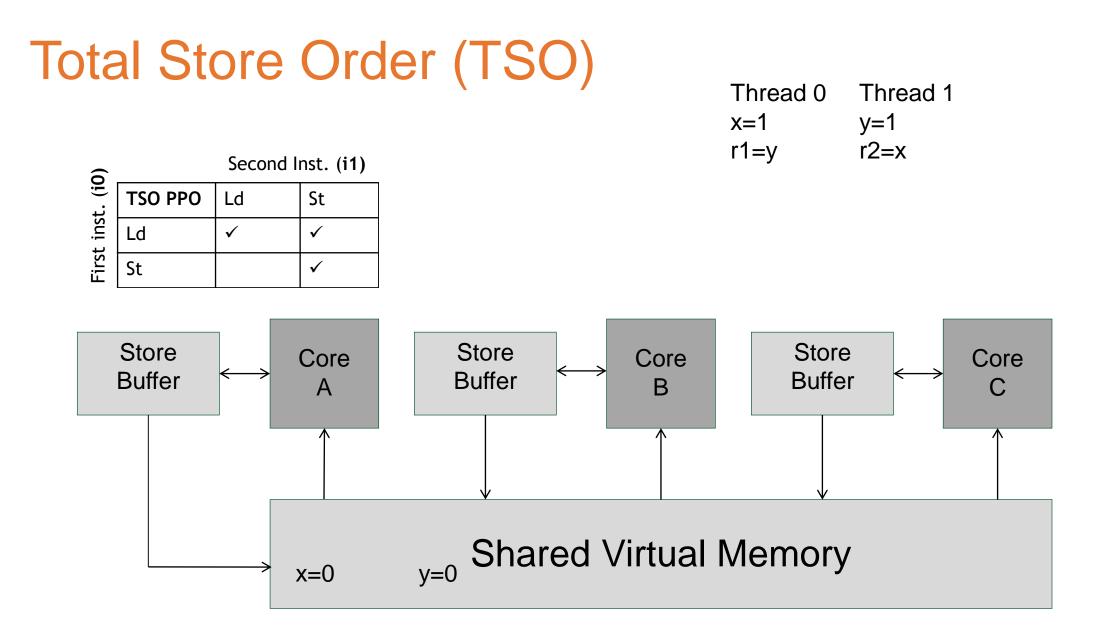

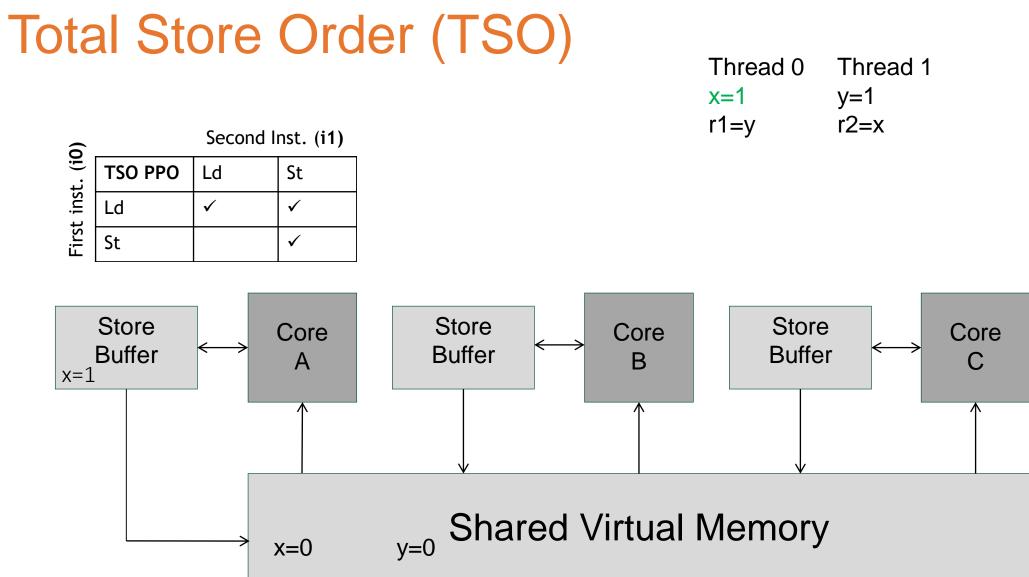

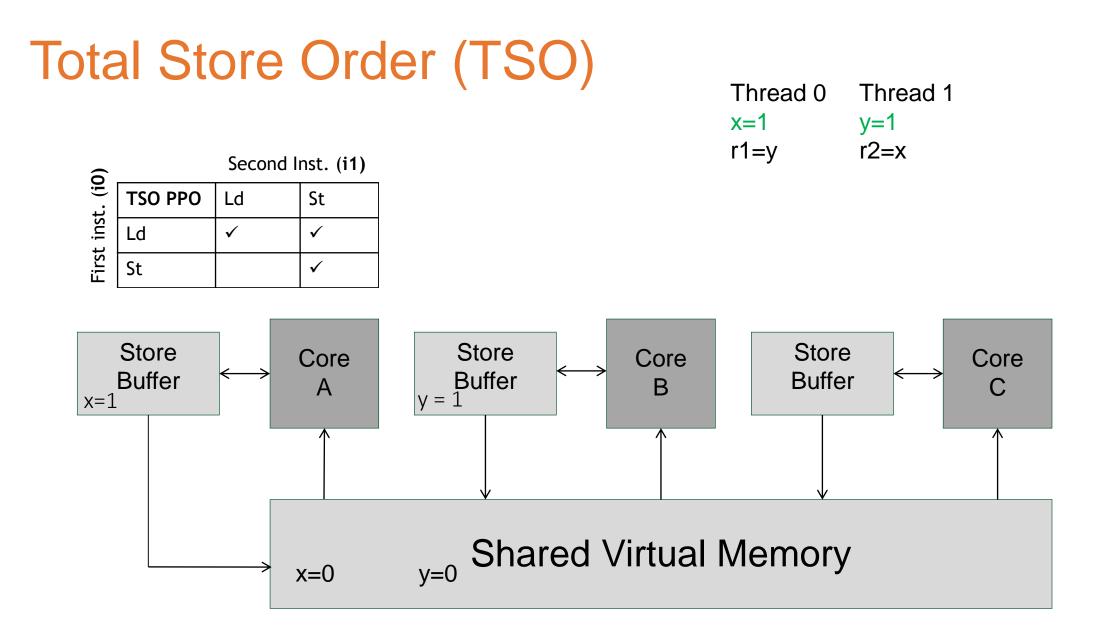

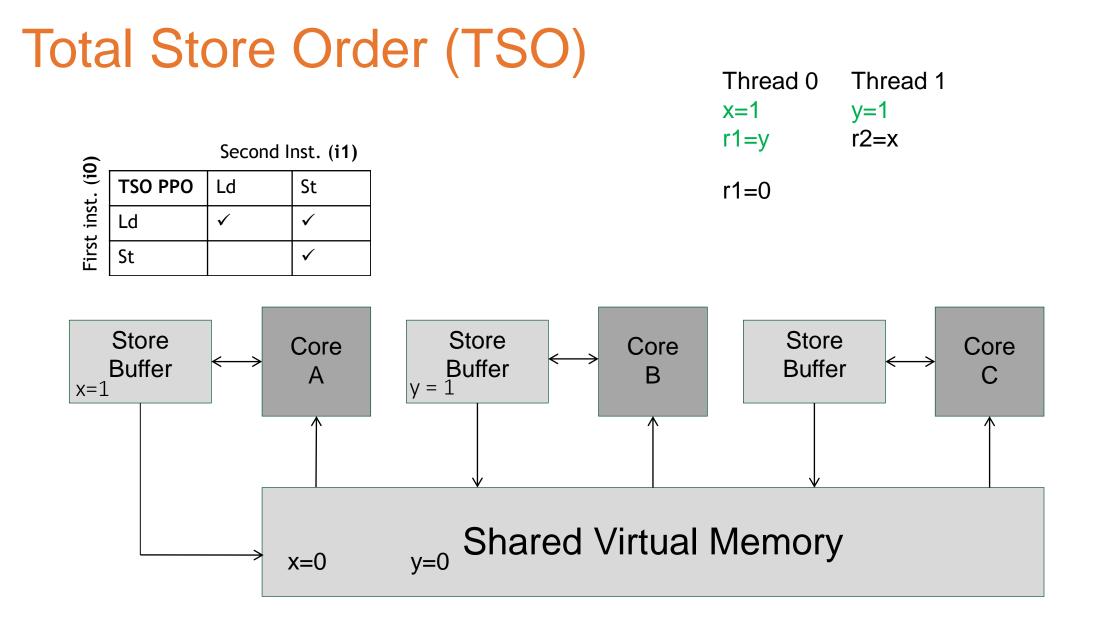

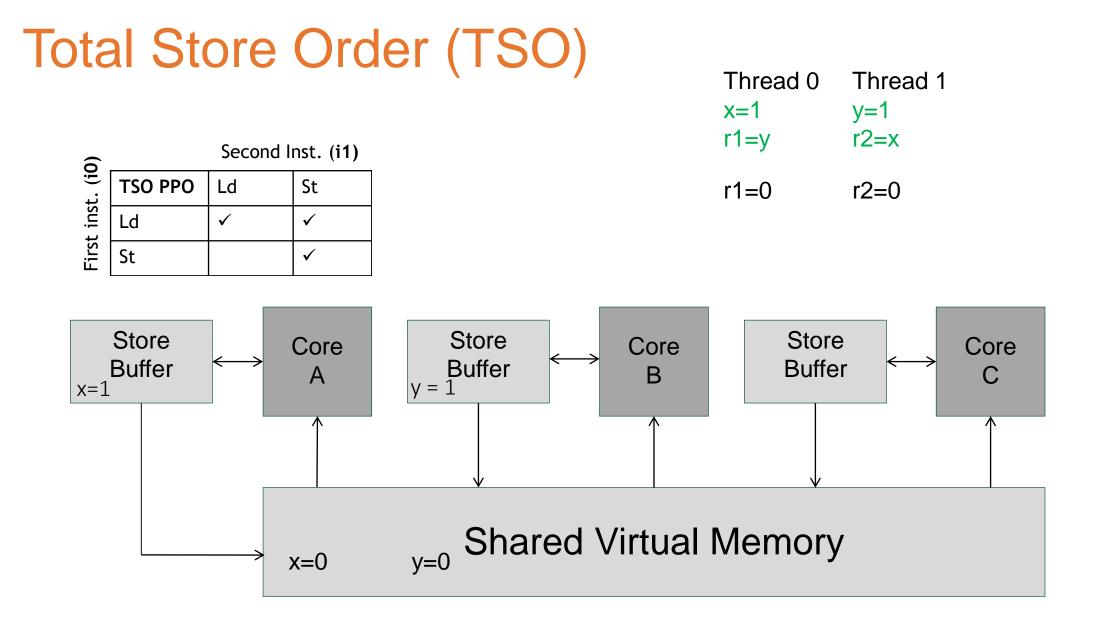

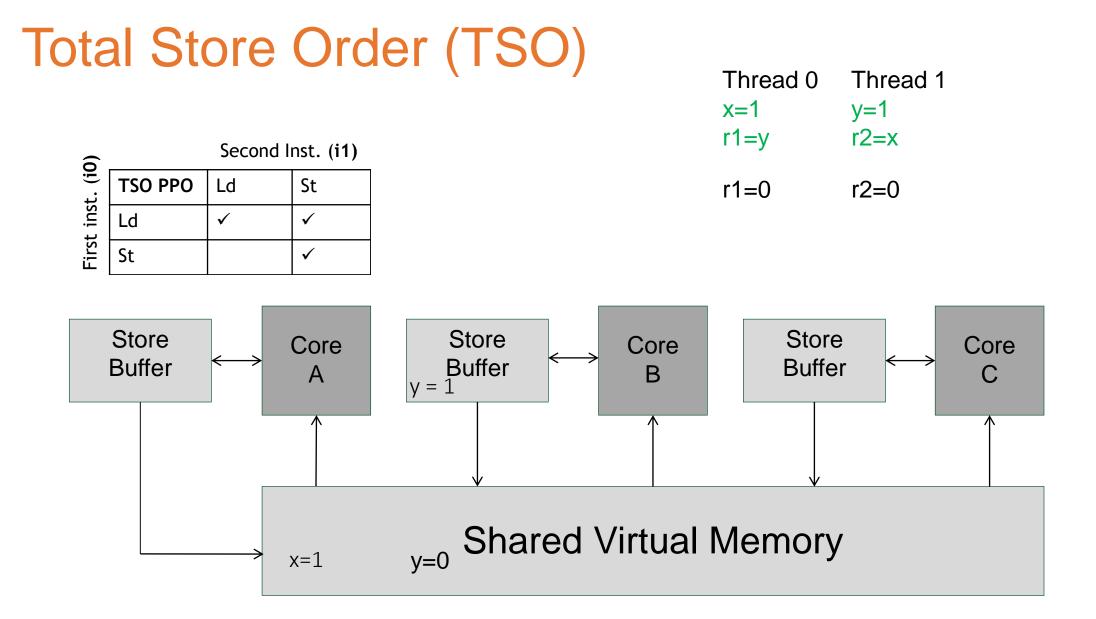

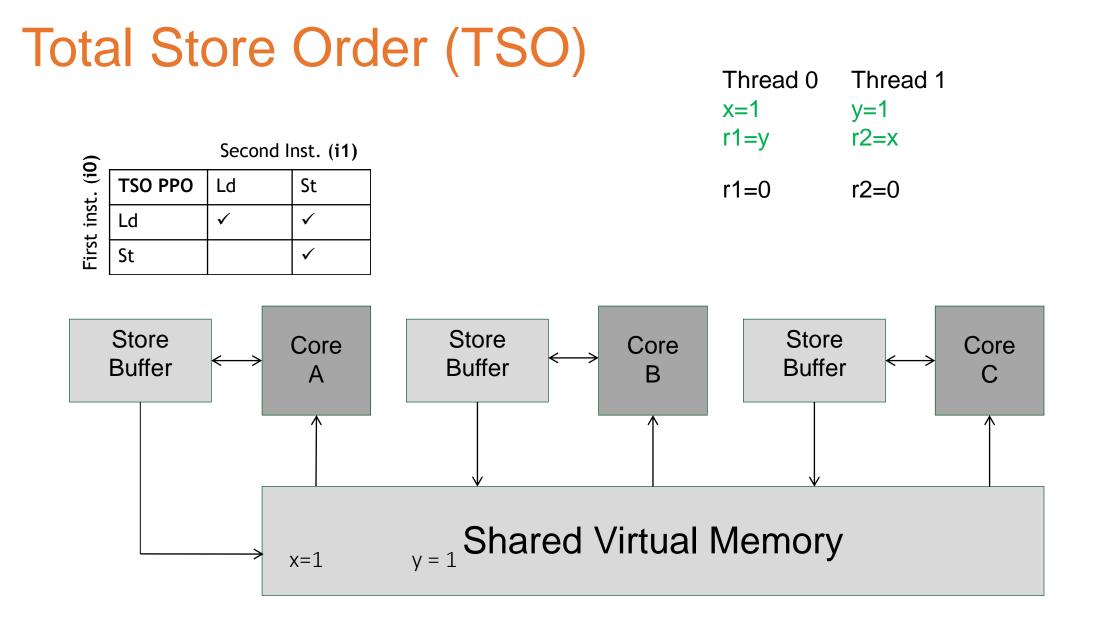

#### **Total Store Order**

Т

| Program                 |                         | Legal Executions           |                            |                            |                            |                            |                            |

|-------------------------|-------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

|                         |                         | x=1<br>r1=y<br>y=1<br>r2=x | x=1<br>y=1<br>r1=y<br>r2=x | x=1<br>y=1<br>r2=x<br>r1=y | y=1<br>r2=x<br>x=1<br>r1=y | y=1<br>x=1<br>r2=x<br>r1=y | y=1<br>x=1<br>r1=y<br>r2=x |

| Thread 0<br>x=1<br>r1=y | Thread 1<br>y=1<br>r2=x | r1=y<br>x=1<br>y=1<br>r2=x | r1=y<br>y=1<br>x=1<br>r2=x | r1=y<br>y=1<br>r2=x<br>x=1 | y=1<br>r2=x<br>r1=y<br>x=1 | y=1<br>r1=y<br>r2=x<br>x=1 | y=1<br>r1=y<br>x=1<br>r2=x |

|                         |                         | x=1<br>r1=y<br>r2=x<br>y=1 | x=1<br>r2=x<br>r1=y<br>y=1 | x=1<br>r2=x<br>y=1<br>r1=y | r2=x<br>y=1<br>x=1<br>r1=y | r2=x<br>x=1<br>y=1<br>r1=y | r2=x<br>x=1<br>r1=y<br>y=1 |

|                         |                         | r1=y<br>x=1<br>r2=x<br>y=1 | r1=y<br>r2=x<br>x=1<br>y=1 | r1=y<br>r2=x<br>y=1<br>x=1 | r2=x<br>y=1<br>r1=y<br>x=1 | r2=x<br>r1=y<br>y=1<br>x=1 | r2=x<br>r1=y<br>x=1<br>y=1 |

# Memory Consistency Models: Critical ISA & System Component

#### 8.2.2 Memory Ordering in P6 and More Recent Processor Families

The Intel Core 2 Duo, Intel Atom, Intel Core Duo, Pentium 4, and P6 family processors also use a processor-ordered memory-ordering model that can be further defined as "write ordered with store-buffer forwarding." This model can be characterized as follows.

In a single-processor system for memory regions defined as write-back cacheable, the memory-ordering model respects the following principles (**Note** the memory-ordering principles for single-processor and multiple-processor systems are written from the perspective of software executing on the processor, where the term "processor" refers to a logical processor. For example, a physical processor supporting multiple cores and/or HyperThreading Technology is treated as a multi-processor systems.):

- Reads are not reordered with other reads.

- Writes are not reordered with older reads.

- Writes to memory are not reordered with other writes, with the following exceptions:

- writes executed with the CLFLUSH instruction;

- streaming stores (writes) executed with the non-temporal move instructions (MOVNTI, MOVNTQ, MOVNTDQ, MOVNTPS, and MOVNTPD); and

- string operations (see Section 8.2.4.1).

- Reads may be reordered with older writes to different locations but not with older writes to the same location.

# Memory Consistency Models: Critical ISA & System Component

#### 8.2.2 Memory Ordering in P6 and More Recent Processor Families

The Intel Core 2 Duo, Intel Atom, Intel Core Duo, Pentium 4, and P6 family processors also use a processor-ordered memory-ordering model that can be further defined as "write ordered with store-buffer forwarding." This model can be characterized as follows.

In a single-processor system for memory regions defined as write-back cacheable. the memory-ordering model

respects the following principles (**Note** the me processor systems are written from the perspe "processor" refers to a logical processor. For ex HyperThreading Technology is treated as a mu

- Reads are not reordered with other reads.

- Writes are not reordered with older reads.

- Writes to memory are not reordered with o

- writes executed with the CLFLUSH instr

- streaming stores (writes) executed with MOVNTDQ, MOVNTPS, and MOVNTPD);

- string operations (see Section 8.2.4.1).

- Type A Type B (second) (first) **Load Store Load**

- Reads may be reordered with older writes to different locations but not with older writes to the same location.

#### Memory Consistency Models: Critical ISA & System Component

In a nutshell: MCMs are part of the ISA They are the spec of what value will be returned

Rest of the software stack expects them to be when your program does a load

•

•

Re

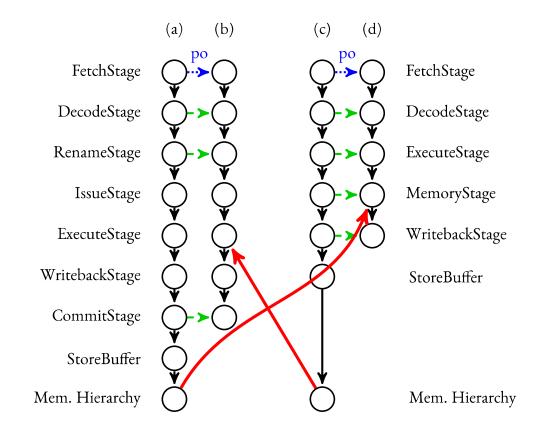

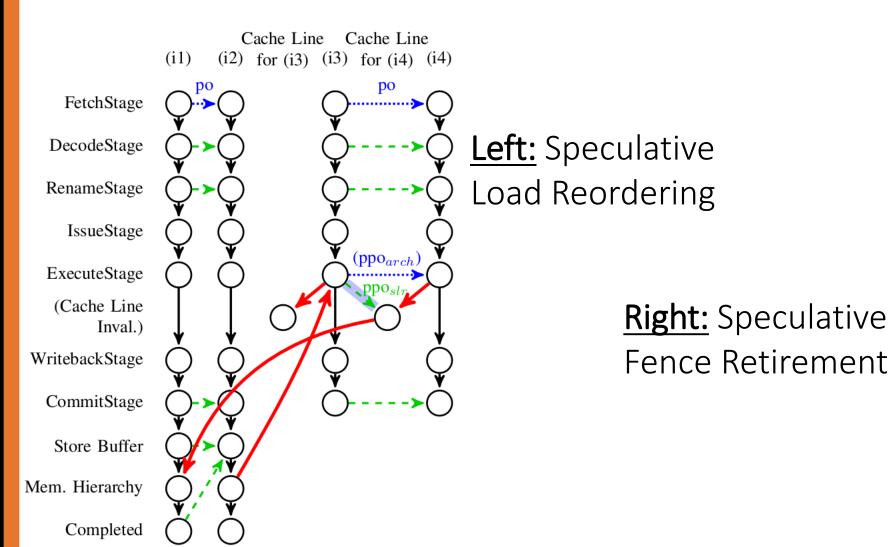

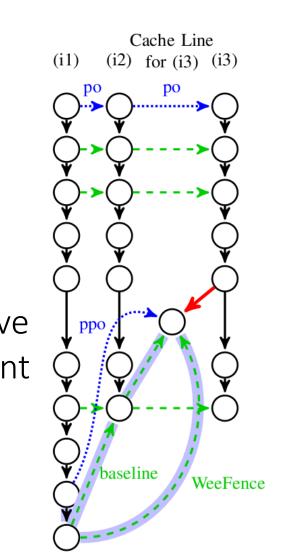

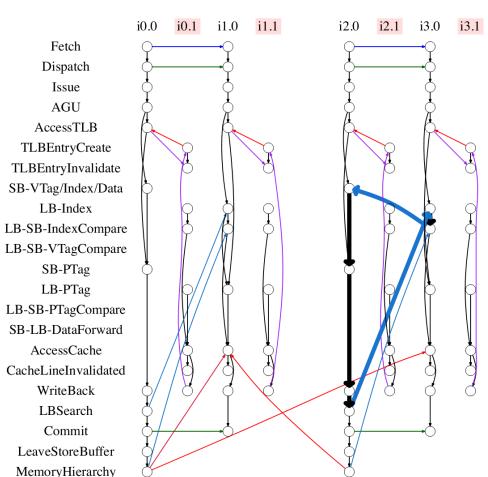

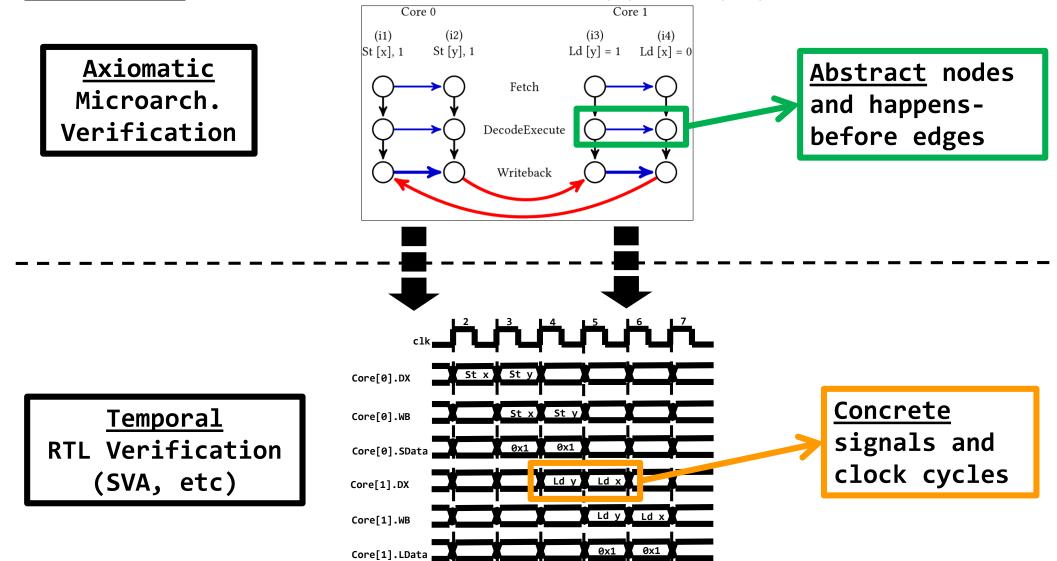

#### **Microarchitectural Consistency Verification**

- Microarch. enforces ISA-level MCM through many small orderings

- In-order fetch/commit

- FIFO store buffers

- Coherence protocol

- Difficult to ensure that these orderings *always* enforce the required orderings

Designs may also be complicated by optimizations (speculative load reordering, early fence retirement, OoO execution), or novel organization (heterogeneity)

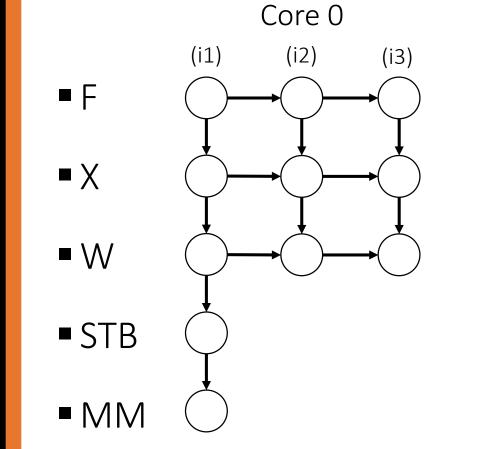

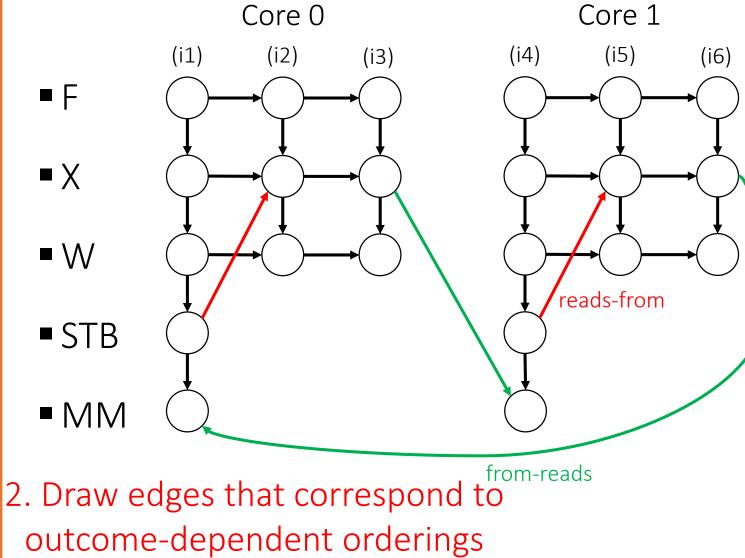

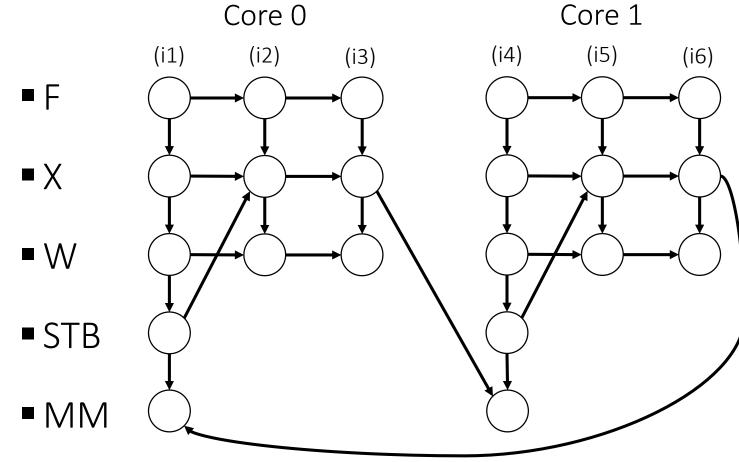

### Our approach: "microarchitecturally happens-before" (µhb) graphs

(i4)

1. Draw edges that correspond to outcome-independent orderings

| Core 1    | Initially:                                              | Initially: [x]=[y]=0                                    |  |  |  |

|-----------|---------------------------------------------------------|---------------------------------------------------------|--|--|--|

| (i5) (i6) | Core 0                                                  | Core 1                                                  |  |  |  |

|           | (i1) st [x] ← 1<br>(i2) ld [x] → r1<br>(i3) ld [y] → r2 | (i4) st [y] ← 1<br>(i5) ld [y] → r3<br>(i6) ld [x] → r4 |  |  |  |

|           | Program outcome of inter<br>r1=1, r2=0, r3=1, and r4    |                                                         |  |  |  |

|           | Key Idea: Mode<br>programs on HV                        |                                                         |  |  |  |

executions of ograms on HW as µhb graphs

(i5) Id [y]  $\rightarrow$  r3

(i6) Id  $[x] \rightarrow r4$

- Nodes: Microarchitectural events in an execution

- Edges: Happens-before relationships between nodes

# Our approach: "microarchitecturally happens-before" (µhb) graphs

| Initially: [x]=[y]=0                                       |                                                         |  |

|------------------------------------------------------------|---------------------------------------------------------|--|

| Core 0                                                     | Core 1                                                  |  |

| (i1) st [x] ← 1<br>(i2) ld [x] → r1<br>(i3) ld [y] → r2    | (i4) st [y] ← 1<br>(i5) ld [y] → r3<br>(i6) ld [x] → r4 |  |

| Program outcome of interest:<br>r1=1, r2=0, r3=1, and r4=0 |                                                         |  |

Key Idea: Model executions of programs on HW as **µhb graphs**

- Nodes: Microarchitectural events in an execution

- Edges: Happens-before relationships between nodes

# Our approach: "microarchitecturally happens-before" (µhb) graphs

No cycle in graph, so program outcome is observable!

| Initially: [x]=[y]=0                                       |                                                         |  |

|------------------------------------------------------------|---------------------------------------------------------|--|

| Core 0                                                     | Core 1                                                  |  |

| (i1) st [x] ← 1<br>(i2) ld [x] → r1<br>(i3) ld [y] → r2    | (i4) st [y] ← 1<br>(i5) ld [y] → r3<br>(i6) ld [x] → r4 |  |

| Program outcome of interest:<br>r1=1, r2=0, r3=1, and r4=0 |                                                         |  |

Key Idea: Model executions of programs on HW as **µhb graphs**

- Nodes: Microarchitectural events in an execution

- Edges: Happens-before relationships between nodes

# Litmus test verification

- Litmus tests small parallel programs

- Used to highlight memory model differences/features

- Typically there is one non-SC outcome of interest

- Different litmus tests associated with different ISA models

- ISA memory model often characterized by their Permitted and Forbidden non-SC litmus test outcomes

- TSO litmus test suite, Power litmus test suite, ARM litmus test suite

- Why litmus test verification?

- Higher performance when evaluating complex designs

- Enables us to have a fast, iterative design process

- Focus on verification cases most likely to exhibit bugs

#### Litmus test verification (for TSO) Many litmus tests have been developed over the years; they have names e.g., MP, SB Initial conditions are all O unless otherwise stated MP litmus test This tutorial: we use a sprinkling of established tests Message Passing (MP) Message Passing (MP) Message Passing (MP) Message Passing (MP) Mo etecutions PO Ρ1 PO Ρ1 PO Ρ1 Ρ1 PO $W x \leftarrow 1$ $R y \rightarrow 1$ $W x \leftarrow 1 \quad R y \rightarrow 1$ $W x \leftarrow 1 R y \rightarrow 0$ $W \times \leftarrow 1$ $R \times \rightarrow 0$ $R x \rightarrow 0$ W y 🗲 1 ₩ v**¥** 1 W v **V** − 1 $W \sqrt{4} \leftarrow 1$ **R** x → 1 Non-SC Outcome SC Outcome Permitted Forbidden SC Outcome Permitted SC Outcome Permitted SB litmus test Store Buffering (SB) S& etecutions Store Buffering (SB) Store Buffering (SB) Store Buffering (SB) PO Ρ1 Ρ1 PO Ρ1 Ρ1 PO PO $W \times \leftarrow 1 \quad \forall y \leftarrow 1$ $W \times \leftarrow 1$ $\downarrow W \vee \leftarrow 1$ $W \times \leftarrow 1$ W x ← 1 $Wy \leftarrow 1$ $Ry \rightarrow 0$ $R \times \rightarrow 0$ $R_V \rightarrow 0$ ¶x → 1 $Ry \rightarrow 1$ $Rv \rightarrow 1$ `R x → 1 $\mathbf{R} \times \rightarrow \mathbf{0}$ Non-SC Outcome SC Outcome Permitted SC Outcome Permitted SC Outcome Permitted Permitted

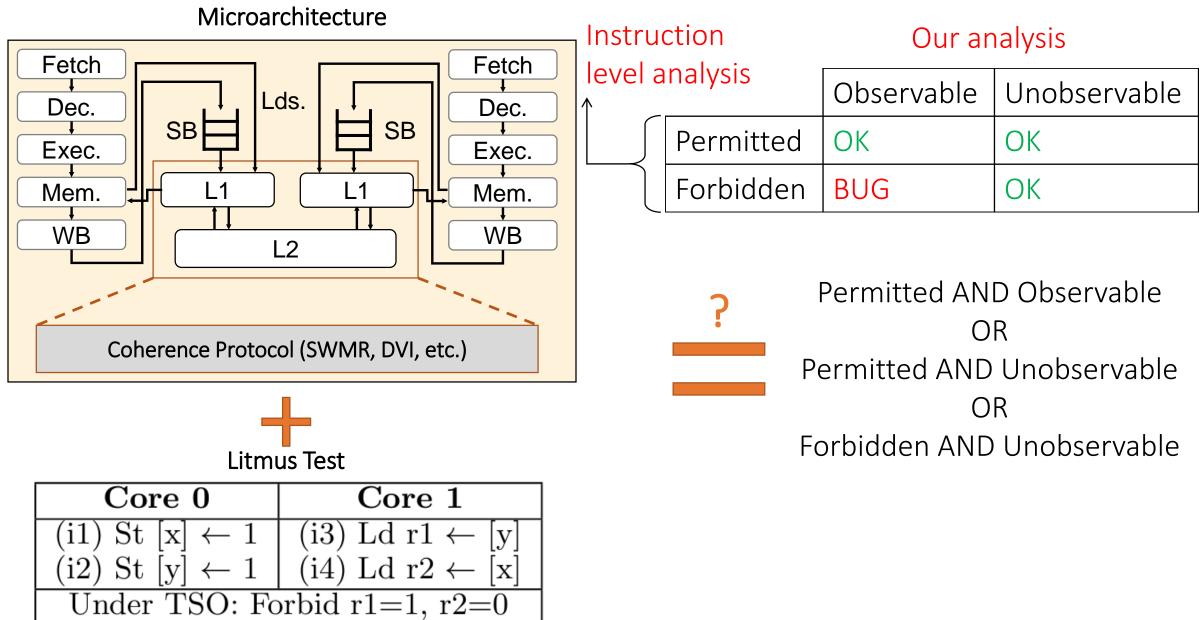

#### **Compare ISA Executions with Hardware Executions**

#### • At the <u>ISA level</u> a litmus test outcome can be:

- Permitted

- Forbidden

#### • Our approach: At the <u>hardware level</u> a litmus test outcome can be:

- Observable

- Unobservable

What ISA level

What our hardware-level analysis tells us

analysis tells us Observable Unobservable Permitted OK OK (Stricter than necessary) Forbidden BUG OK

#### Does hardware correctly implement memory model?

#### Check Inputs: Microarchitecture Spec + Litmus Tests Microarchitecture Specification in µspec DSL

```

Axiom "PO_Fetch":

forall microops "i1",

forall microops "i2",

SameCore i1 i2 /\ ProgramOrder i1 i2 =>

AddEdge ((i1, Fetch), (i2, Fetch), "PO").

Axiom "Execute_stage_is_in_order":

forall microops "i1",

forall microops "i2",

SameCore i1 i2 /\

EdgeExists ((i1, Fetch), (i2, Fetch)) =>

AddEdge ((i1, Execute), (i2, Execute), "PPO").

```

Litmus Test

| Core 0                       | Core 1                      |

|------------------------------|-----------------------------|

| (i1) St [x] $\leftarrow 1$   | (i3) Ld r1 $\leftarrow$ [y] |

| (i2) St [y] $\leftarrow 1$   | (i4) Ld r2 $\leftarrow$ [x] |

| Under TSO: Forbid r1=1, r2=0 |                             |

Refer to <u>Quick Start Guide</u> for more information on the µSpec DSL and how to write axioms.

> Permitted AND Observable OR Permitted AND Unobservable OR Forbidden AND Unobservable

#### Check Inputs: Microarchitecture Spec + Litmus Tests Microarchitecture Specification in µSpec DSL Axiom "PO\_Fetch": forall microops "i1", forall microops "i2", SameCore i1 i2 /\ ProgramOrder i1 i2 => AddEdge ((i1, Fetch), (i2, Fetch), "PO").

```

Axiom "Execute_stage_is_in_order":

forall microops "i1",

forall microops "i2",

SameCore i1 i2 /\

EdgeExists ((i1, Fetch), (i2, Fetch)) =>

AddEdge ((i1, Execute), (i2, Execute), "PPO").

```

#### Litmus Test

| Core 0                       | Core 1                      |

|------------------------------|-----------------------------|

| (i1) St [x] $\leftarrow 1$   | (i3) Ld r1 $\leftarrow$ [y] |

| (i2) St [y] $\leftarrow 1$   | (i4) Ld r2 $\leftarrow$ [x] |

| Under TSO: Forbid r1=1, r2=0 |                             |

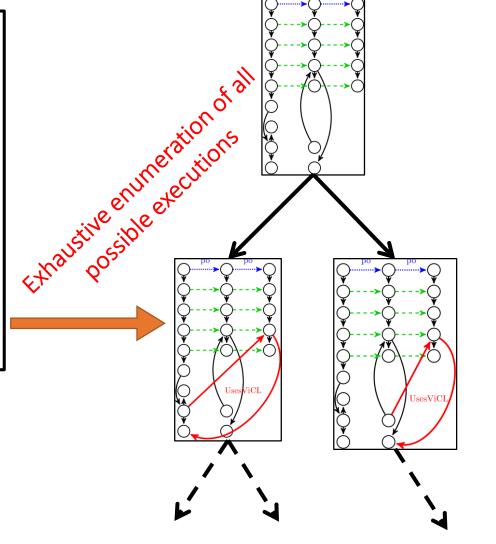

Microarchitectural happens-before ( $\mu$ hb) graphs

# In a nutshell, our tool philosophy...

- Automate specification, verification, and translation related to MCMs

- Comprehensive exploration of ordering possibilities

- Key Techniques: Happens-before Graphs and SMT solvers

- Bounded, litmus-test driven verificatiom

- We have other related techniques for whole-program, more comprehensive design analysis

- And we have templates to assist in the automatic generation of "families" of litmus tests

- Verification conducted on and axiomatic model of hardware

- We have tools for verifying this model is representative of real RTL

# Outline

- Introduction

- Motivating Example

- Overview of Our Work

- MCM Background & Our Approach

- PipeCheck: Verifying Hardware Implementations against ISA Specs

- Graph-based happens-before analysis of program executions on hardware

- µspec DSL for specifying axiomatic models of hardware

- TriCheck: Expanding to HW/SW Stack Interface Issues

- Looking forward: Other uses of tools and techniques

- CCICheck, COATCheck, SecurityCheck, ...

#### Overview

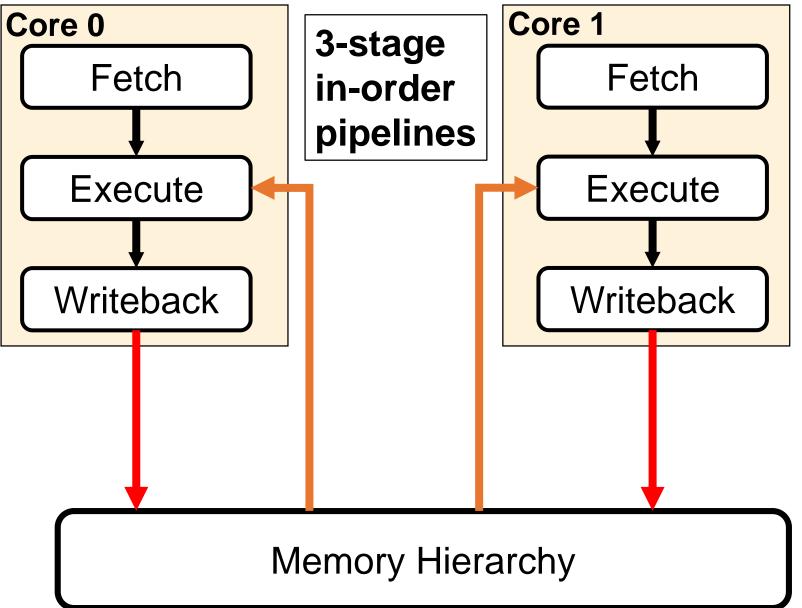

- Modelling simple microarchitectures (µarches) in µSpec

- Give you a taste of what  $\mu \text{Spec}$  can model and reason about

- Begin by modelling a SC µarch

- Partially completed µarch in VM, you will fill in remainder

- Post-coffee break, will look at expanding this SC μarch to TSO

- Store buffers

- Reading own write early (time permitting)

- Fences (time permitting)

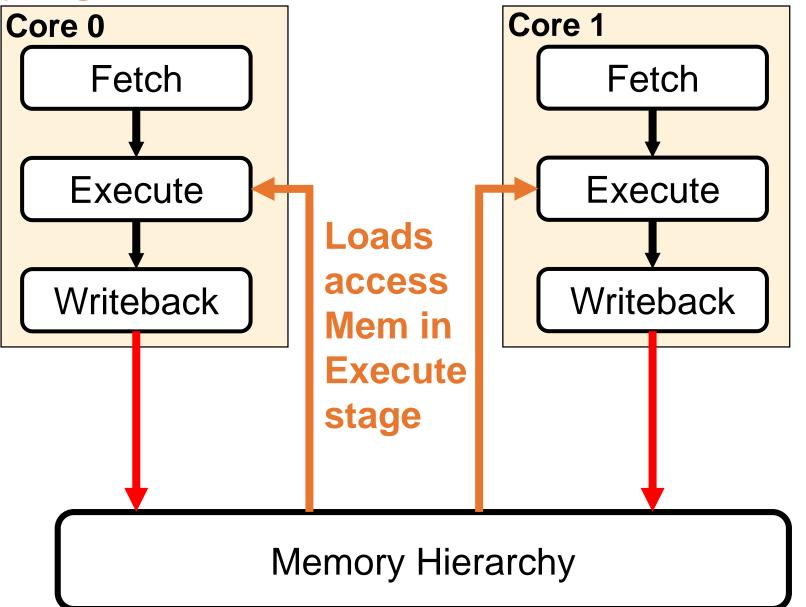

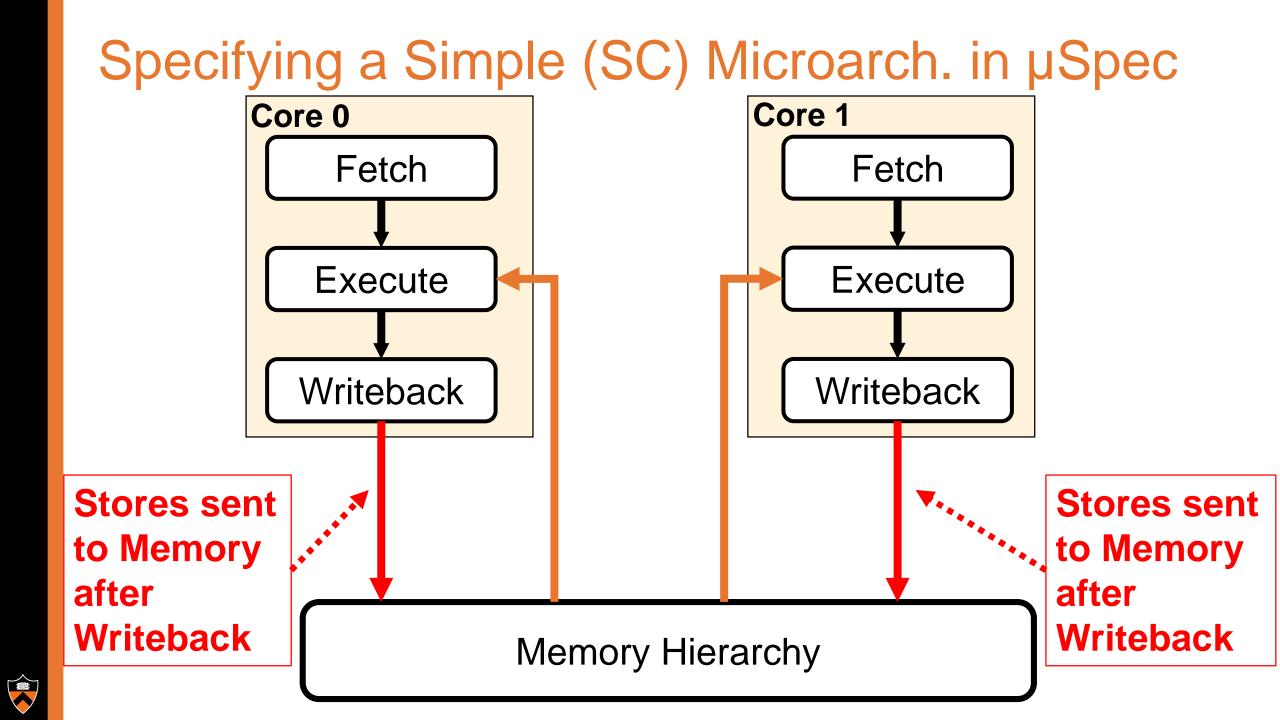

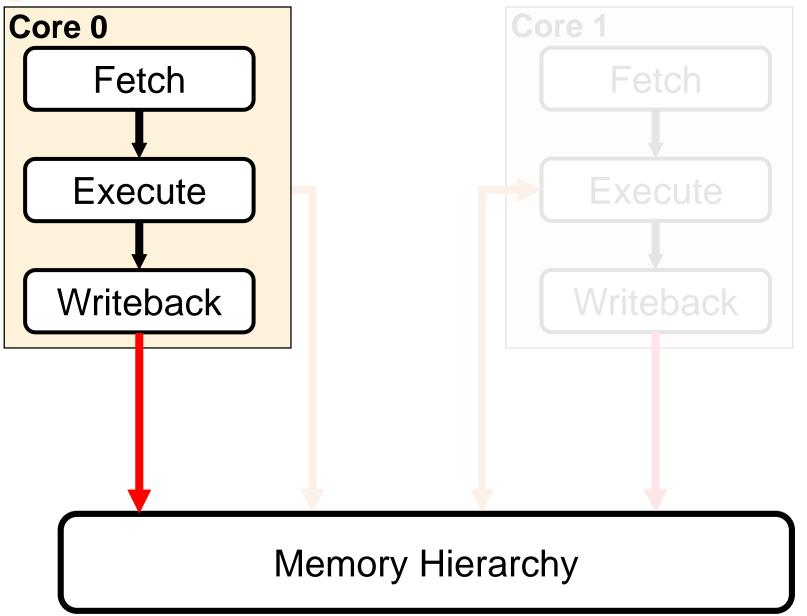

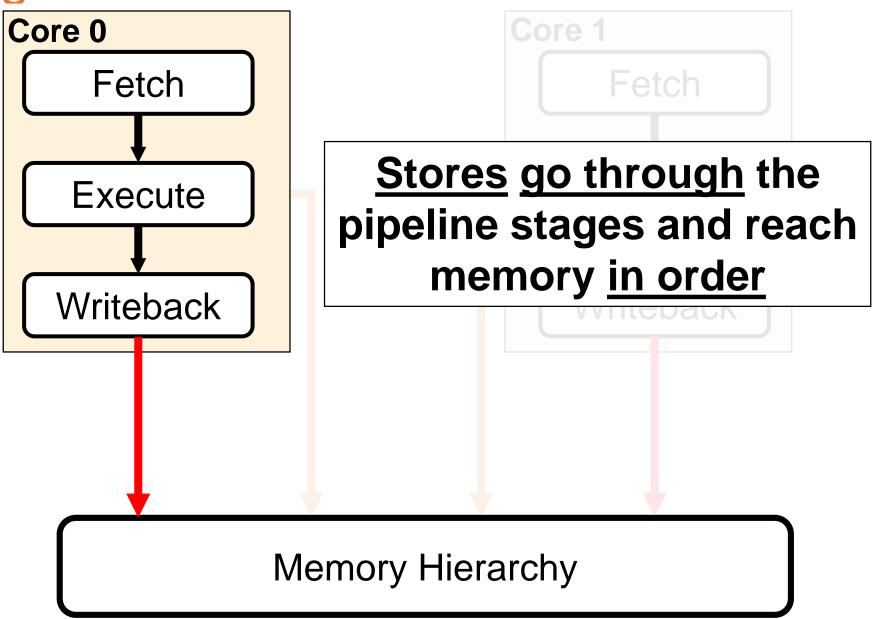

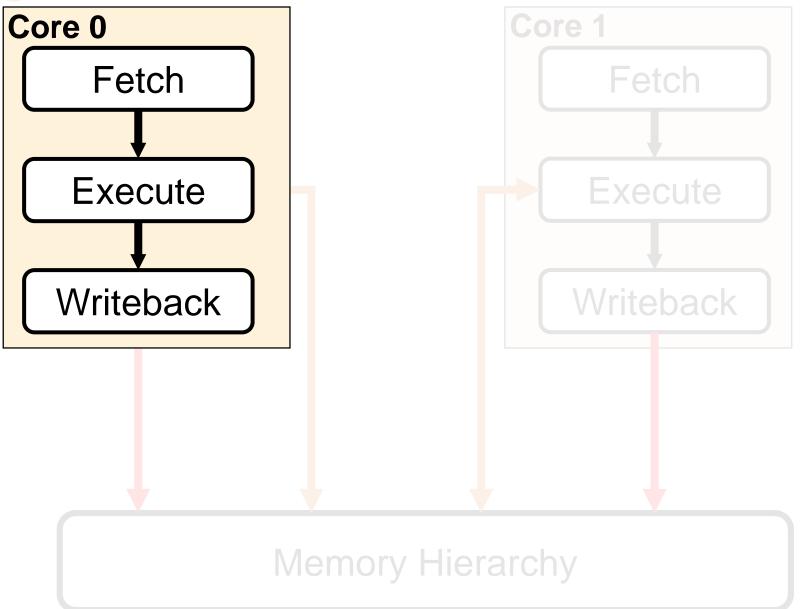

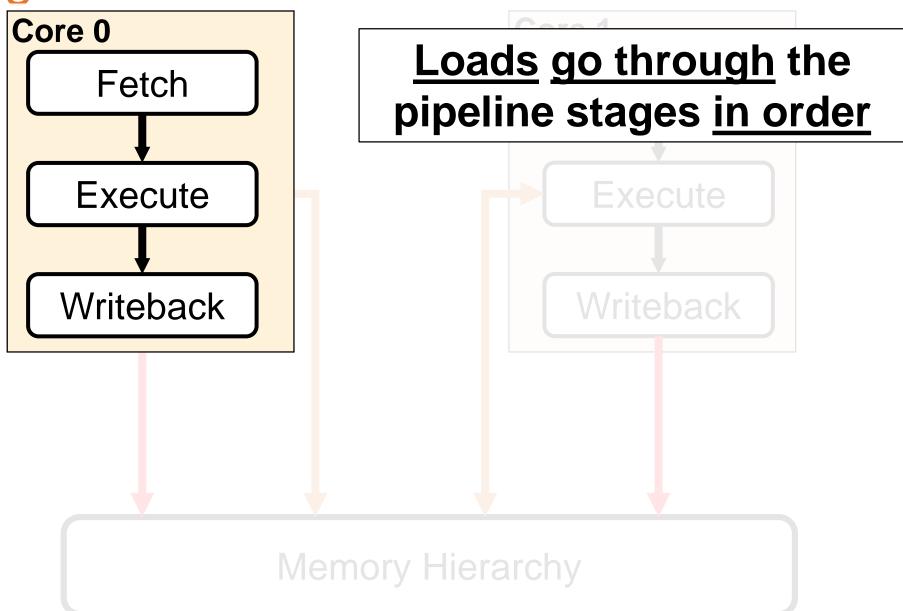

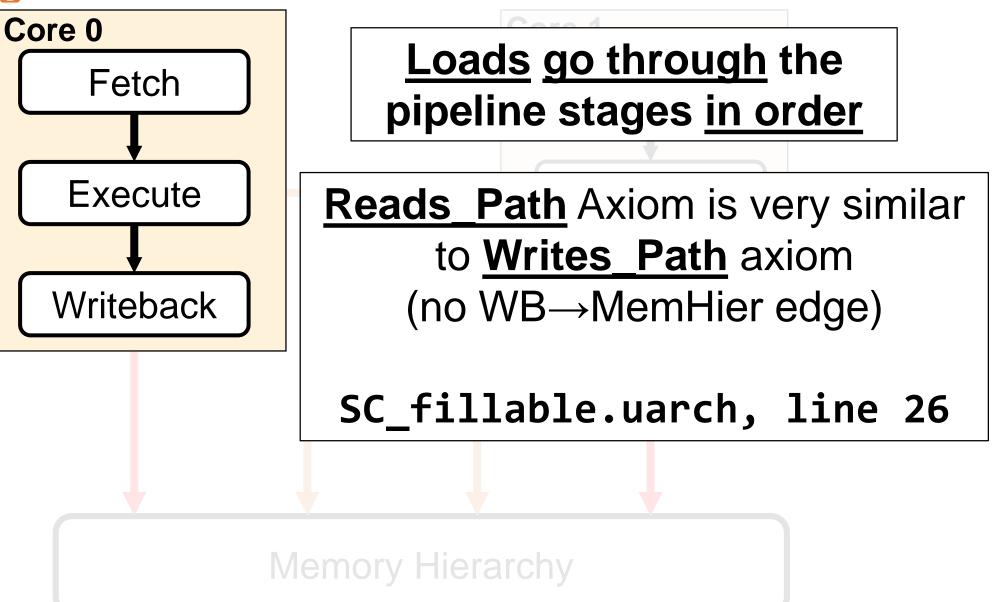

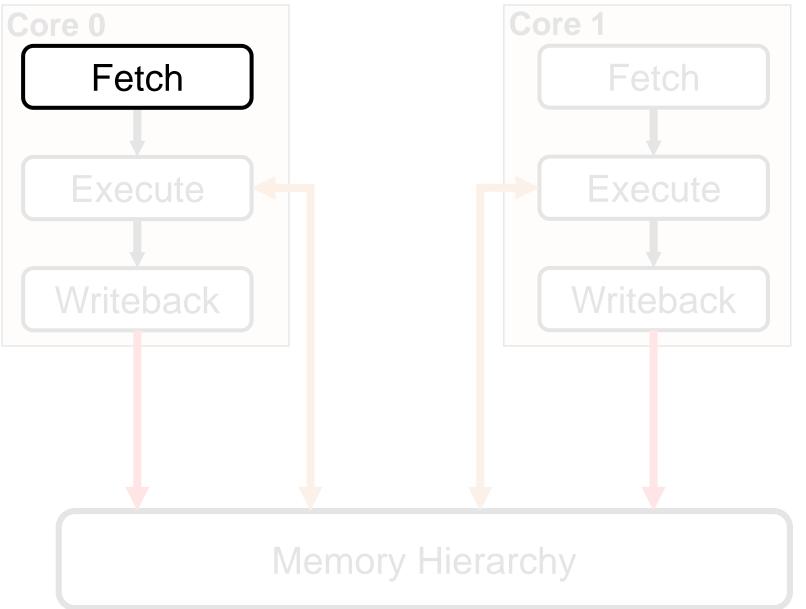

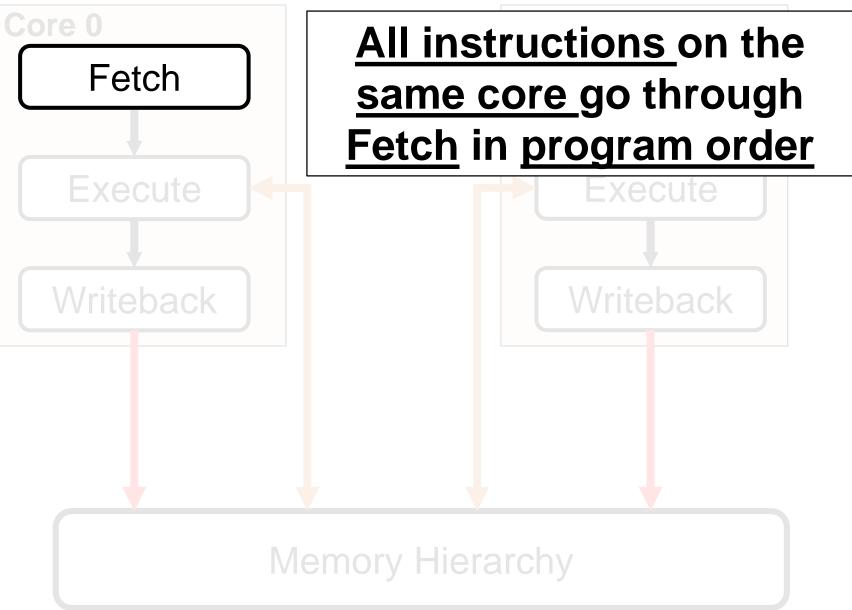

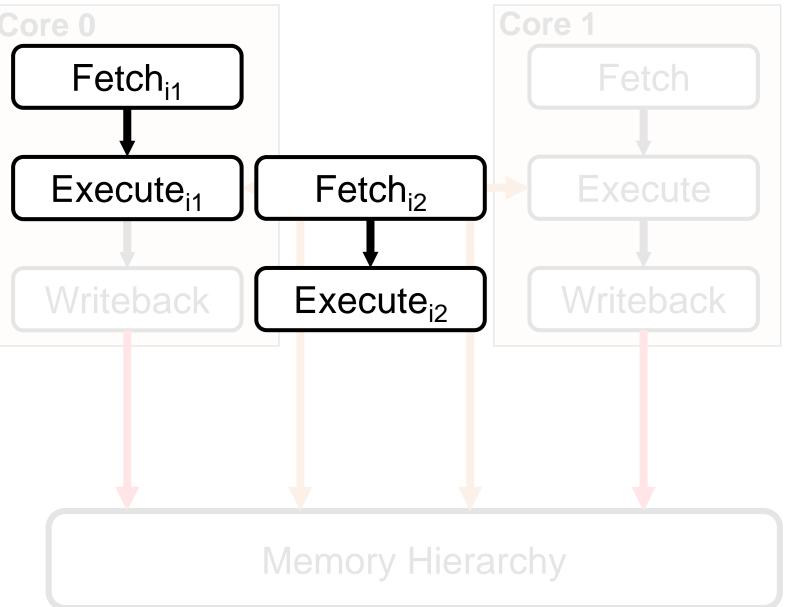

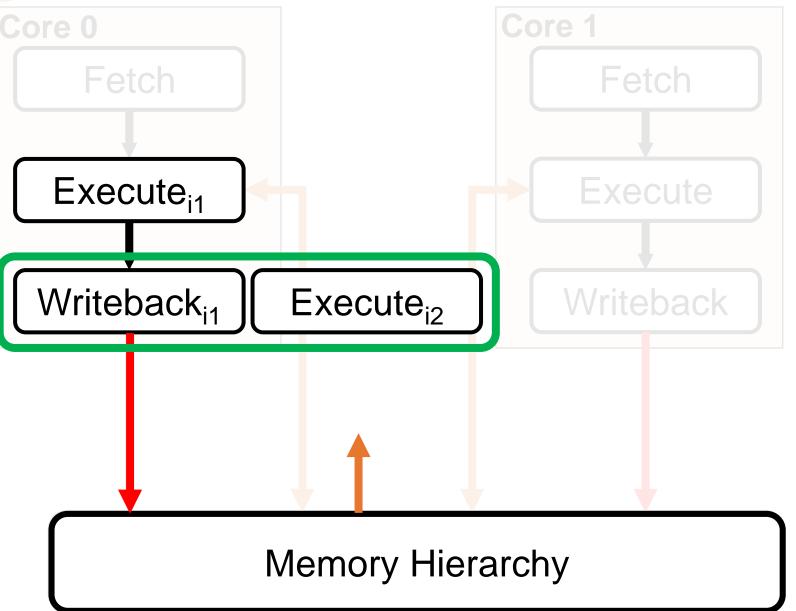

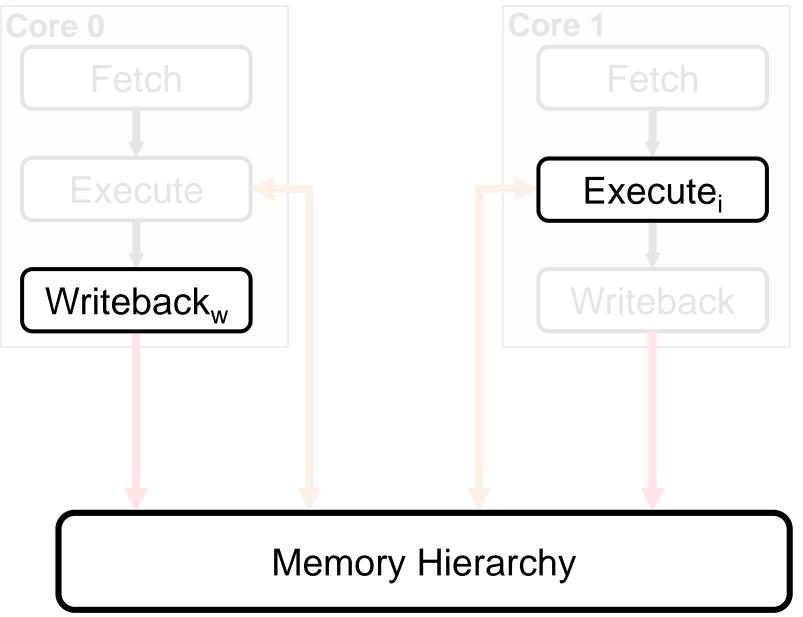

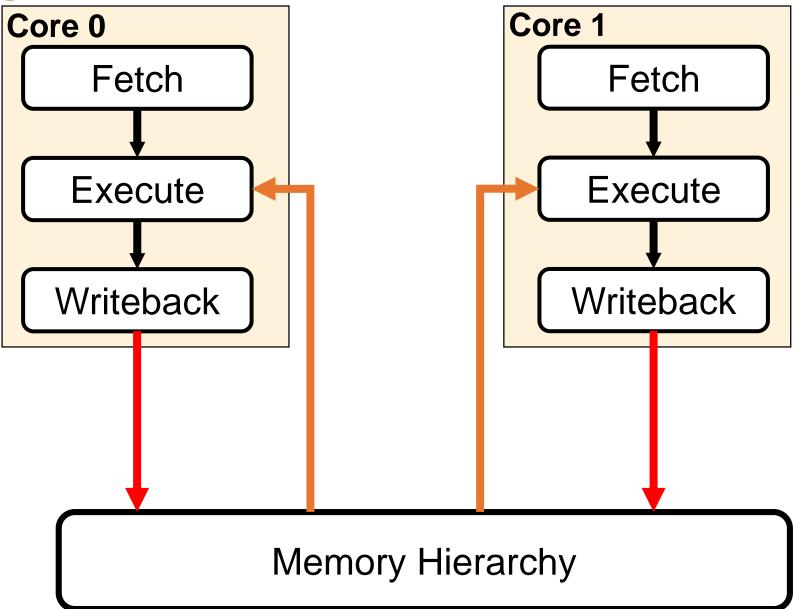

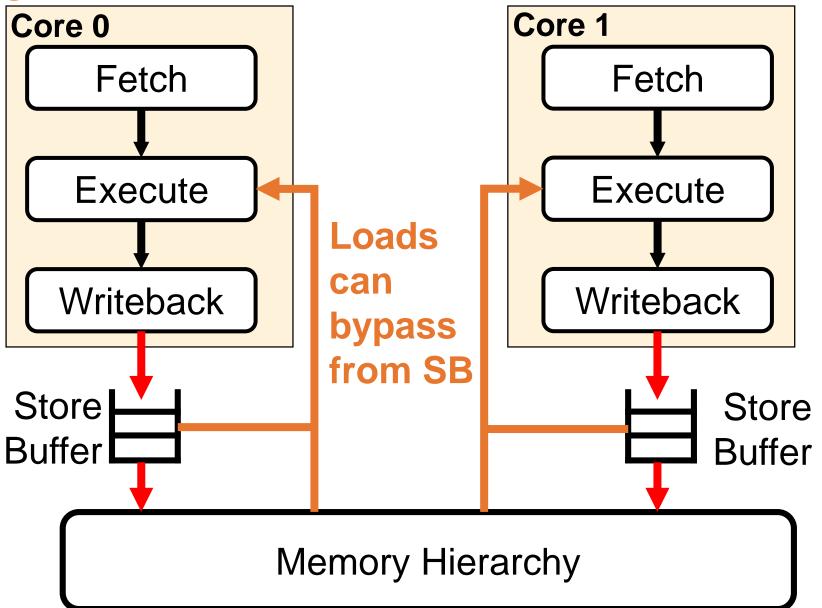

Specifying a Simple (SC) Microarch. in µSpec Core 0 Core 1 Fetch Fetch Execute Execute Writeback Writeback Memory Hierarchy

Specifying a Simple (SC) Microarch. in µSpec

Specifying a Simple (SC) Microarch. in µSpec

# Specifying a Simple (SC) Microarch. in µSpec

#### 1. Start VirtualBox VM

#### 2. Open a Terminal

#### 3. Partially completed SC uarch in

/home/check/pipecheck\_tutorial/uarches/SC\_fillable.uarch

(i.e. ~/pipecheck\_tutorial/uarches/SC\_fillable.uarch)

# µSpec: A DSL for Specifying Microarchitectures

- Language has capabilities similar to first-order logic

- forall, exists, AND (/\), OR (\/), NOT (~), implication (=>)

- Microarchitecture spec is a set of axioms

- Each axiom enforces a *partial ordering* on execution events...

- ...which correspond to individual smaller microarchitectural orderings!

- Eg: Some axioms for pipeline stages, others for coherence...

- Job of PipeCheck is to ensure that axioms correctly work

*together* to uphold the requirements of the ISA-level MCM

- Axiom writing is an iterative process

# Specifying µSpec Nodes

- A node represents a particular event in a particular instruction's execution

- Eg: (i, Fetch) represents the fetch stage of instruction i

- Sometimes the core of a node needs to be explicitly specified

- Eg: (i, (0, MemoryHierarchy)) represents i reaching the memory hierarchy, which is nominally on core 0

- Reflects that there's only one memory hierarchy, not one per core

## Writing µSpec Axioms

- A microarchitecture spec has three components:

- Stage identifier definitions

- Macro definitions (optional) for axiom decomposition and reuse

- Axiom definitions

- Axioms are comprised of FOL operators and built-in *predicates*

- Some predicates deal with nodes and edges

- EdgeExists ((i1, Fetch), (i2, Fetch))

- NodeExists ((i1, Execute))

- Other predicates represent architecture-level properties

- SameCore <instr1> <instr2>

- SamePhysicalAddress, SameData, IsAnyRead, ProgramOrder,...

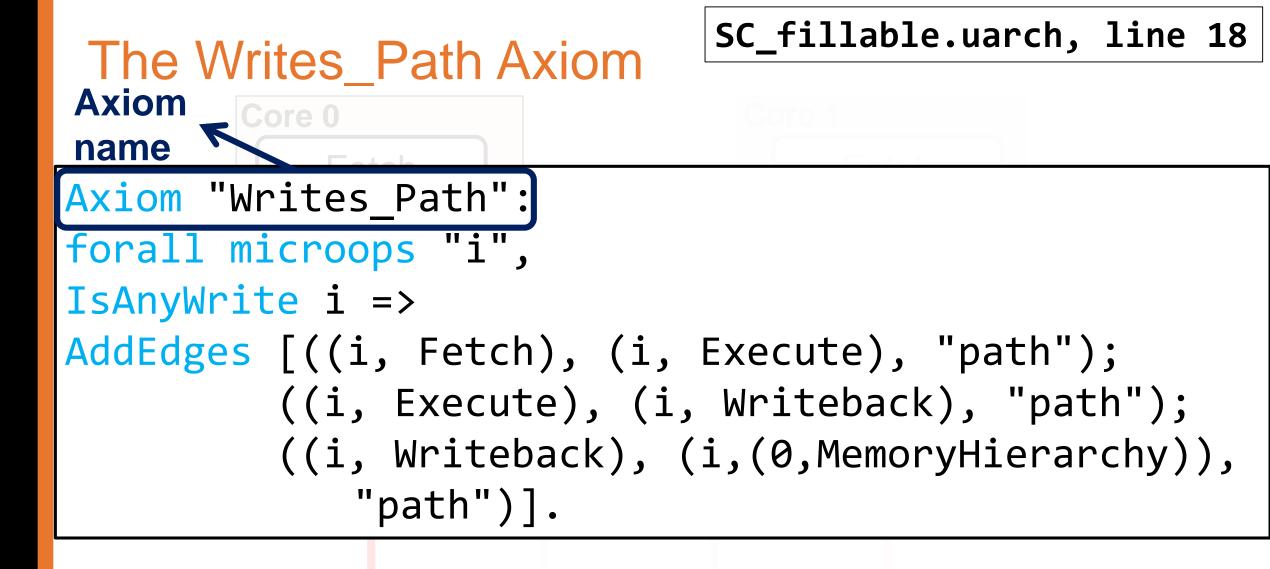

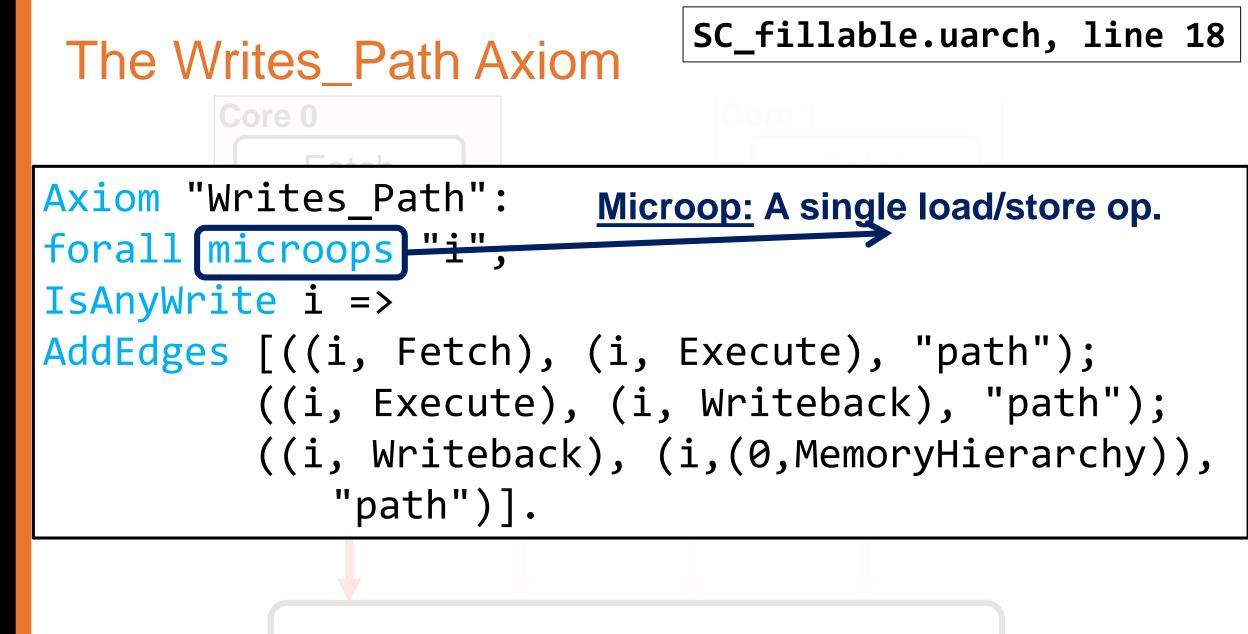

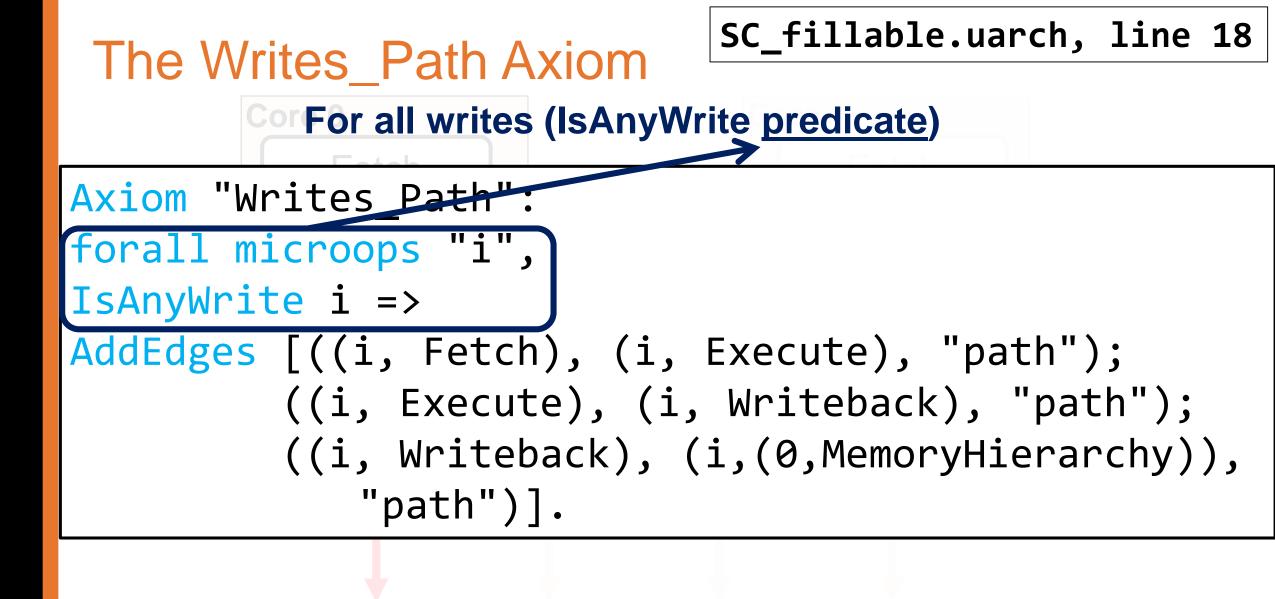

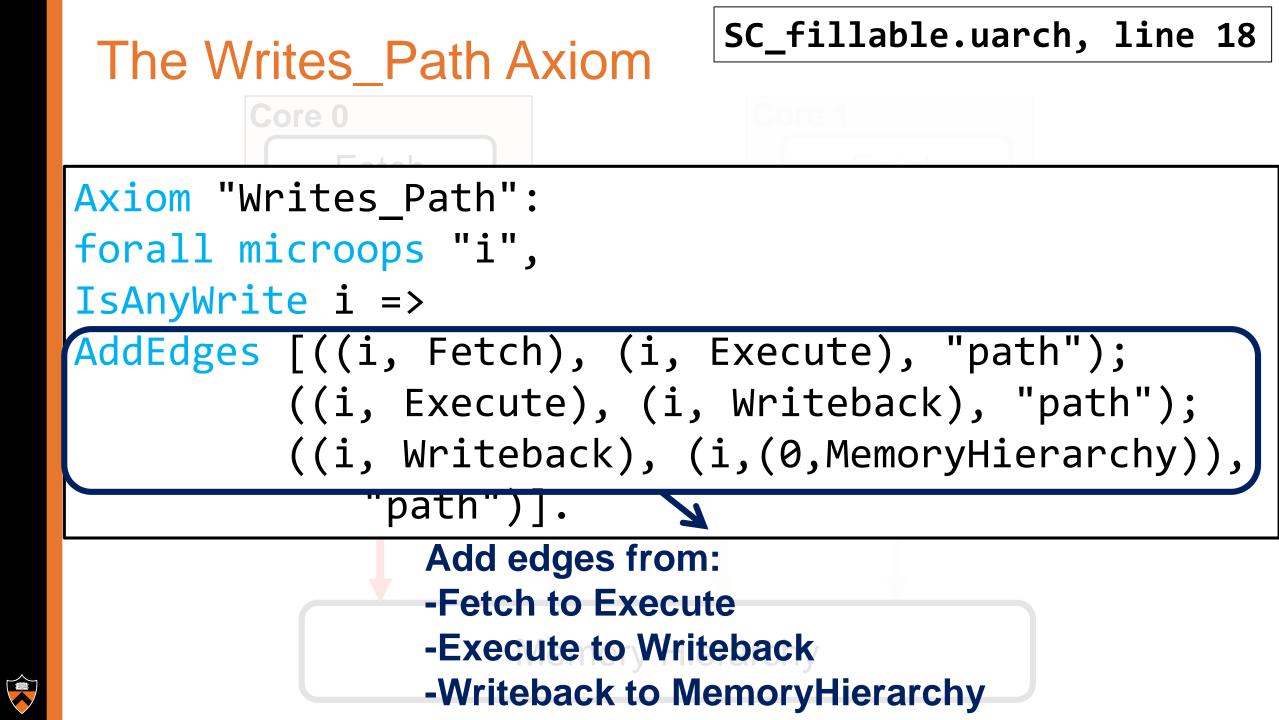

#### SC\_fillable.uarch, line 18 The Writes\_Path Axiom Axiom "Writes Path": forall microops "i", IsAnyWrite i => AddEdges [((i, Fetch), (i, Execute), "path"); ((i, Execute), (i, Writeback), "path"); ((i, Writeback), (i,(0,MemoryHierarchy)), "path")].

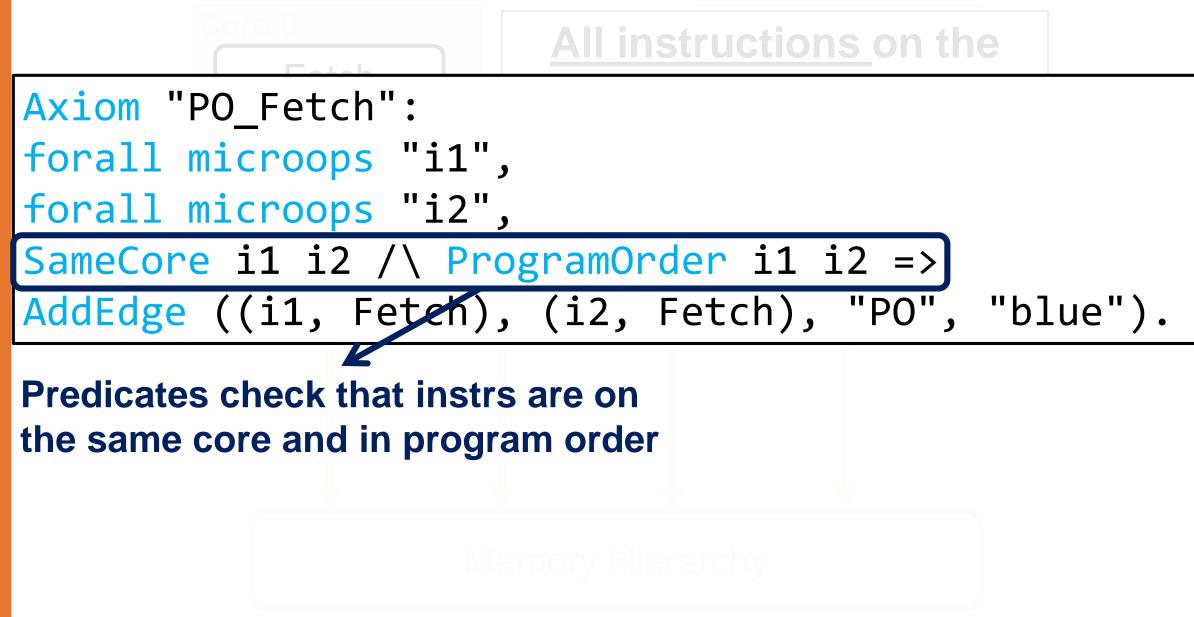

### The PO\_Fetch Axiom

#### SC\_fillable.uarch, line 32

All instructions on the

# Axiom "PO\_Fetch": forall microops "i1", forall microops "i2", SameCore i1 i2 /\ ProgramOrder i1 i2 => AddEdge ((i1, Fetch), (i2, Fetch), "PO", "blue").

#### The PO\_Fetch Axiom

#### SC\_fillable.uarch, line 32

# The PO\_Fetch Axiom

#### SC\_fillable.uarch, line 32

All instructions on the Axiom "PO Fetch": forall microops "i1", forall microops "i2", SameCore i1 i2 /\ ProgramOrder i1 i2 => AddEdge ((i1, Fetch), (i2, Fetch), "PO", "blue").

> Add edge from Fetch stage of earlier instruction i1 to Fetch stage of later instruction i2

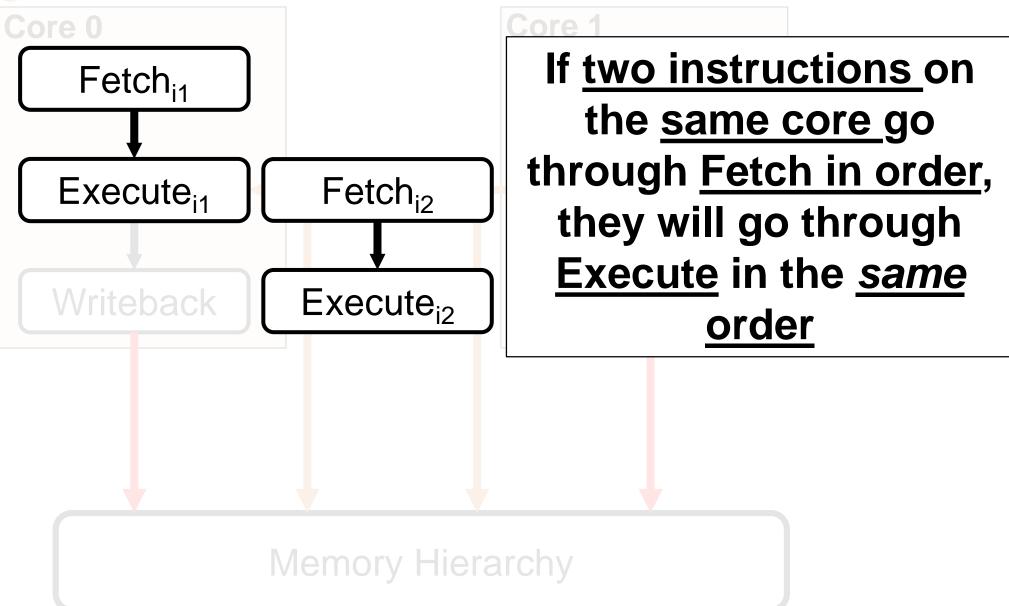

# The Execute\_Stage\_Is\_In\_order Axiom

ftwo SC\_fillable.uarch, line 38

Axiom "Execute\_stage\_is\_in\_order":

forall microops "i1",

forall microops "i2",

SameCore i1 i2 /\

EdgeExists ((i1, Fetch), (i2, Fetch), "") =>

AddEdge ((i1, Execute), (i2, Execute), "PPO").

Memory Hierarchy

# The Execute\_Stage\_Is\_In\_order Axiom

SC\_fillable.uarch, line 38

Axiom "Execute\_stage\_is\_in\_order":

forall microops "i1",

forall microops "i2",

SameCore i1 i2 /\

EdgeExists ((i1, Fetch), (i2, Fetch), "") =>

AddEdge ((i1, Execute), (i2, Execute), "PPO").

If instructions i1 and i2 on same core go through Fetch in order...

Memory Hierarchy

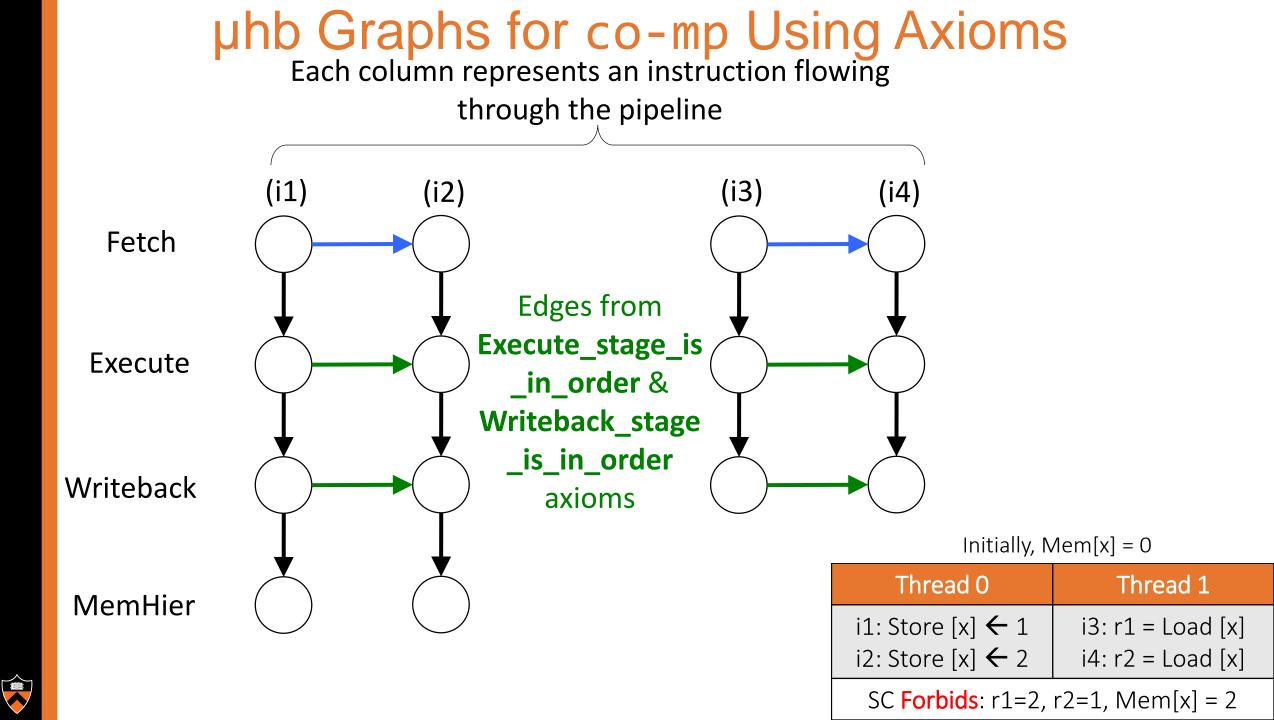

# The Execute\_Stage\_Is\_In\_order Axiom

ftwo SC\_fillable.uarch, line 38

Axiom "Execute stage is in order": forall microops "i1", forall microops "i2", SameCore i1 i2 /\ EdgeExists ((i1, Fetch), (i2, Fetch), "") => AddEdge ((i1, Execute), (i2, Execute), "PPO"). ...then they go through Execute in the same order.

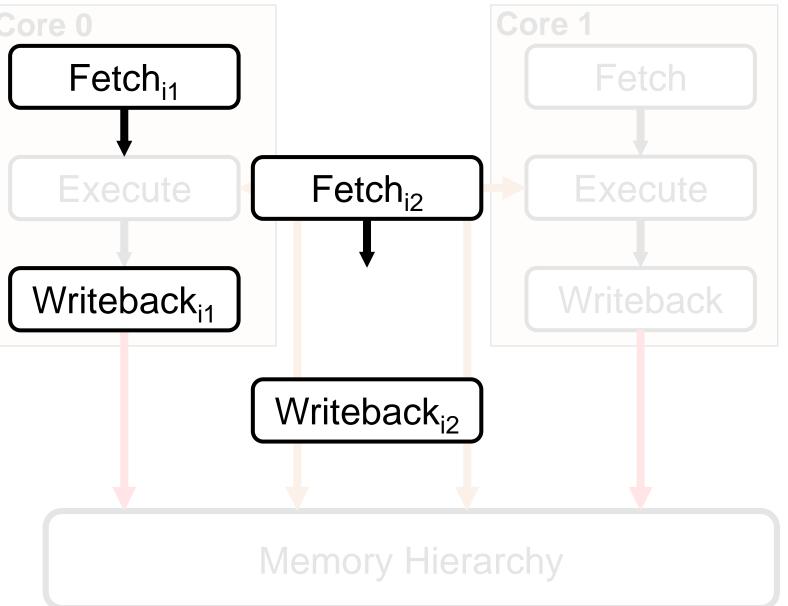

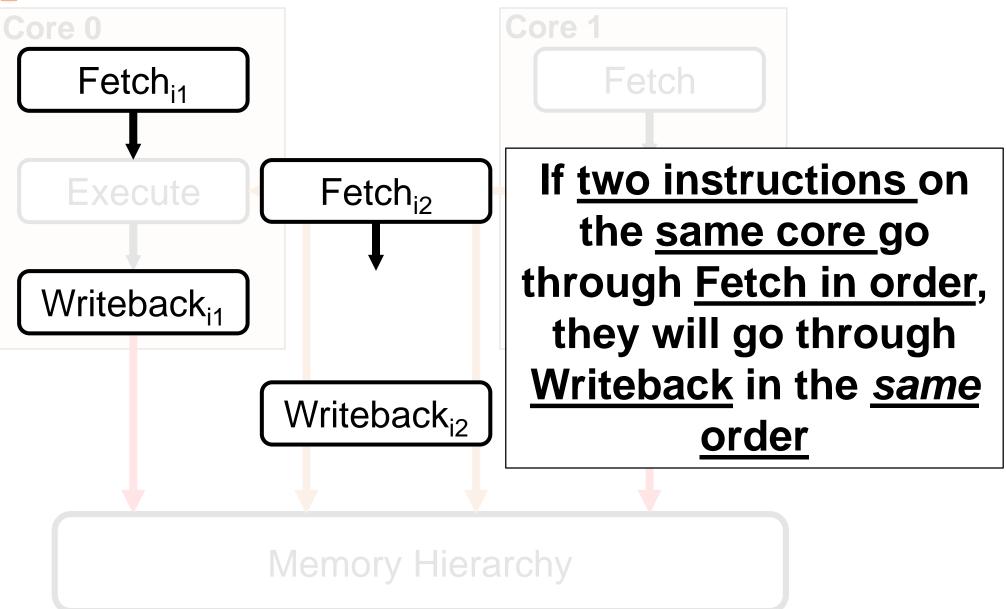

# The Writeback\_Stage\_Is\_In\_Order Axiom ftwo i SC\_fillable.uarch, line 55 If two instructions on the same core go through Fetch in order, they will go through Writeback in the same order Axiom "Writeback stage is in order": forall microops "i1", forall microops "i2", i1 i2 /\ EdgeExists ((i1, \_\_\_\_), (i2, \_\_\_\_), AddEdge ((i1, ), (i2, ), "PPO").

Viemory Hierarchy

# The Writeback\_Stage\_Is\_In\_Order Axiom

ftwo SC\_fillable.uarch, line 55

If two instructions on the same core go through Fetch in order, they will go through Writeback in the same order

Axiom "Writeback\_stage\_is\_in\_order":

forall microops "i1",

forall microops "i2",

SameCore i1 i2 /\

EdgeExists ((i1, Fetch), (i2, Fetch), "") =>

AddEdge ((i1, Writeback), (i2, Writeback), "PPO").

Memory Hierarchy

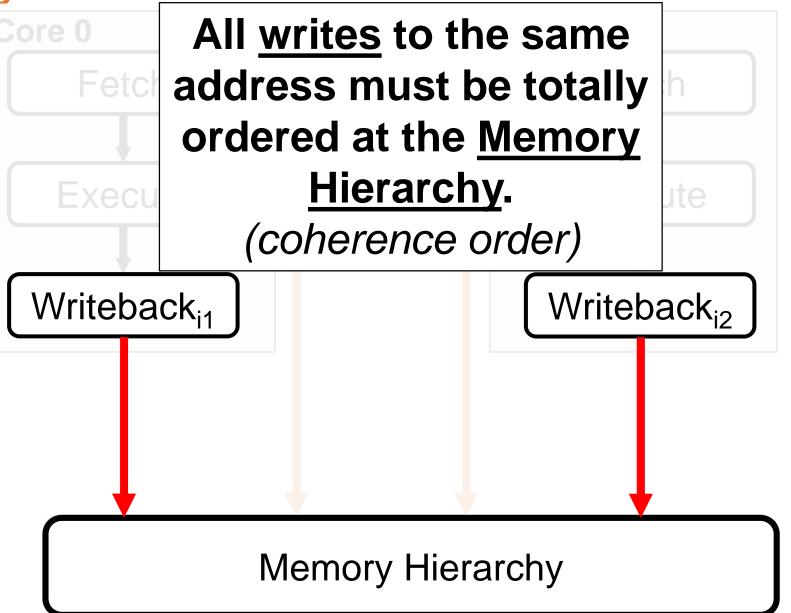

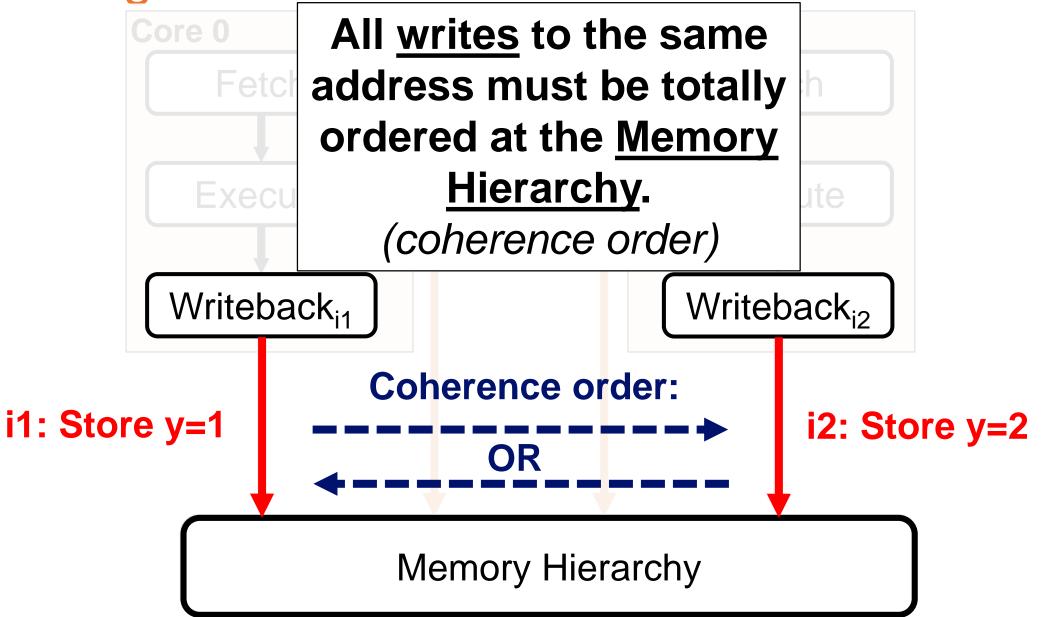

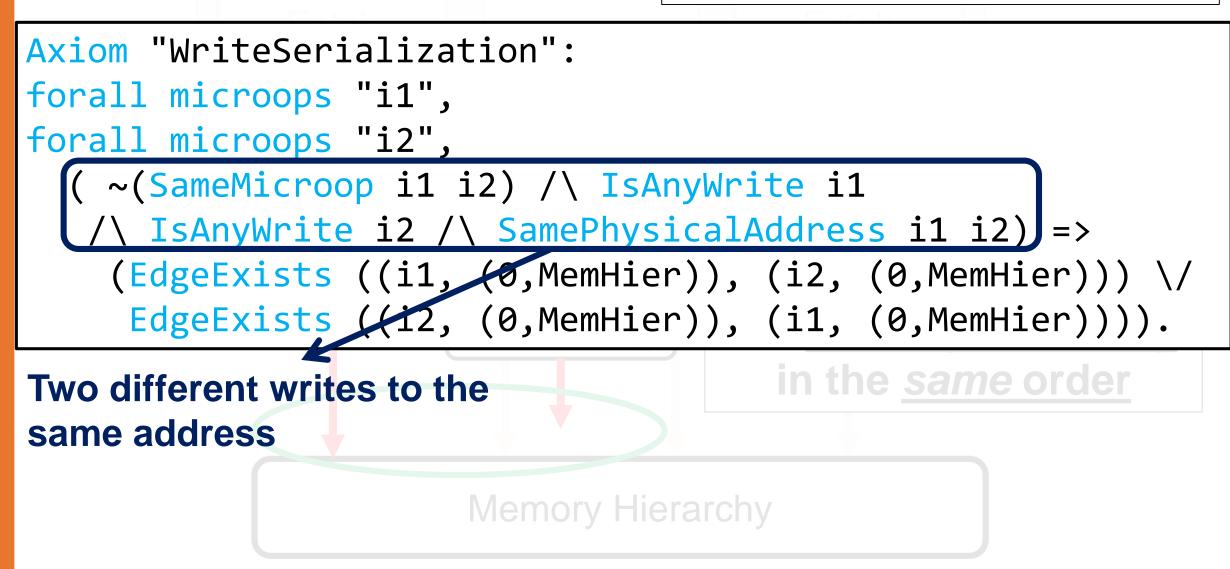

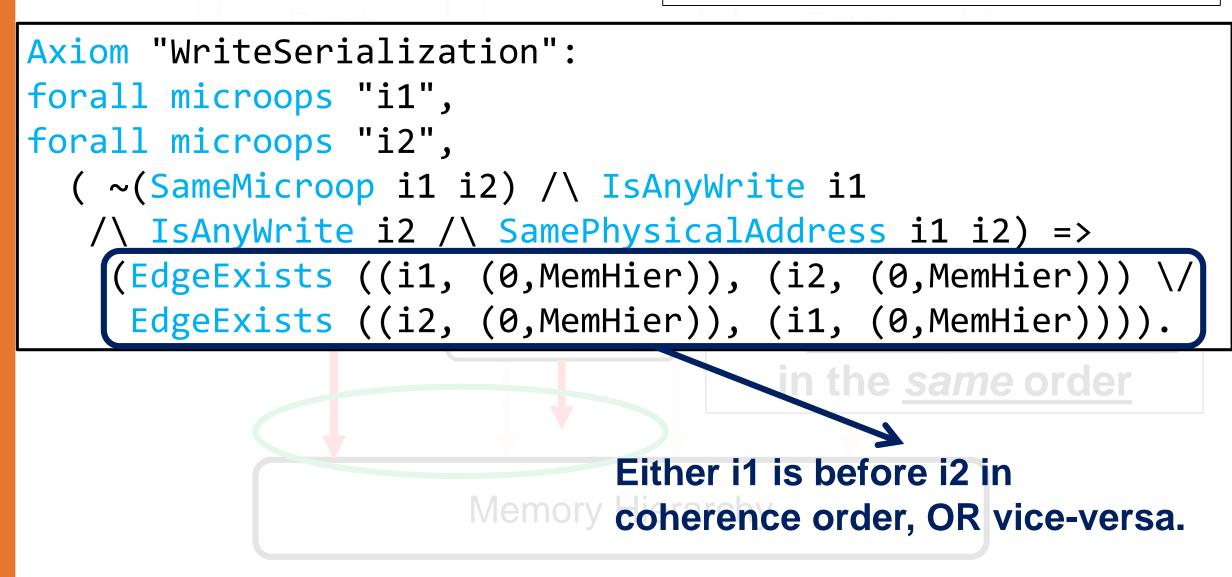

## The WriteSerialization Axiom

#### SC\_fillable.uarch, line 65

Axiom "WriteSerialization":

forall microops "i1",

forall microops "i2",

( ~(SameMicroop i1 i2) /\ IsAnyWrite i1

/\ IsAnyWrite i2 /\ SamePhysicalAddress i1 i2) =>

(EdgeExists ((i1, (0,MemHier)), (i2, (0,MemHier))) \/

EdgeExists ((i2, (0,MemHier)), (i1, (0,MemHier)))).

in the <u>same order</u>

Memory Hierarchy

## The WriteSerialization Axiom

SC\_fillable.uarch, line 65

## The WriteSerialization Axiom

SC\_fillable.uarch, line 65

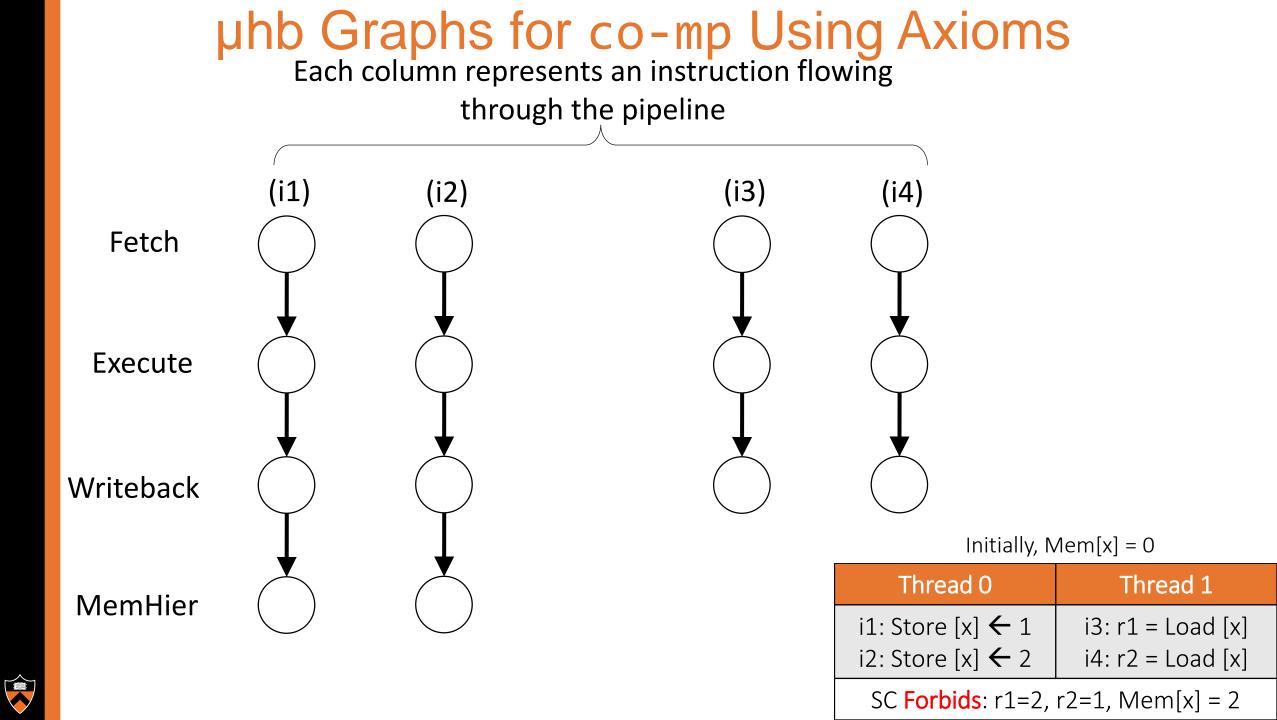

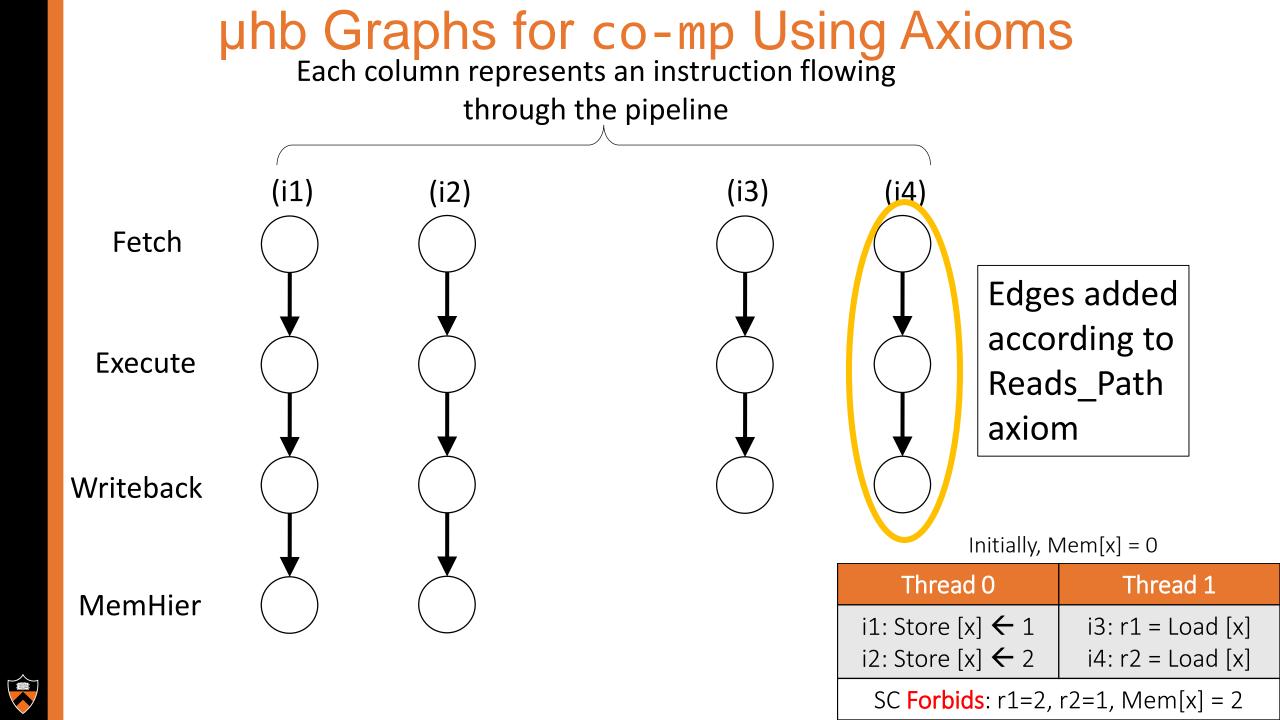

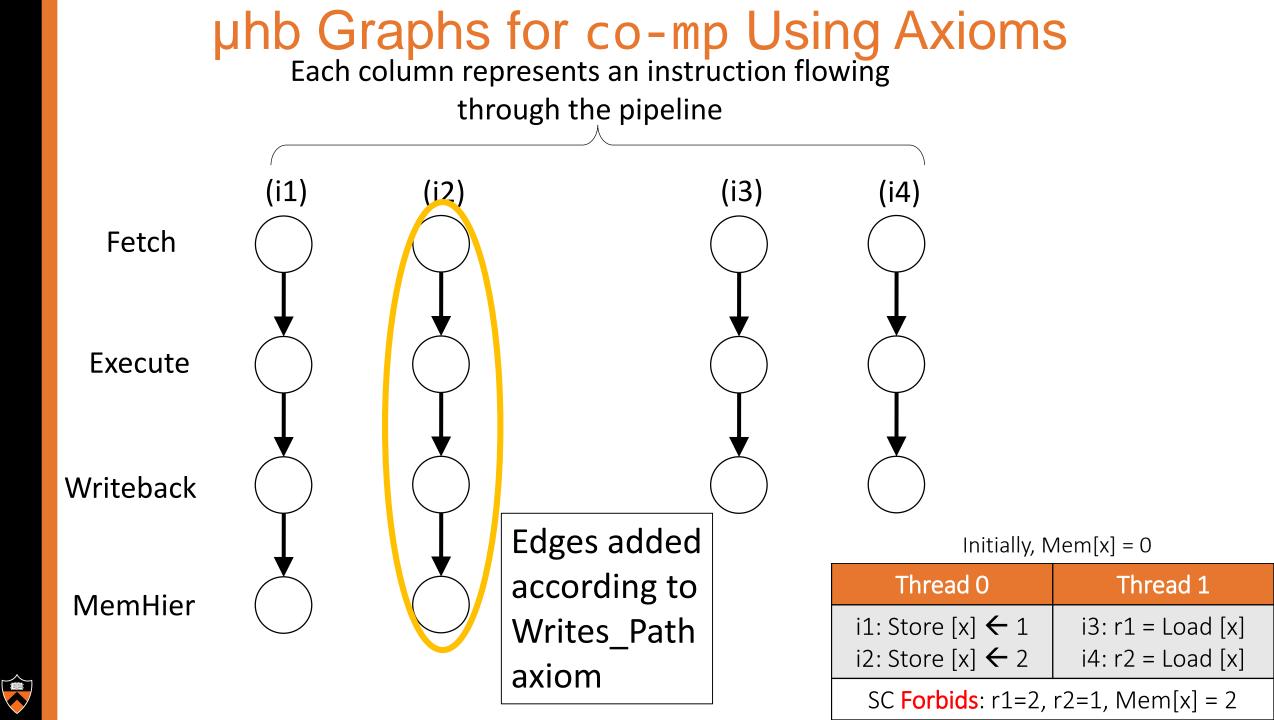

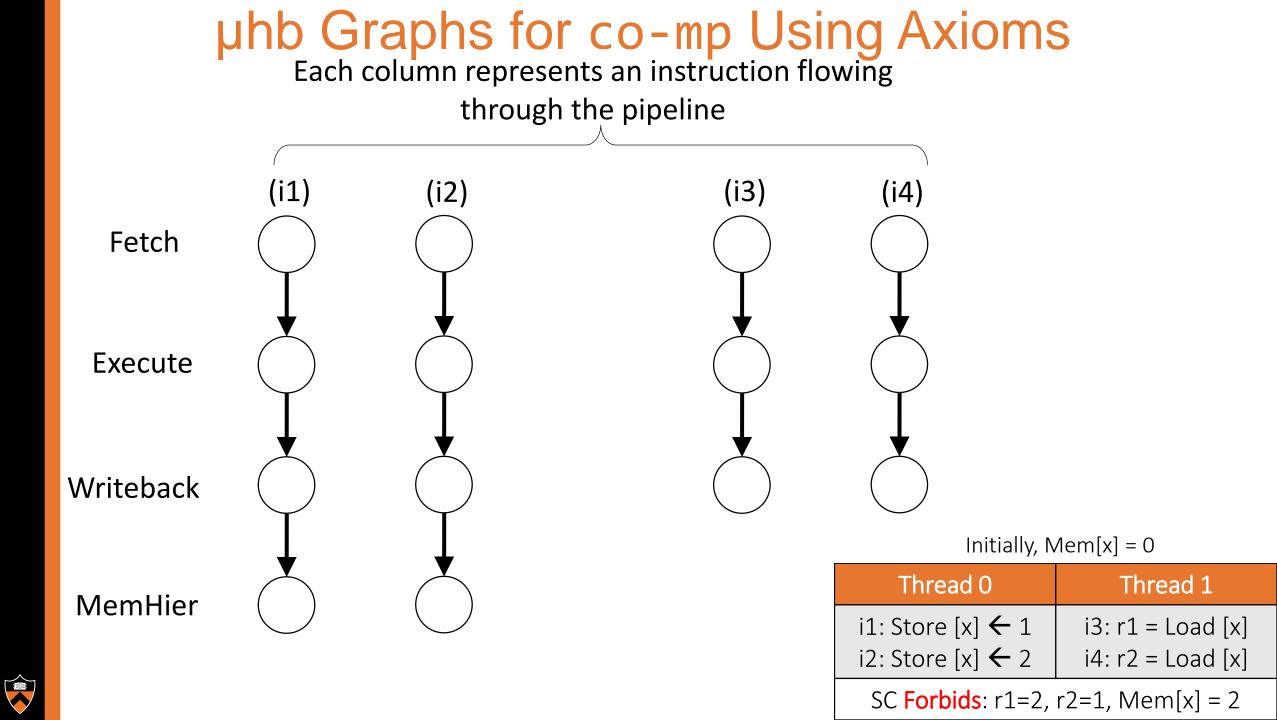

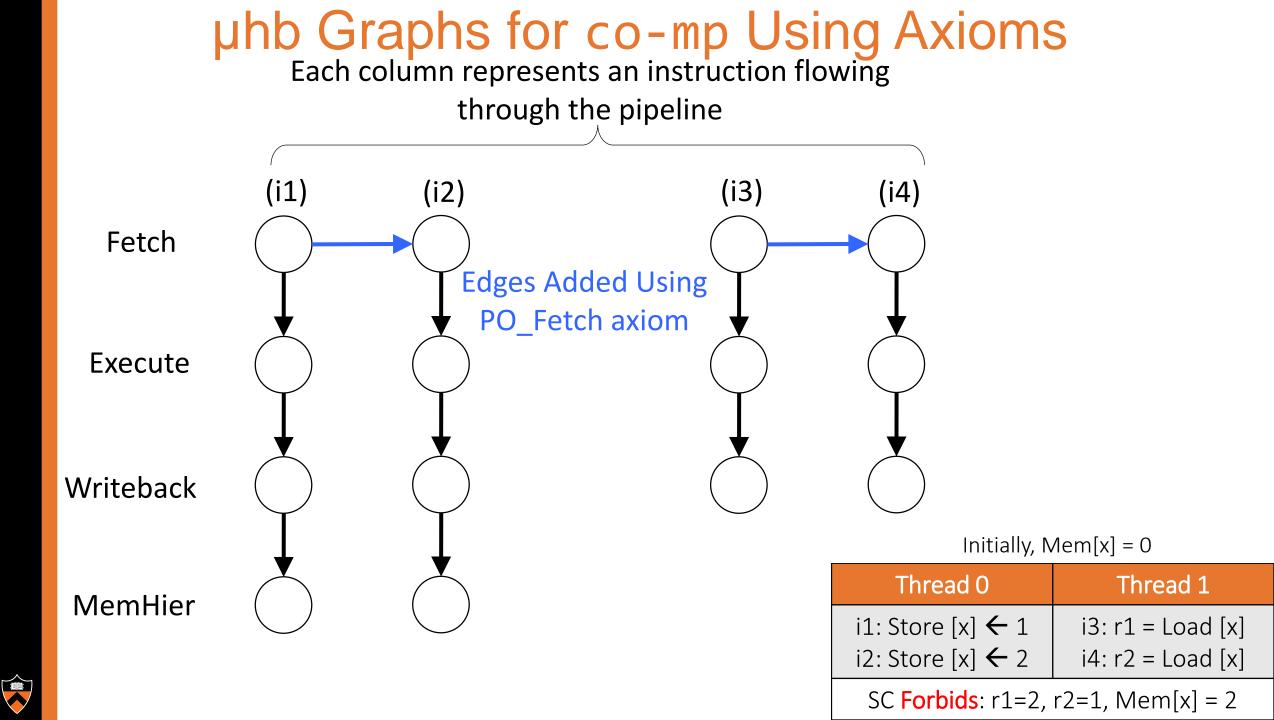

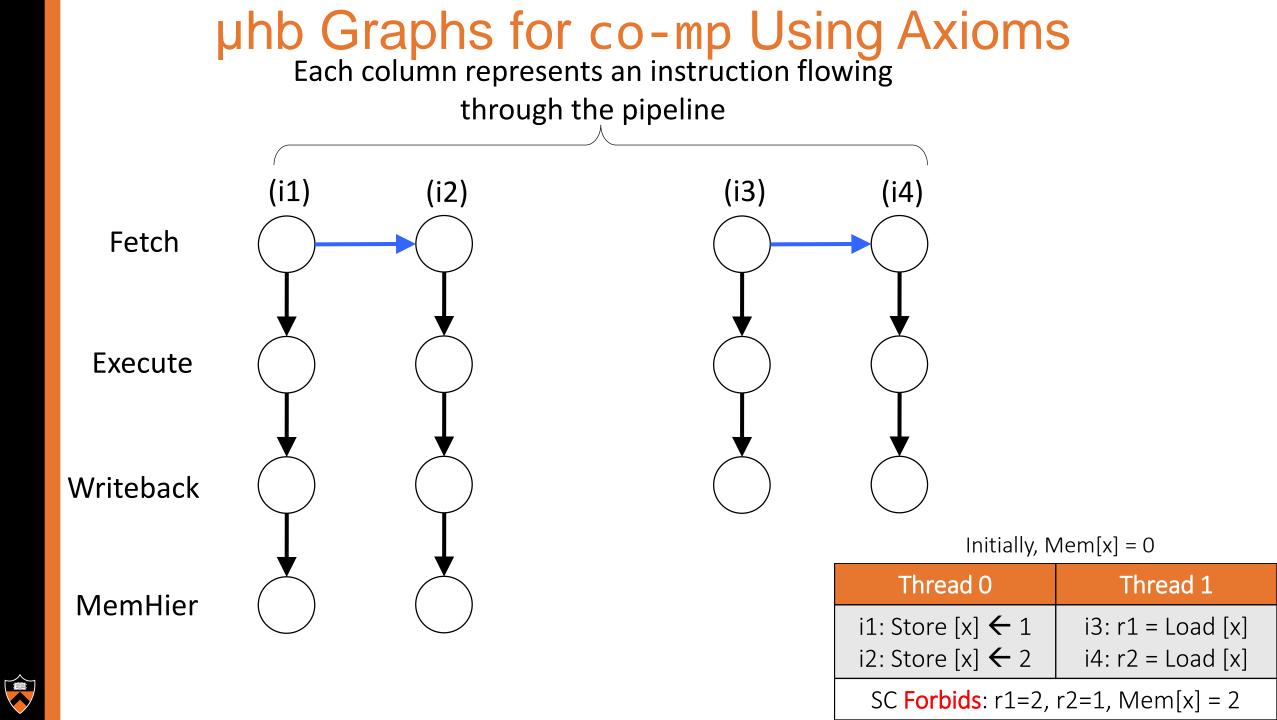

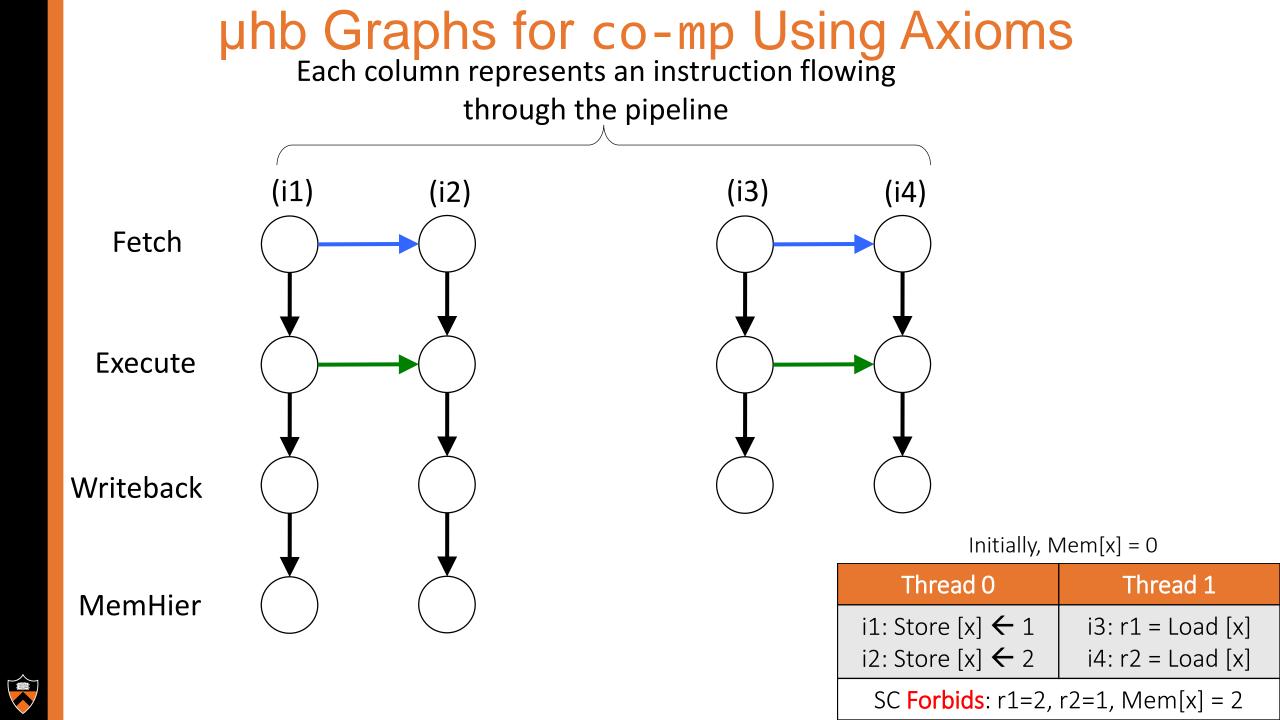

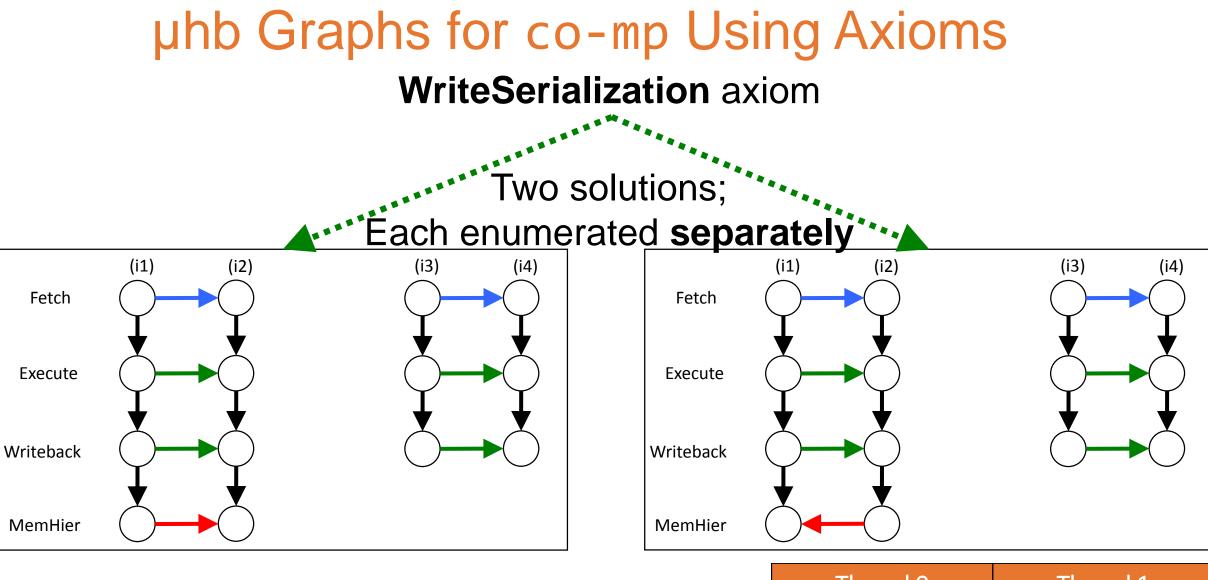

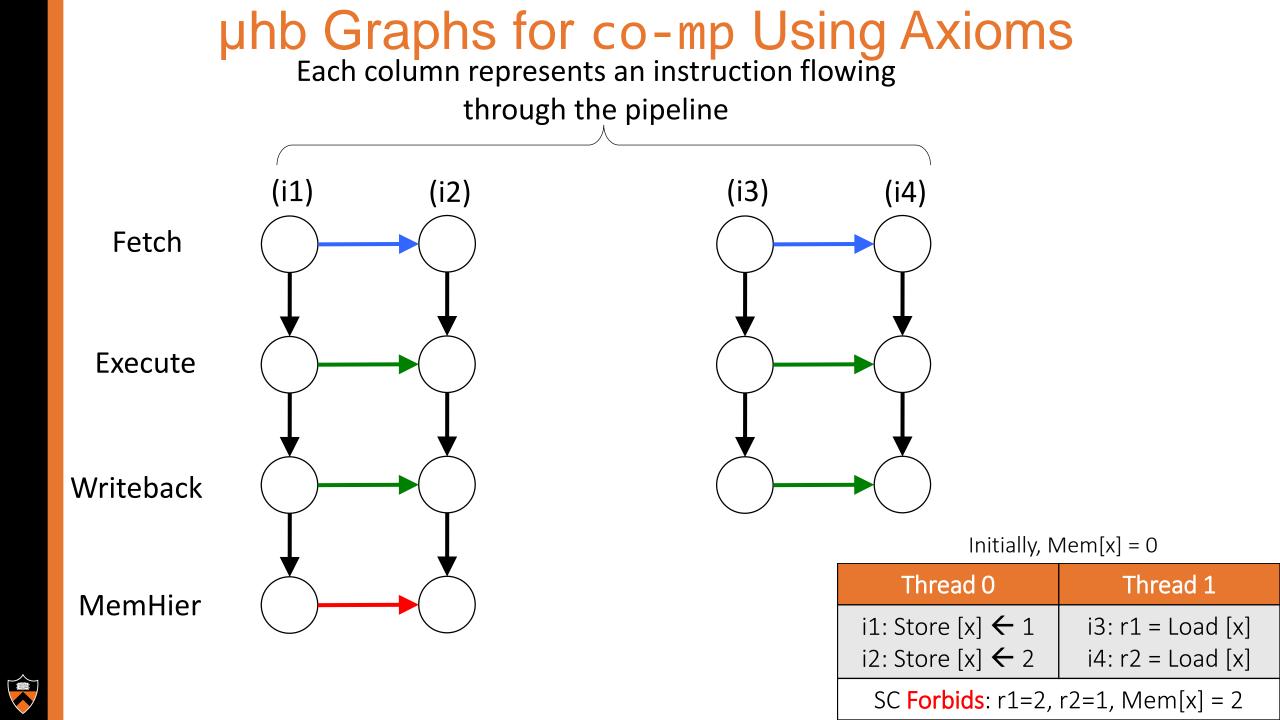

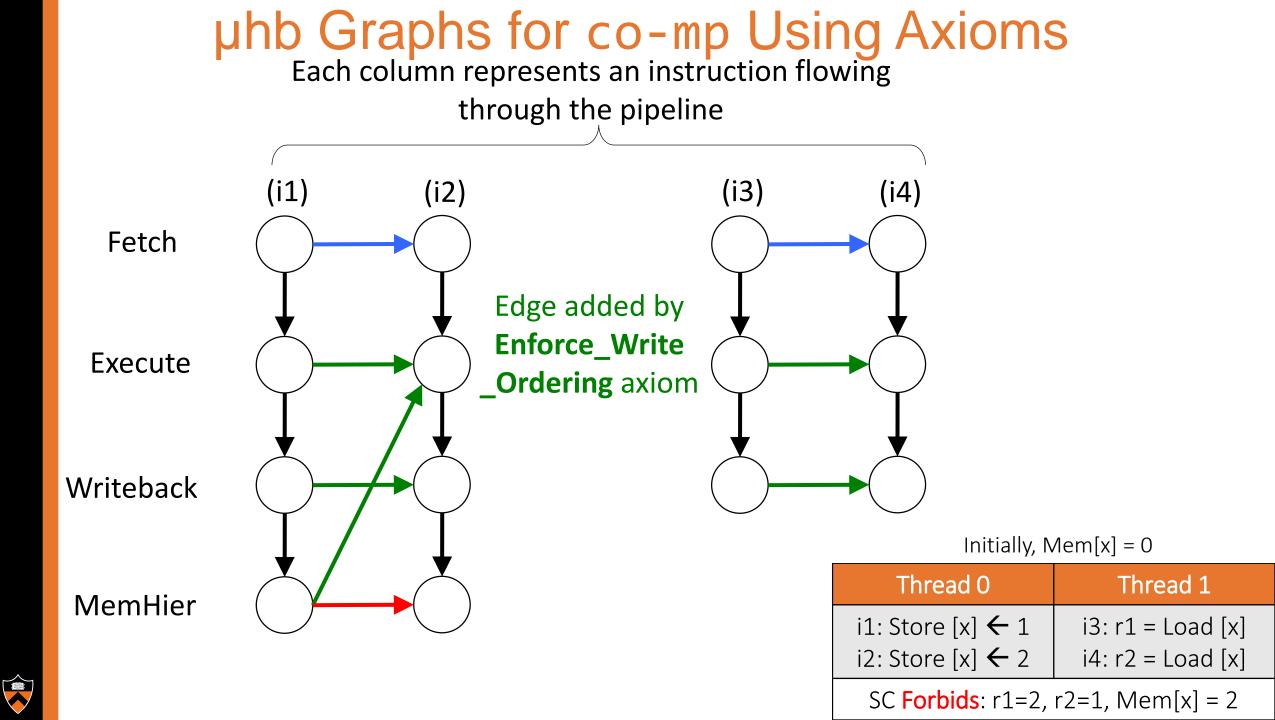

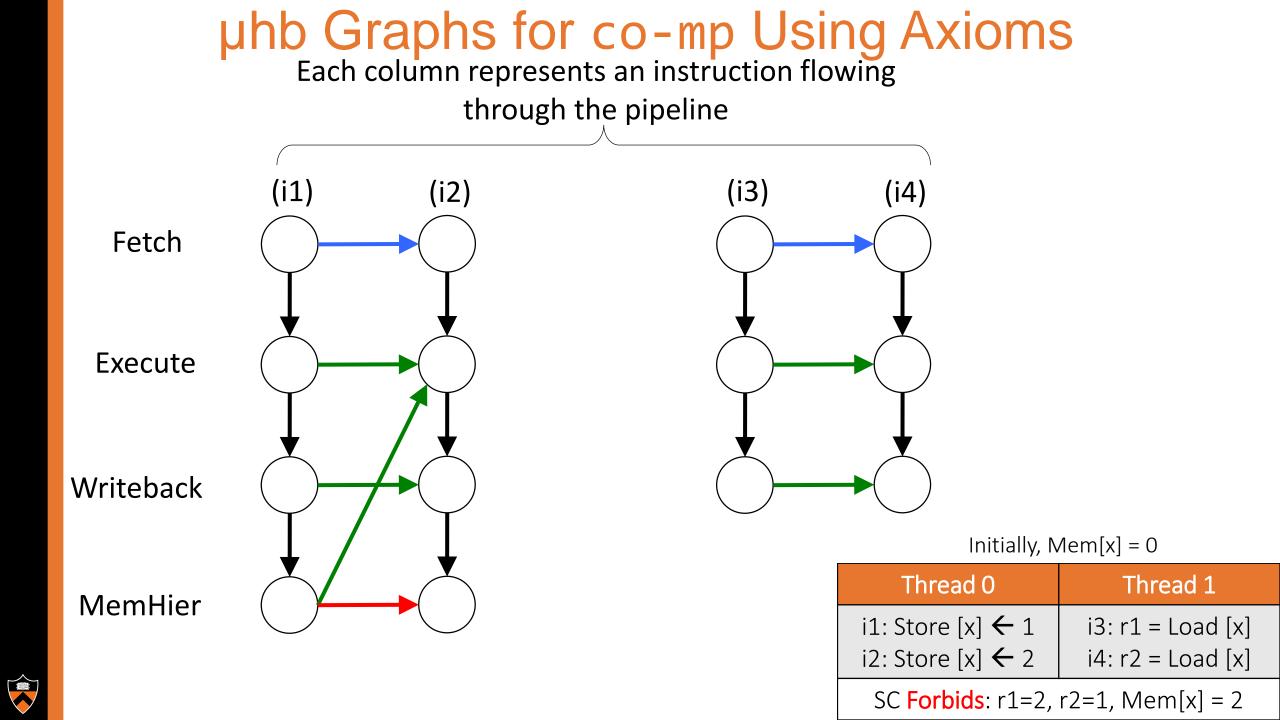

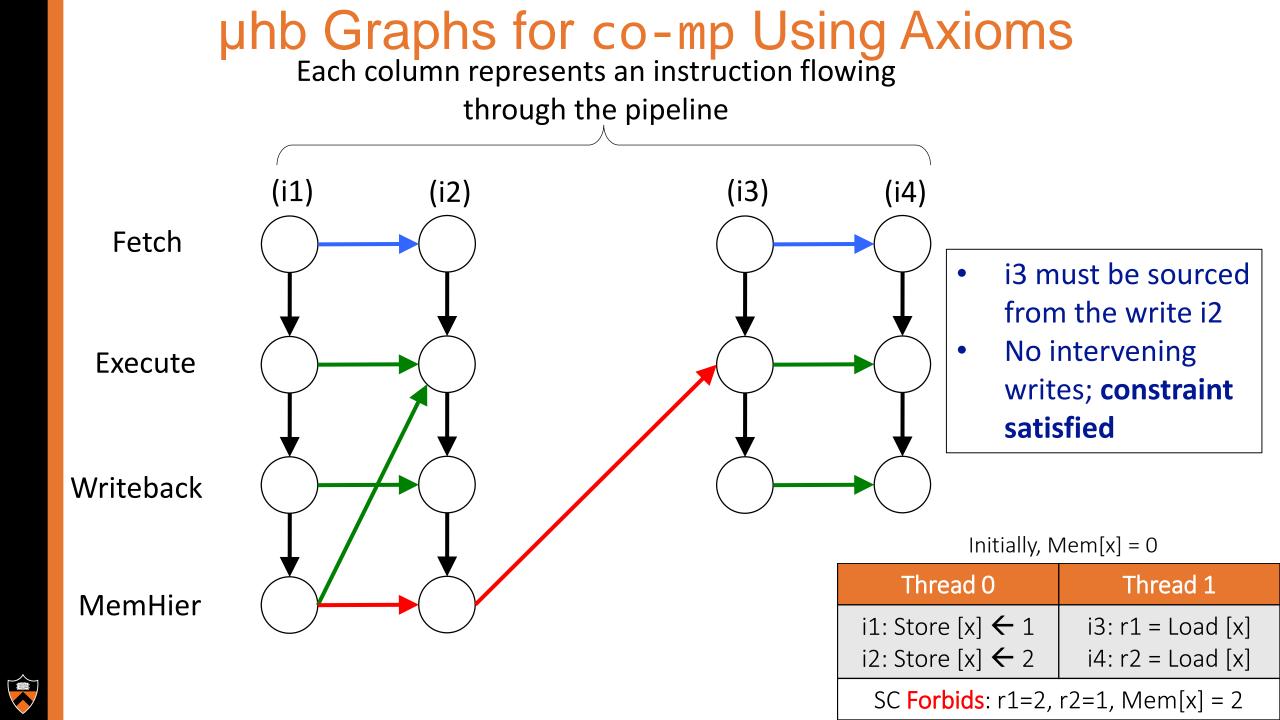

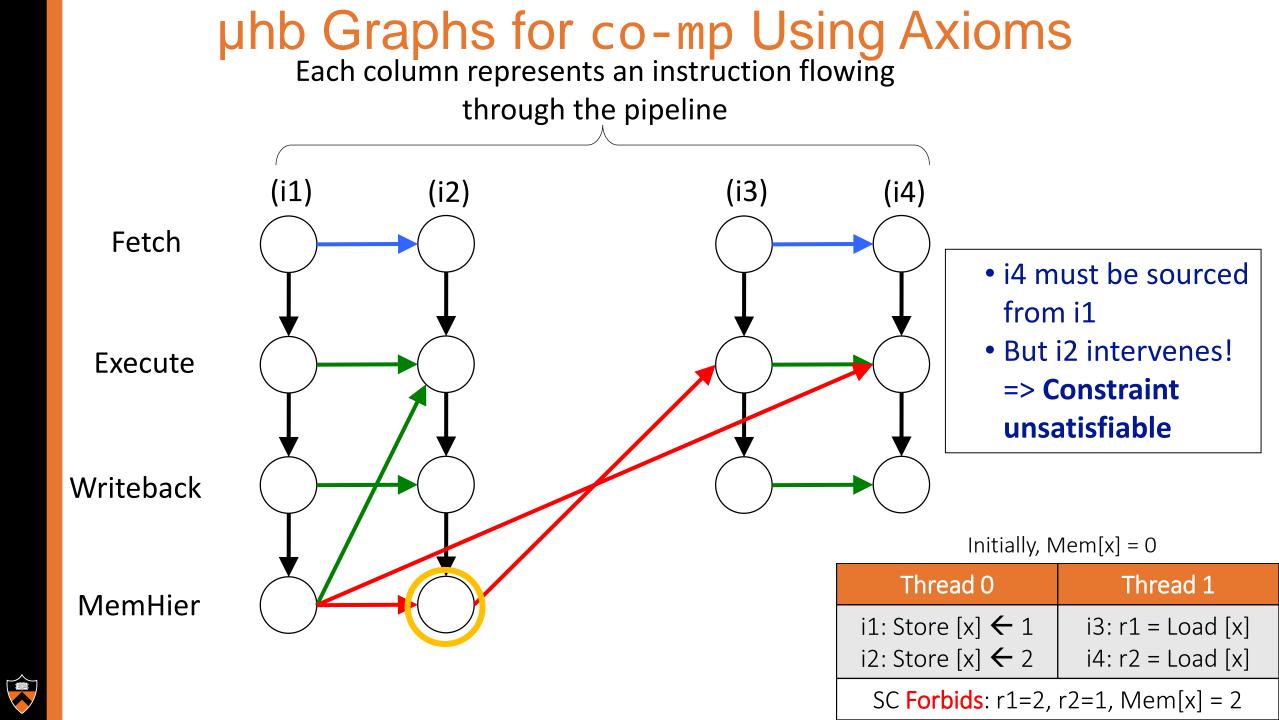

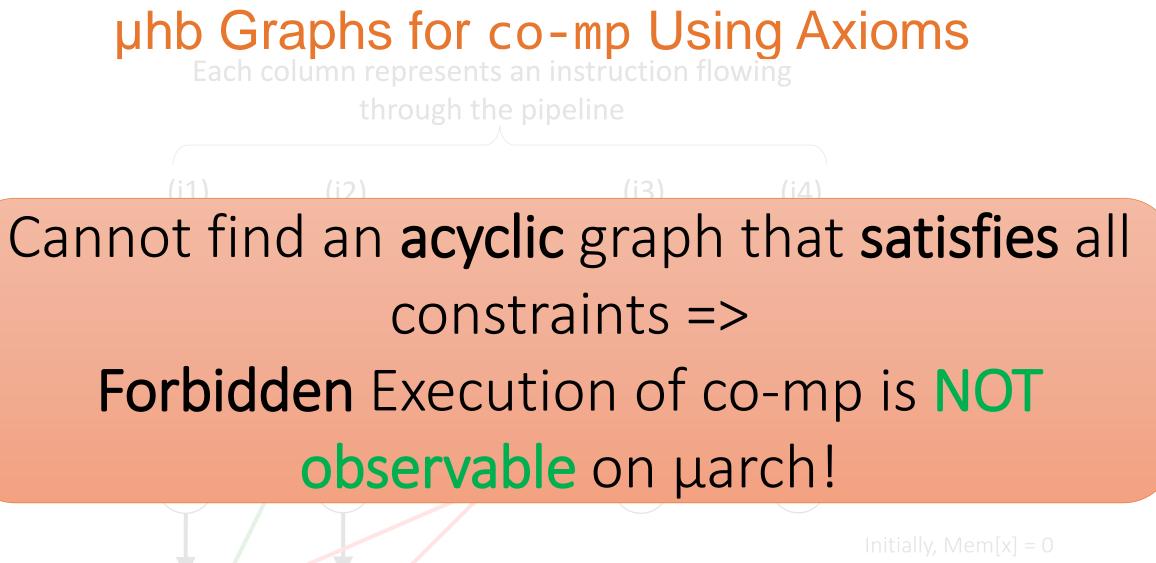

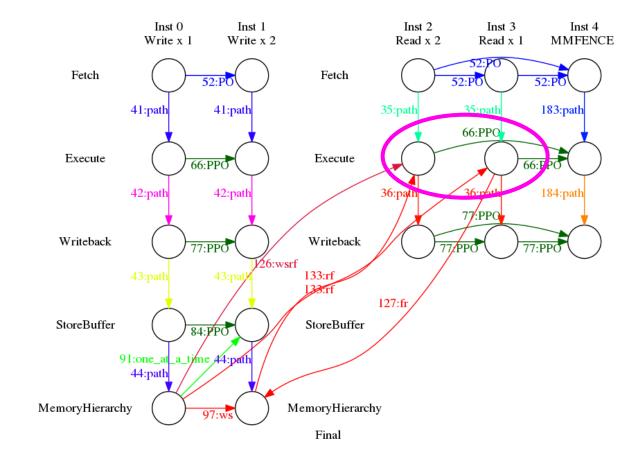

# µhb Graphs for co-mp Using Axioms WriteSerialization axiom

| Thread 0                                   | Thread 1                               |

|--------------------------------------------|----------------------------------------|

| i1: Store [x] ← 1<br>i2: Store [x] ← 2     | i3: r1 = Load [x]<br>i4: r2 = Load [x] |

| SC <b>Forbids</b> : r1=2, r2=1, Mem[x] = 2 |                                        |

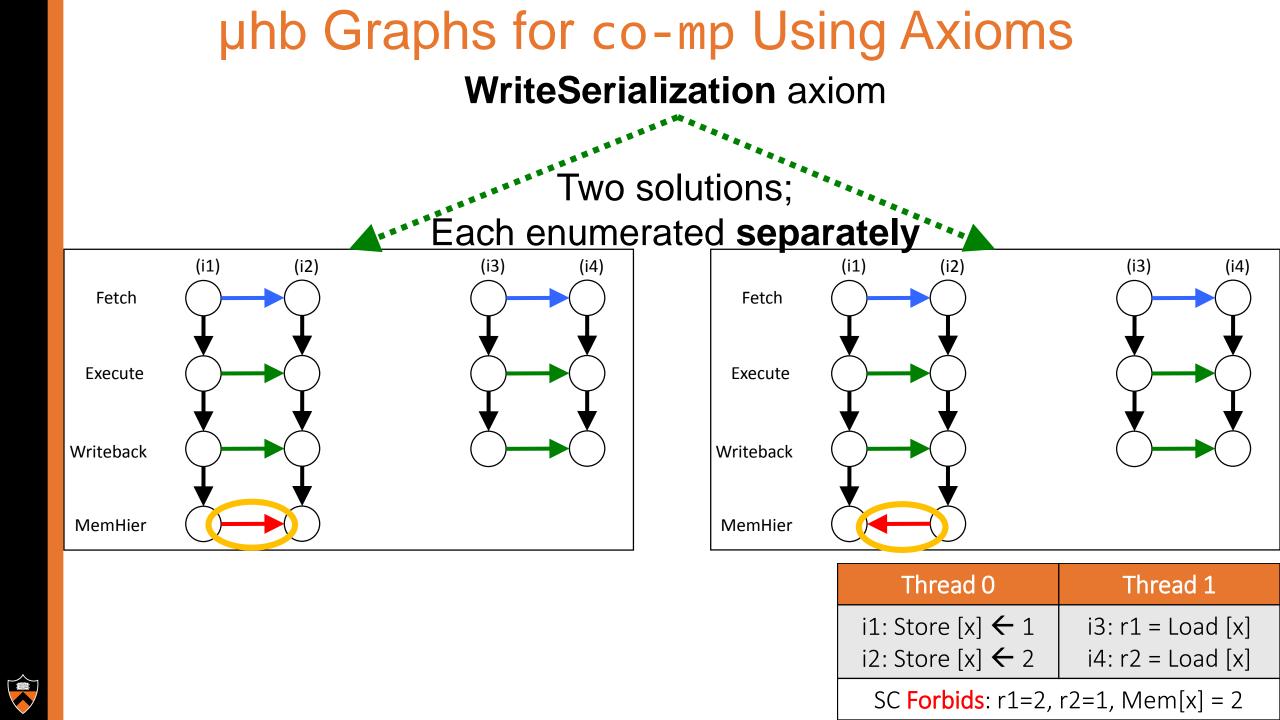

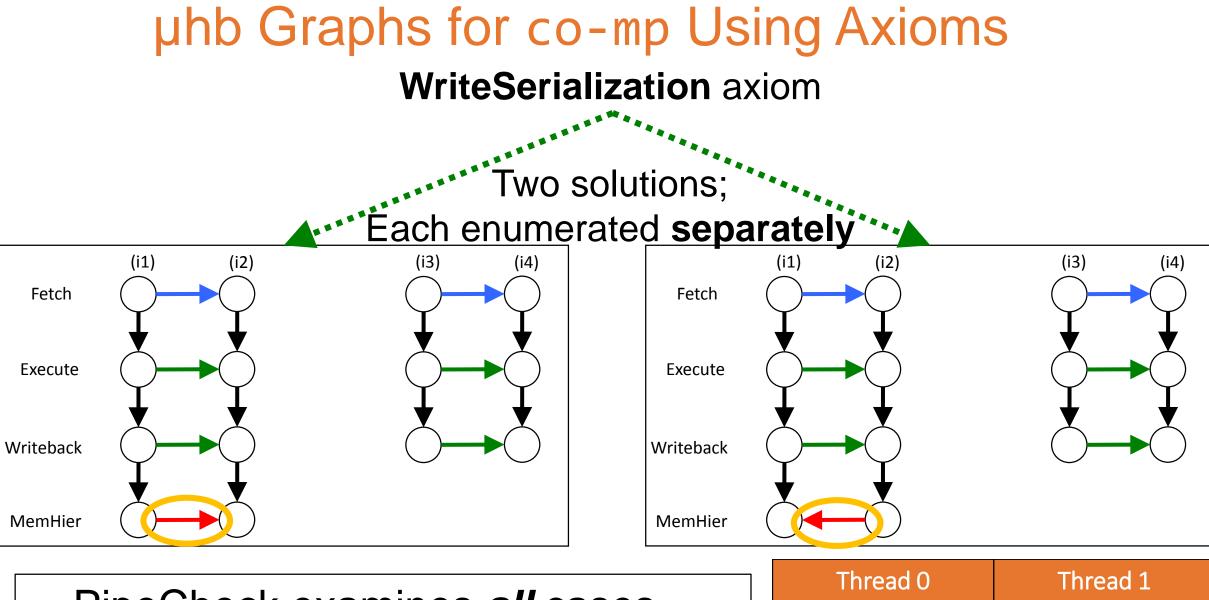

## µhb Graphs for co-mp Using Axioms

#### WriteSerialization axiom

Two solutions; **Each enumerated separately**

| Thread 0                                         | Thread 1                               |

|--------------------------------------------------|----------------------------------------|

| i1: Store [x] ← 1<br>i2: Store [x] ← 2           | i3: r1 = Load [x]<br>i4: r2 = Load [x] |

| SC <b>Forbids</b> : $r1=2$ , $r2=1$ , Mem[x] = 2 |                                        |

| Thread O      | Thread 1                               |

|---------------|----------------------------------------|

| i1: Store [x] | i3: r1 = Load [x]<br>i4: r2 = Load [x] |

|               |                                        |

SC **Forbids**: r1=2, r2=1, Mem[x] = 2

PipeCheck examines all cases

• Will focus on left graph for clarity

| Thread 0      | Thread 1                               |

|---------------|----------------------------------------|

| i1: Store [x] | i3: r1 = Load [x]<br>i4: r2 = Load [x] |

|               |                                        |

SC **Forbids**: r1=2, r2=1, Mem[x] = 2

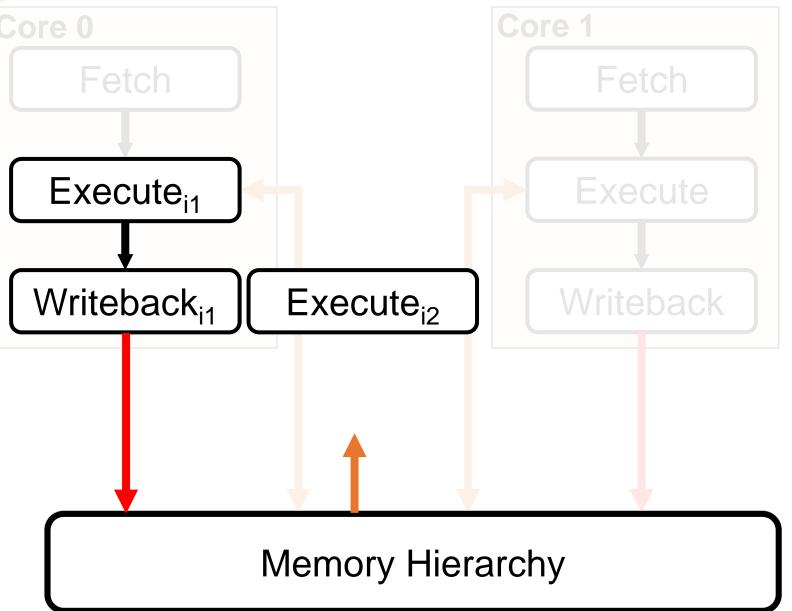

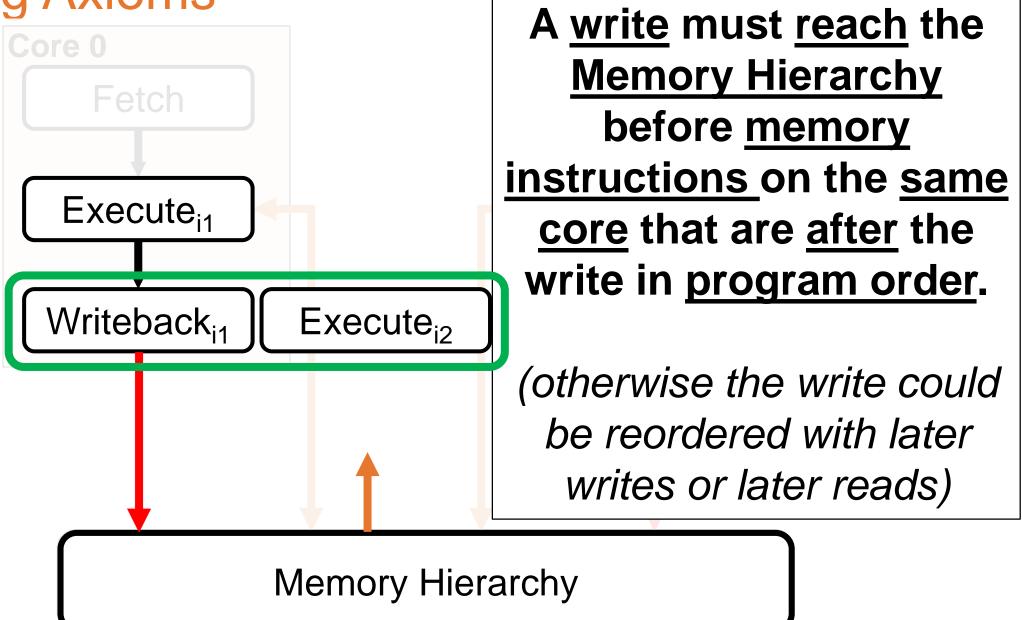

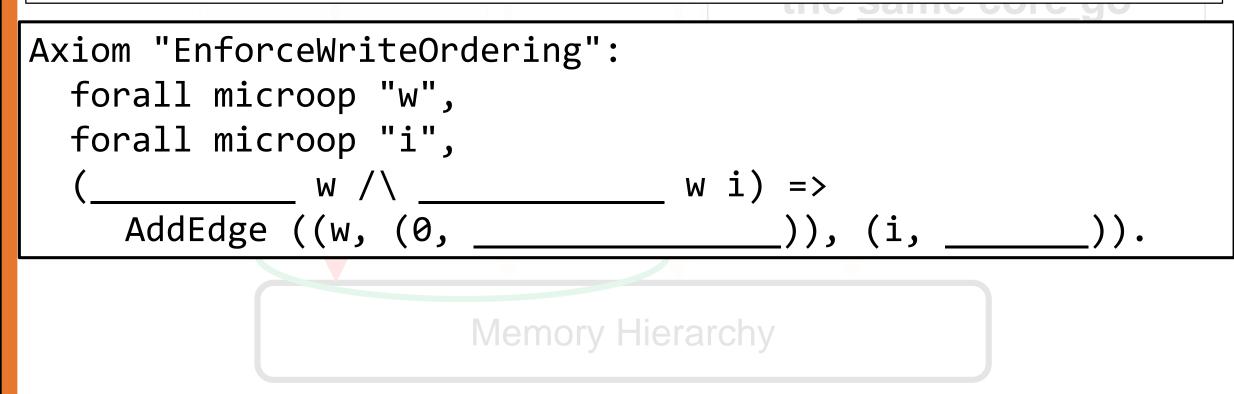

# The Enforce\_Write\_Ordering Axiom

SC\_fillable.uarch, line 87

A <u>write</u> must <u>reach</u> the <u>Memory Hierarchy</u> before <u>execution</u> of <u>memory instructions</u> that are <u>after</u> the write in <u>program order</u>.

# The Enforce\_Write\_Ordering Axiom

SC\_fillable.uarch, line 87

A <u>write</u> must <u>reach</u> the <u>Memory Hierarchy</u> before <u>execution</u> of <u>memory instructions</u> that are <u>after</u> the write in <u>program order</u>.

Axiom "EnforceWriteOrdering":

forall microop "w",

forall microop "i",

(IsAnyWrite w /\ ProgramOrder w i) =>

AddEdge ((w, (0, MemoryHierarchy)), (i, Execute)).

Memory Hierarchy

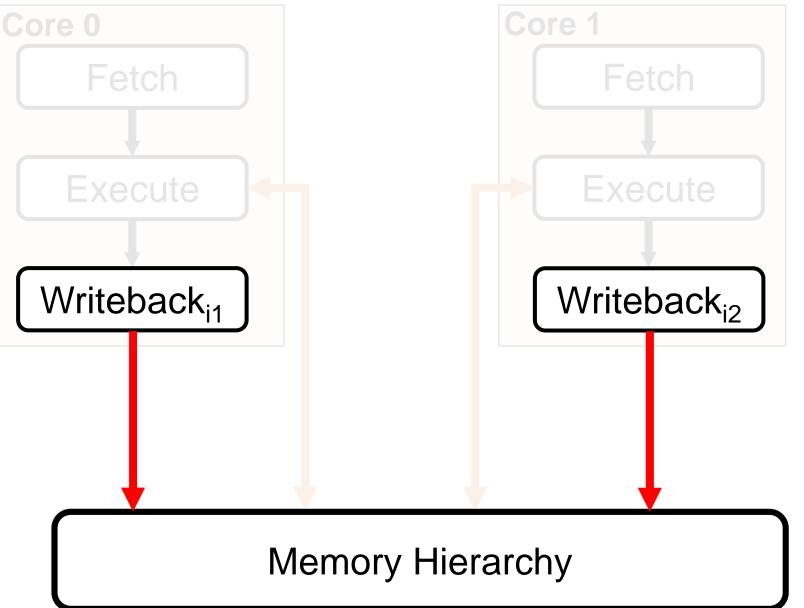

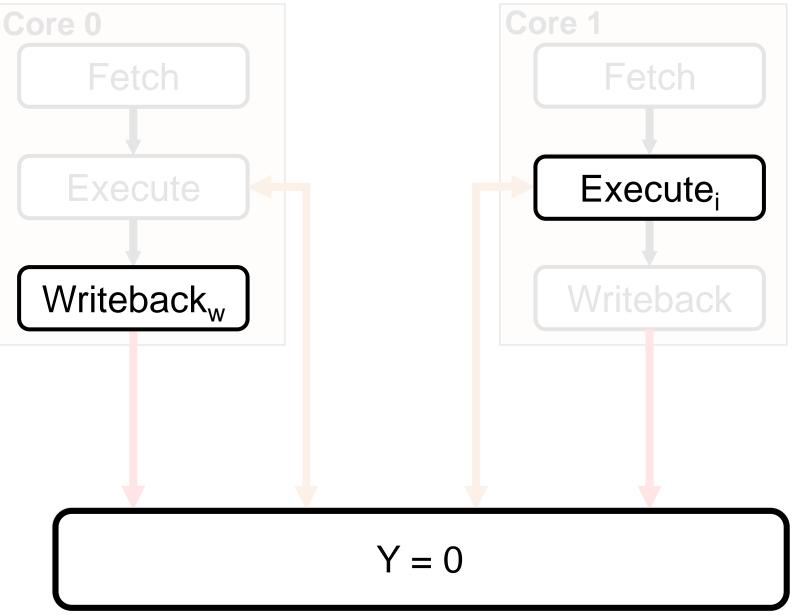

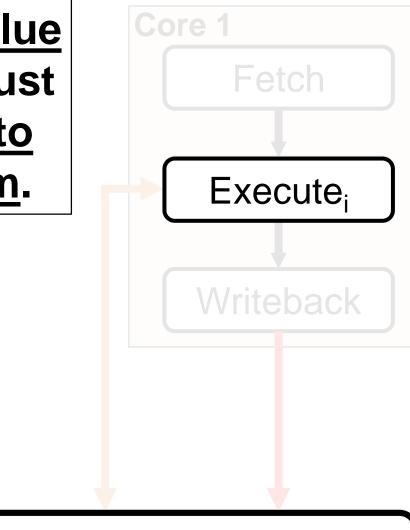

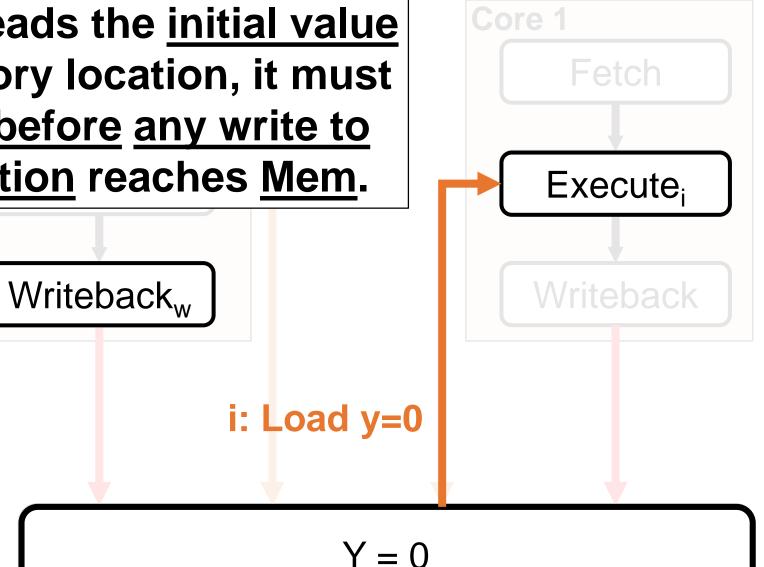

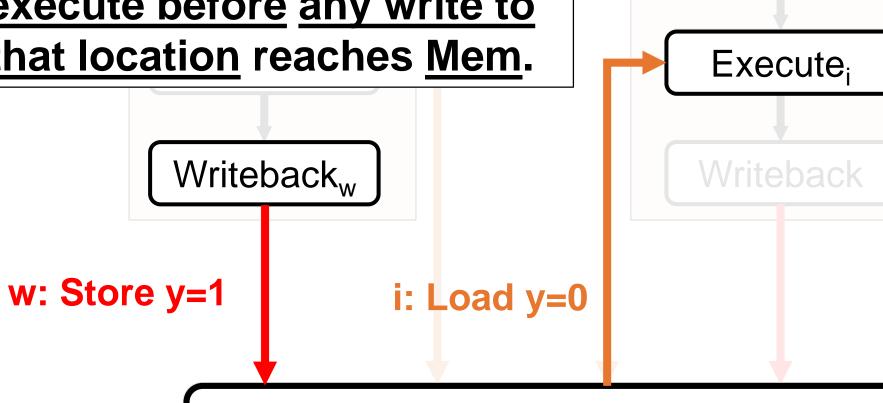

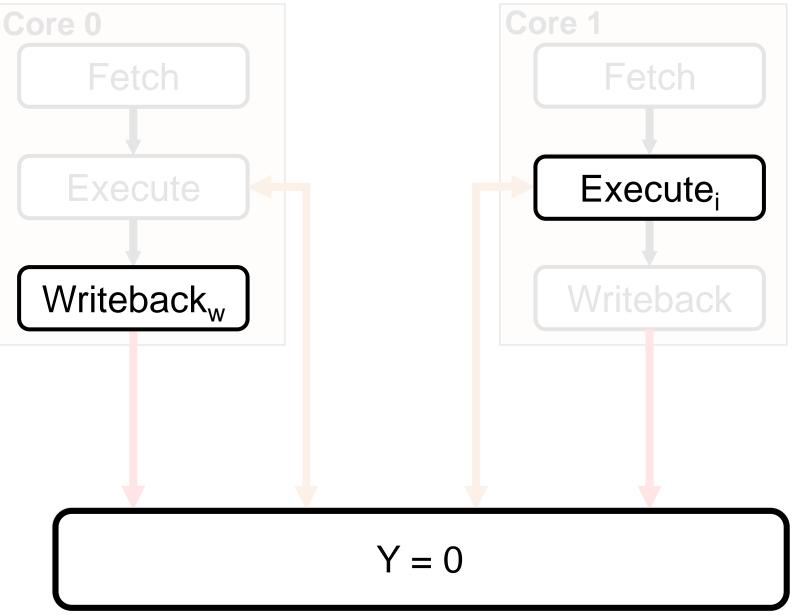

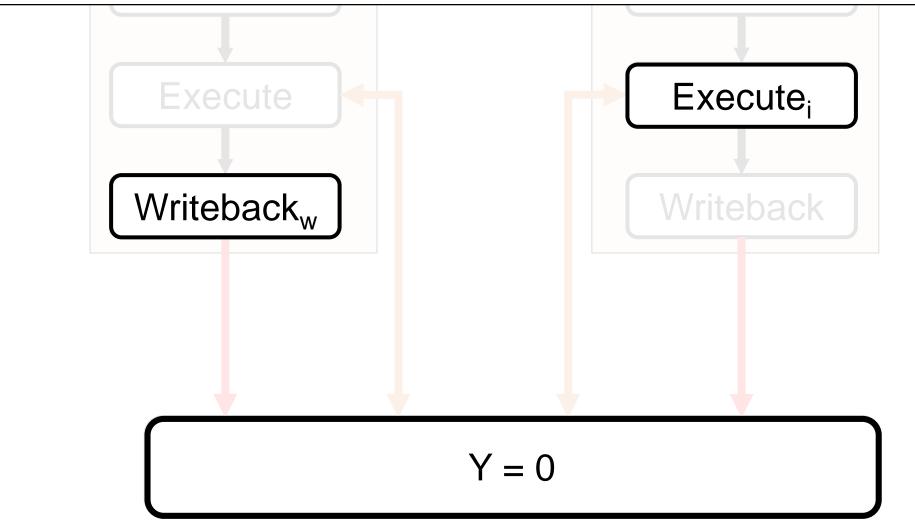

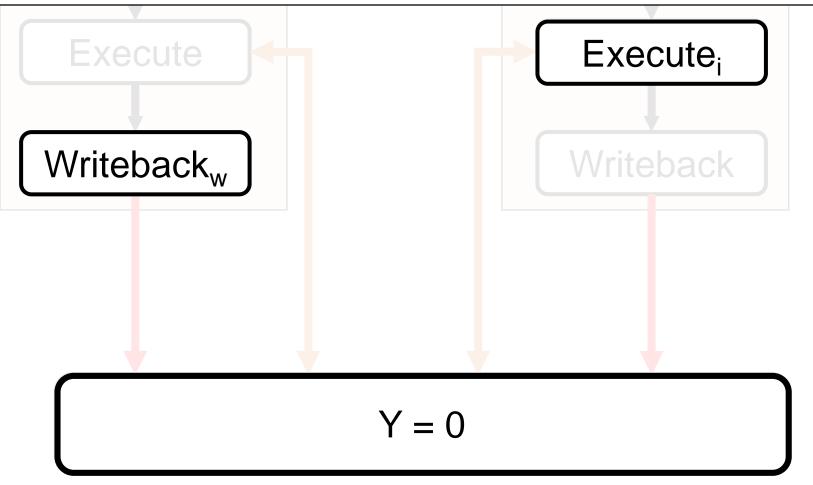

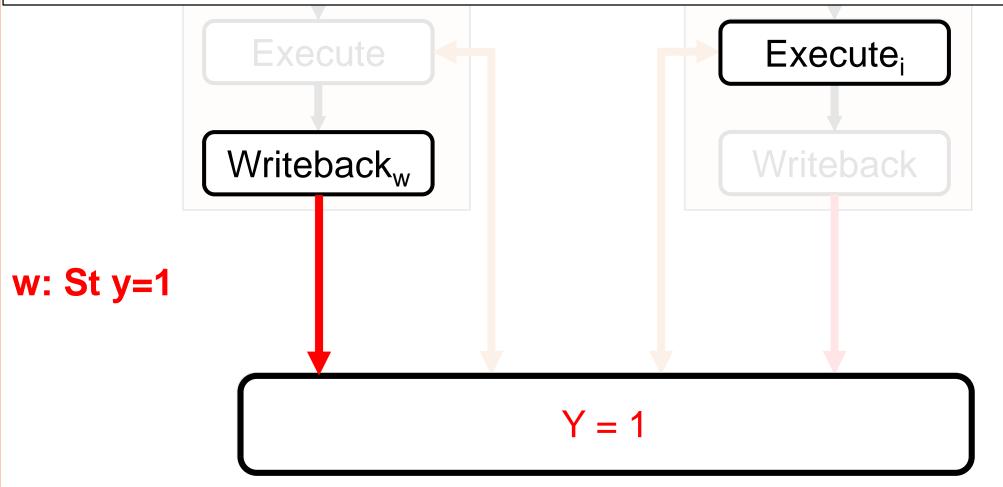

If a <u>load</u> reads the <u>initial value</u> of a memory location, it must <u>execute before any write to</u> <u>that location</u> reaches <u>Mem</u>.

Writeback<sub>w</sub>

$$Y = 0$$

If a load reads the initial value of a memory location, it must execute before any write to that location reaches Mem.

If a <u>load</u> reads the <u>initial value</u> of a memory location, it must <u>execute before any write to</u> <u>that location</u> reaches <u>Mem</u>.

Core 1

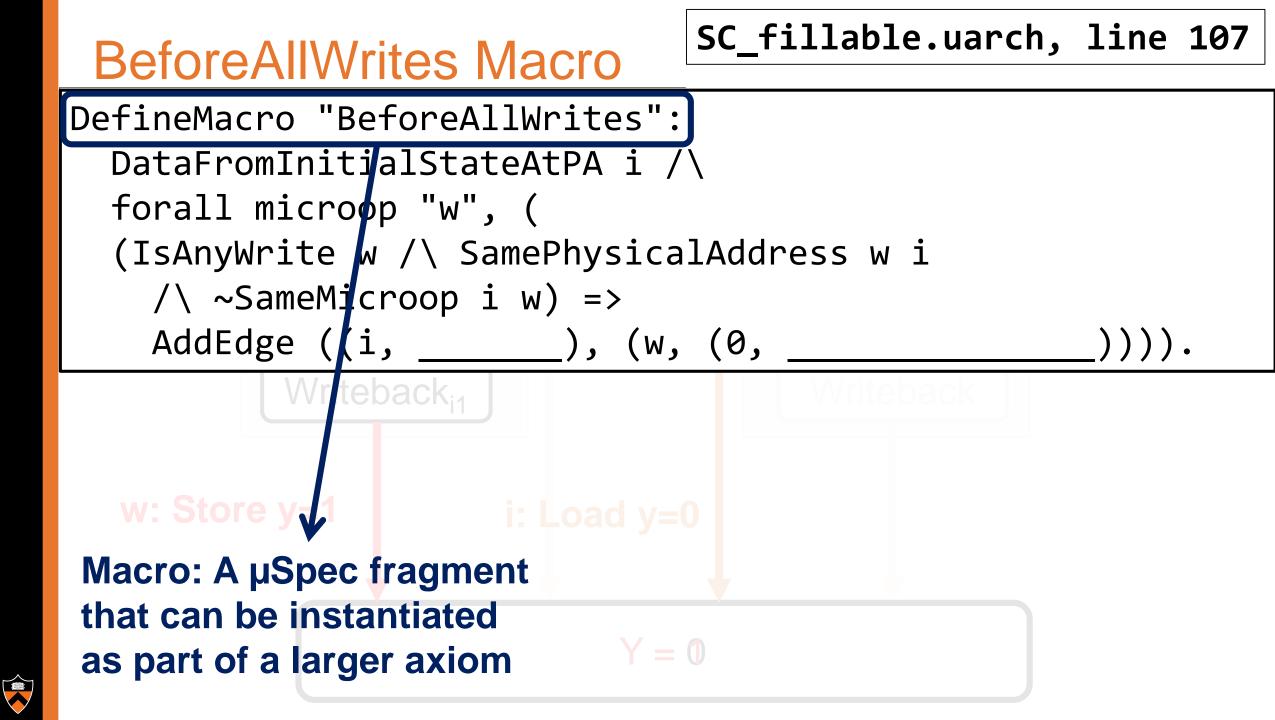

# **BeforeAllWrites Macro**

DefineMacro "BeforeAllWrites": DataFromInitialStateAtPA i /\ forall microop "w", ( (IsAnyWrite w /\ SamePhysicalAddress w i /\ ~SameMicroop i w) => )))). AddEdge ((i, ), (w, (0, Writeback<sub>i1</sub>

SC fillable.uarch, line 107

# **BeforeAllWrites Macro**

```

DefineMacro "BeforeAllWrites":

DataFromInitialStateAtPA i /\

forall microop "w", (

(IsAnyWrite w /\ SamePhysicalAddress w i

/\ ~SameMicroop i w) =>

AddEdge ((i, ____), (w, (0, _____)))).

If a load reads the initial value of a memory location, it

```

SC fillable.uarch, line 107

must execute before any write to that addr reaches Mem.

Y = 0

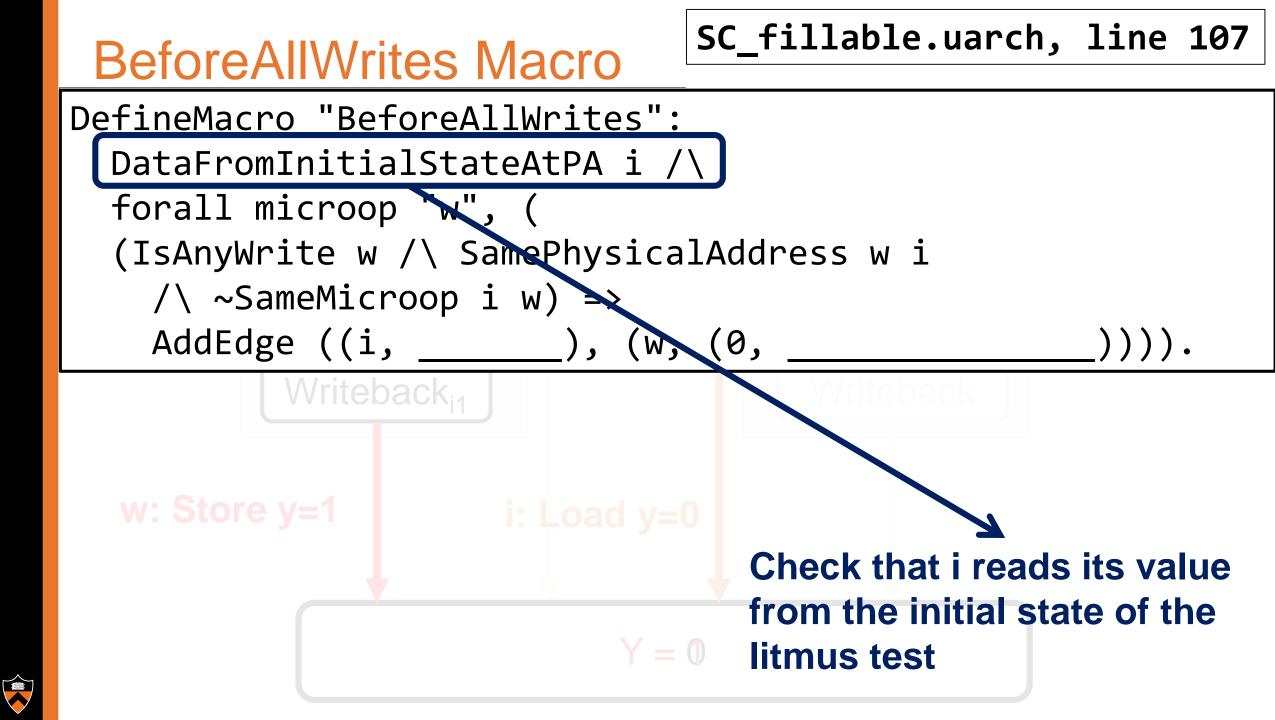

# **BeforeAllWrites Macro**

```

DefineMacro "BeforeAllWrites":

DataFromInitialStateAtPA i /\

forall microop "w", (

(IsAnyWrite w /\ SamePhysicalAddress w i

/\ ~SameMicroop i w) =>

AddEdge ((i, Execute), (w, (0, MemoryHierarchy)))).

If a load reads the initial value of a memory location, it

```

SC fillable.uarch, line 107

must execute before any write to that addr reaches Mem.

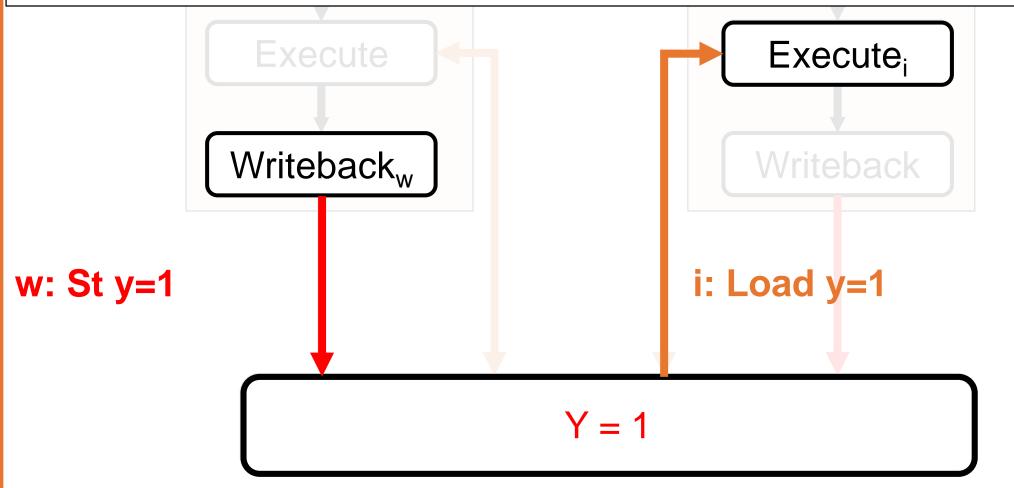

tore y=1 i: Load y=0 Y = 0

### SC fillable.uarch, line 107 **BeforeAllWrites Macro** DefineMacro "BeforeAllWrites": DataFromInitialStateAtPA i /\ forall microop "w", ( (IsAnyWrite w /∖ SamePhysicalAddress w i /\ ~SameMicroop i w) => AddEdge ((i, Execute), (w, (0, MemoryHierarchy)))). If a load reads the initial value of a memory location, it must execute before any write to that addr reaches Mem. V Enforce that the load executes before all writes to its address in the test

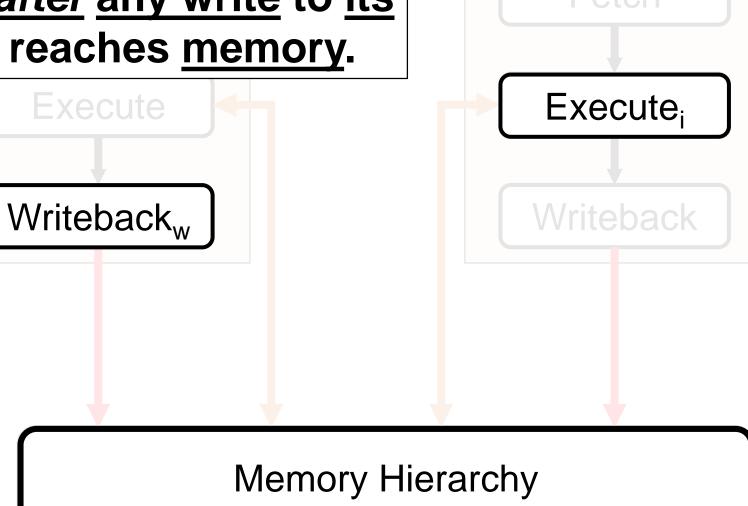

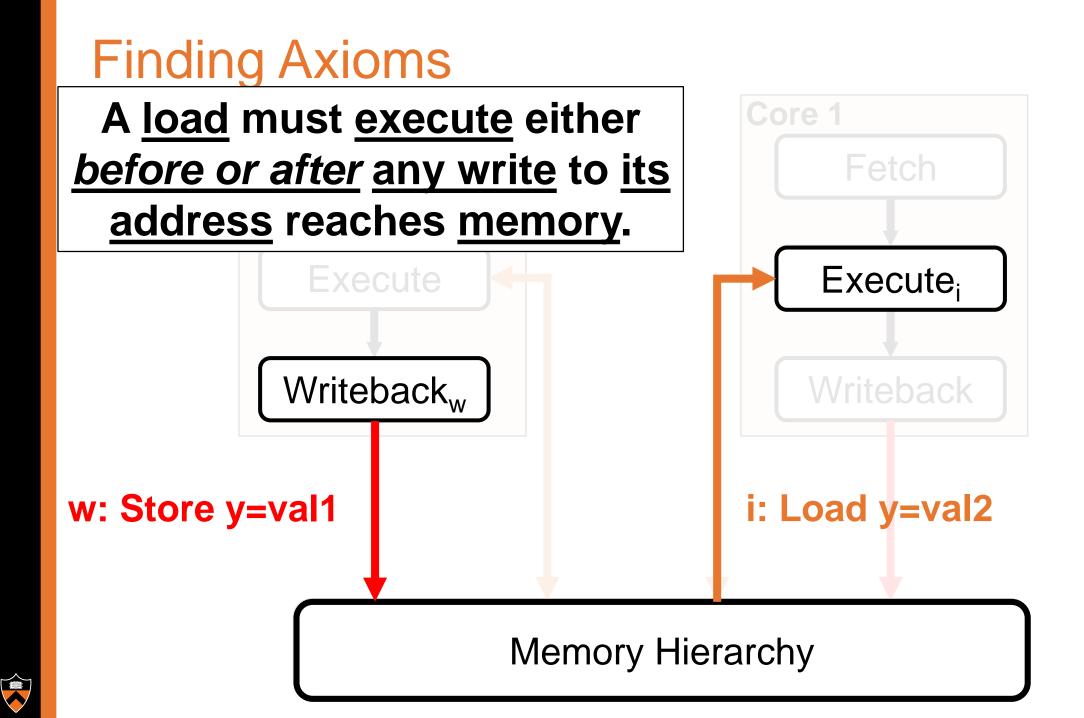

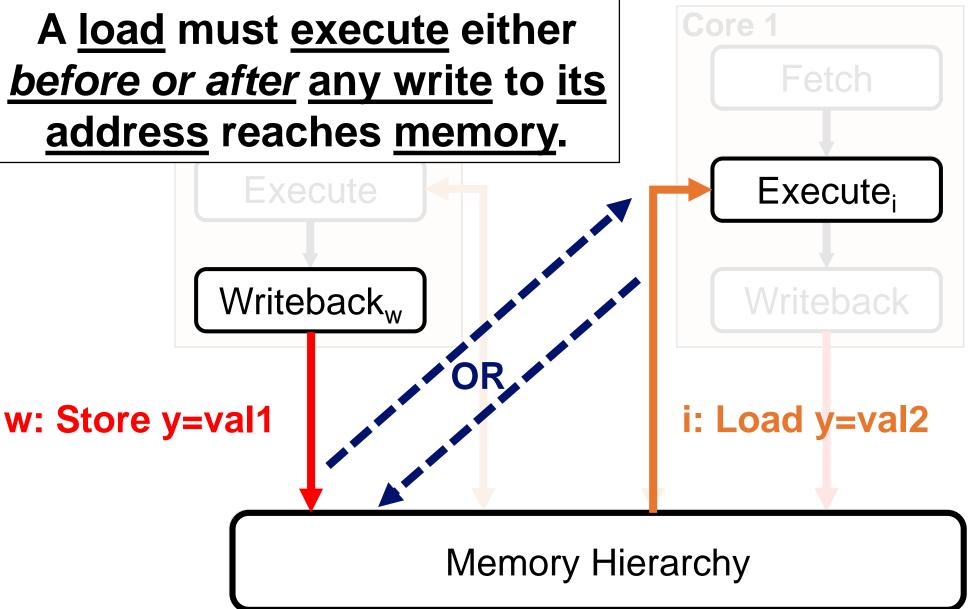

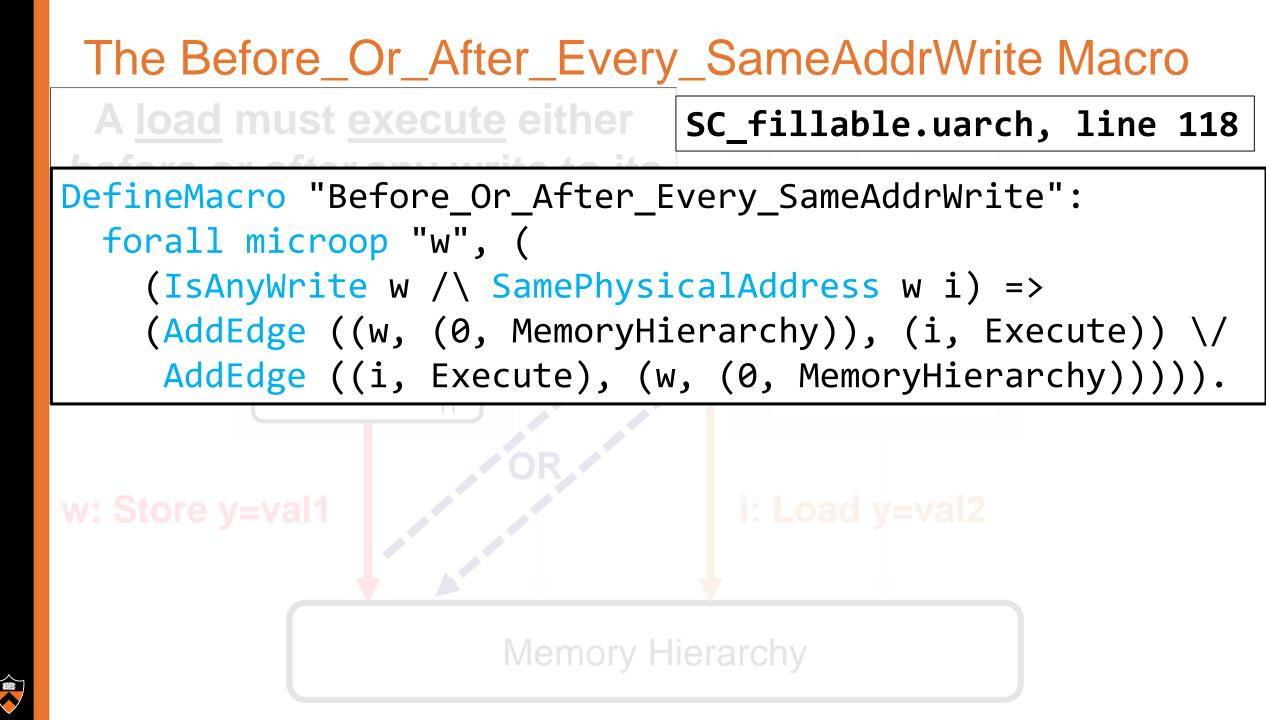

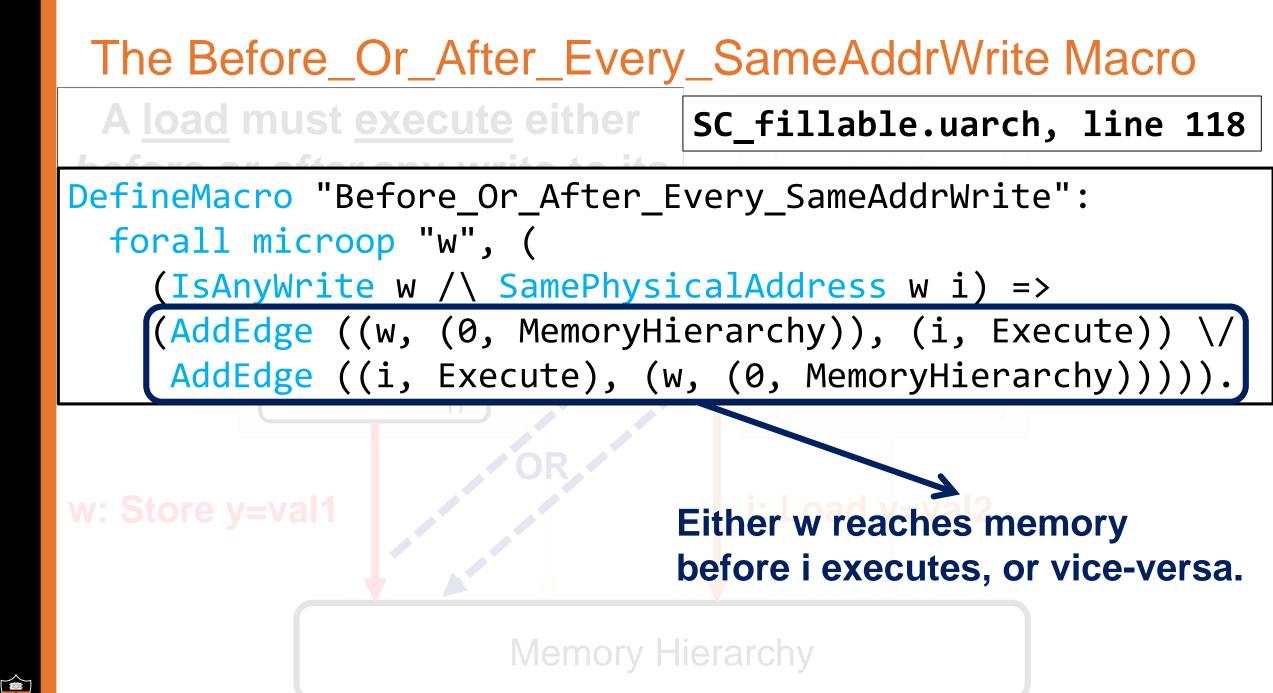

A load must execute either <u>before or after any write</u> to its <u>address reaches memory.</u>

# A load must read from the latest write to that address to reach memory.

Alternatively:

1) The load must execute after the write it reads from

2) <u>No writes to that address between the source write and the read</u>

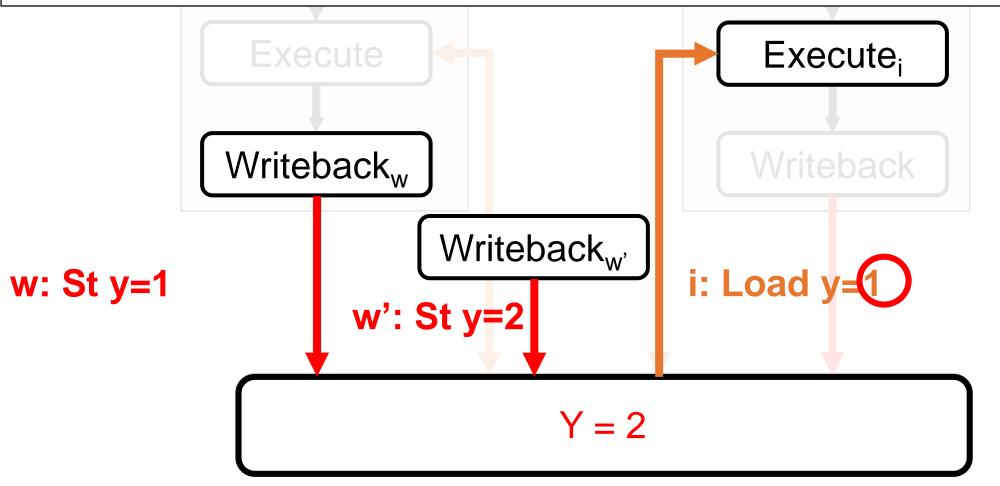

Alternatively:

1) The load must execute after the write it reads from

2) <u>No writes</u> to <u>that address</u> <u>between</u> the <u>source</u> write and the <u>read</u>

Alternatively:

1) The load must execute after the write it reads from

2) <u>No writes</u> to <u>that address</u> <u>between</u> the <u>source</u> write and the <u>read</u>

Alternatively:

1) The load must execute after the write it reads from

2) <u>No writes</u> to <u>that address</u> <u>between</u> the <u>source</u> write and the <u>read</u>

#### The No\_SameAddrWrites\_Btwn\_Src\_And\_Read Macro SC fillable.uarch, line 135 **Alternatively:** DefineMacro "No SameAddrWrites Btwn Src And Read": exists microop "w", ( IsAnyWrite w /\ wi/\ wi /\ AddEdge ((w, (0, MemHier)), (i, Execute)) /\ ~(exists microop "w'", IsAnyWrite w' /\ i w' /\ ~SameMicroop w w' /\ EdgesExist [((w, (0,MemHier)), (w', (0,MemHier))); ((w', (0,MemHier)), (i, Execute))])).

The load must <u>execute after</u> the <u>write it reads from</u>

<u>No writes</u> to <u>that address between</u> the <u>source</u> write and the <u>read</u>

### The No\_SameAddrWrites\_Btwn\_Src\_And\_Read Macro

#### **Alternatively:**

#### SC\_fillable.uarch, line 135

DefineMacro "No\_SameAddrWrites Btwn Src And Read": exists microop "w", ( IsAnyWrite w /\ SamePhysicalAddress w i /\ SameData w i /\ AddEdge ((w, (0, MemoryHierarchy)), (i, Execute)) /\ ~(exists microop "w'", IsAnyWrite w' /\ SamePhysicalAddress i w' /\ ~SameMicroop w w' /\ EdgesExist [((w, (0, MemHier)), (w', (0, MemHier)));((w', (0,MemHier)), (i, Execute))])).

### The No SameAddrWrites\_Btwn\_Src\_And\_Read Macro SC fillable.uarch, line 135 Alternatively: DefineMacro "No SameAddrWrites Btwn Src And Read": exists microop "w", ( IsAnyWrite w /\ SamePhysicalAddress w i /\ SameData w i /\ AddEdge ((w, (0, MemoryHierarchy)), (i, Execute)) / ~(exists microop "w'", IsAnyWrite w' /\ SamePhysicalAddress i w' /\ ~SameMicroop w w' /\ EdgesExist [( w, (0,MemHier)), (w', (0,MemHier)); ((w', (0,MemHier)), (i, Execute))])). Read i executes after its source

write w reaches memory...

### The No SameAddrWrites\_Btwn\_Src\_And\_Read Macro SC fillable.uarch, line 135 **Alternatively:** DefineMacro "No SameAddrWrites Btwn Src And Read": exists microop "w", ( IsAnyWrite w /\ SamePhysicalAddress w i /\ SameData w i /\ AddEdge ((w, (0, MemoryHierarchy)), (i, Execute)) /\ ~(exists microop "w'", IsAnyWrite w' /\ SamePhysicalAddress i w' /\ ~SameMicroop w w' /\ EdgesExist [((w, (0,MemHier)), (w', (0,MemHier))); ((w', (0,MemHier)), (i, Execute))])). ...and there are no writes w' to that addr between the source write w and the read i.

```

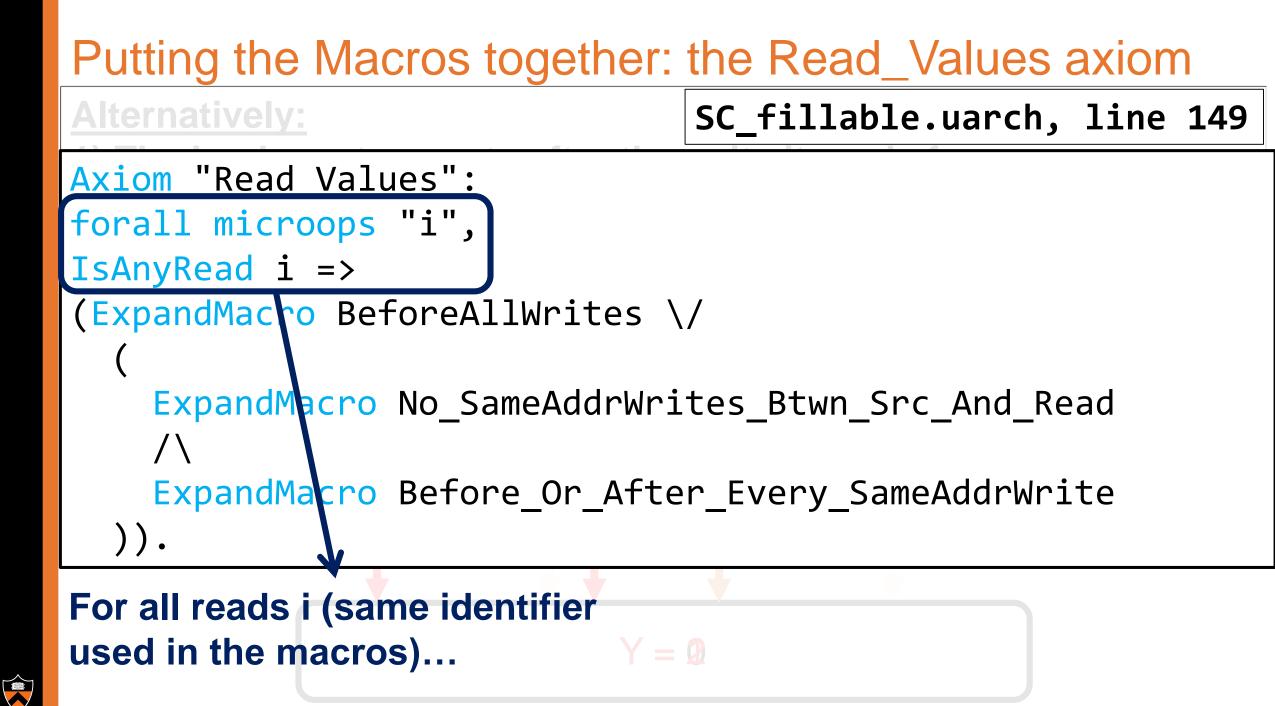

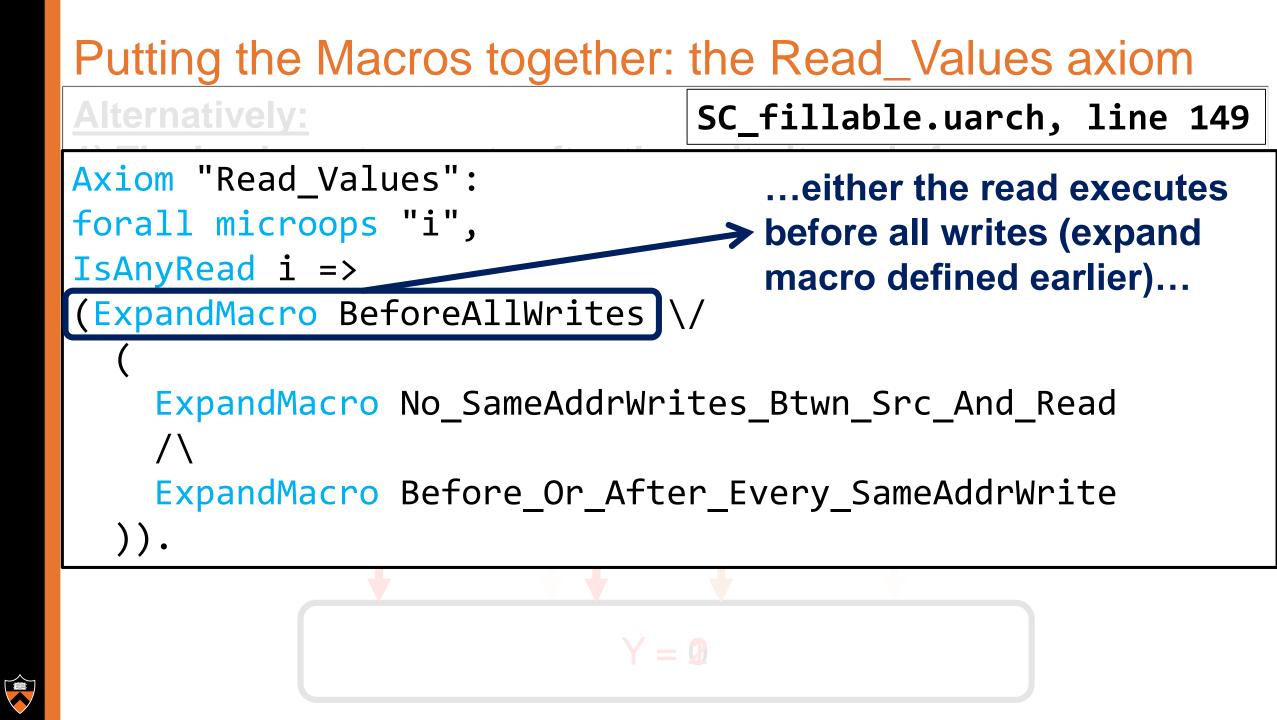

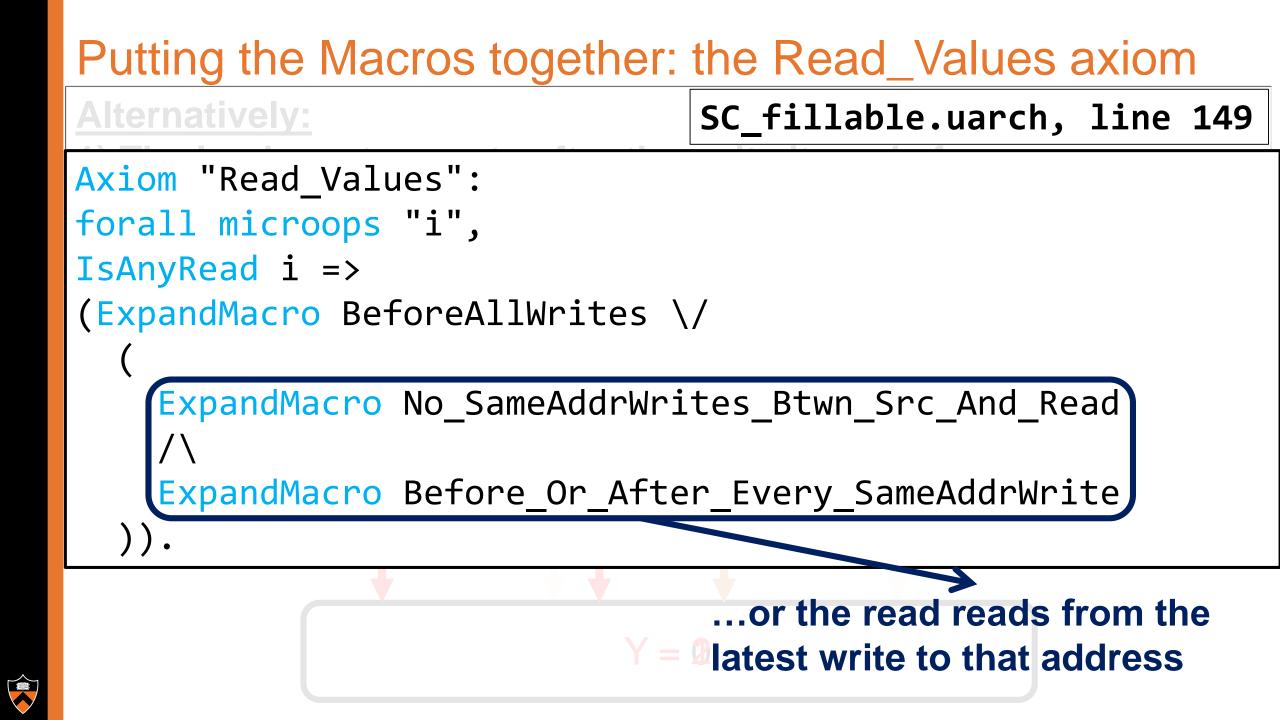

Putting the Macros together: the Read_Values axiom

Alternatively:

SC fillable.uarch, line 149

Axiom "Read Values":

forall microops "i",

IsAnyRead i =>

(ExpandMacro BeforeAllWrites \/

ExpandMacro No SameAddrWrites Btwn Src And Read

/

ExpandMacro Before Or After Every SameAddrWrite

)).

```

| i1: Store [x] ← 1<br>i2: Store [x] ← 2 |  |

|----------------------------------------|--|

|                                        |  |

**MemHier**

### Test your completed SC uarch!

# Assuming you are in ~/pipecheck\_tutorial/uarches/

\$ check -i ../tests/SC\_tests/co-mp.test -m SC\_fillable.uarch

# If your uarch is valid, the above will create co-mp.pdf in your # current directory (open pdfs from command line with evince) # To run the solution version of the SC uarch on this test: # (Note: this will overwrite the co-mp.pdf in your current folder) \$ check -i ../tests/SC\_tests/co-mp.test -m SC.uarch -d solutions/

# If you get an error (cannot parse uarch, ps2pdf crashes, etc), # examine your syntax or ask for help. # If the outcome is observable ("BUG"), compare the graphs # generated by the solution uarch to those of your uarch.

# To compare the uarches themselves:

\$ diff SC\_fillable.uarch solutions/SC.uarch

### Run the entire suite of SC litmus tests!

# Assuming you are in ~/pipecheck\_tutorial/uarches/

\$ run\_tests -v 2 -t ../tests/SC\_tests/ -m SC\_fillable.uarch

# The above will generate \*.gv files in ~/pipecheck\_tutorial/out/ # for all SC tests, and output overall statistics at the end. If # the count for "Buggy" is non-zero, your uarch is faulty. Look for the tests that output "BUG" to find out which tests fail.

# You can use gen\_graph to convert gv files into PDFs:

\$ gen\_graph -i <test\_gv\_file>

# Compare your uarch with the solution SC uarch using diff to find # discrepancies:

\$ diff SC\_fillable.uarch solutions/SC.uarch

### **Coffee Break!**

### After the break: Extending SC uarch. to TSO

### **PipeCheck Hands-On Continued:**

### **Extending SC uarch. to TSO**

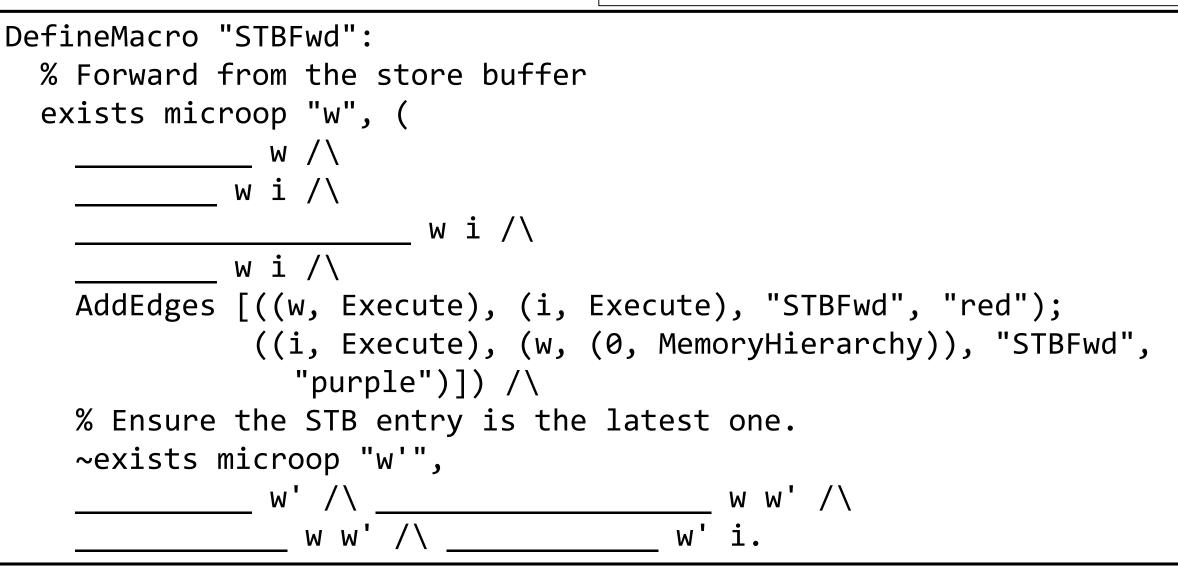

# Hands-on: Moving from SC to TSO

- Reads must currently wait for prior writes to reach memory

- EnforceWriteOrdering axiom

- Low performance!

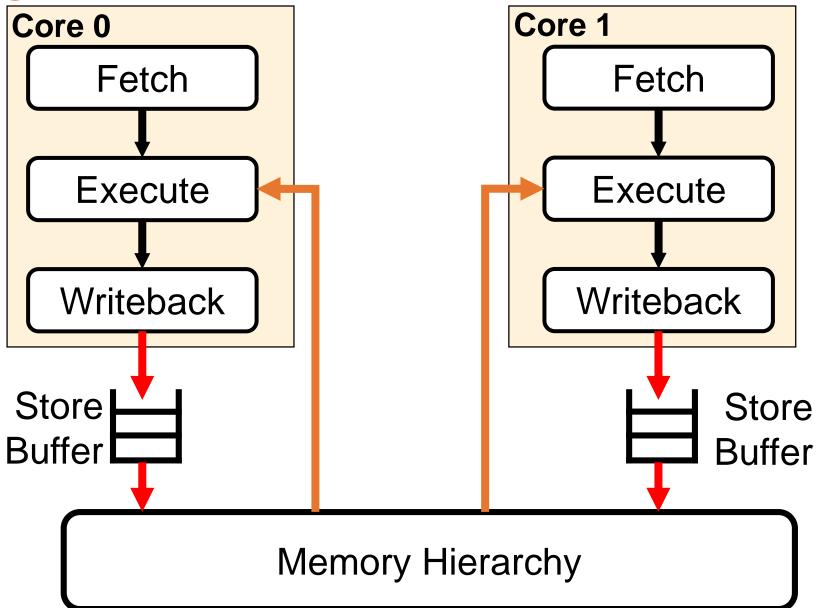

- Main motivation for TSO: store buffers to hide write latency

- Allow reads to be *reordered* with writes

- Also want to allow reads to bypass value from store buffer (before value made visible to other cores)

- Known as "read your own write early"

- How to model this in µSpec?

### Moving from SC to TSO

### Moving from SC to TSO

### Moving from SC to TSO

#### Moving from SC to TSO Core 0 Fetch Fetch Fetch

### Partially completed TSO uarch in

/home/check/pipecheck\_tutorial/uarches/TSO\_fillable.uarch

(i.e. ~/pipecheck\_tutorial/uarches/TSO\_fillable.uarch)

### Some axioms remain the same from SC.uarch

- 7 changes needed to SC.uarch:

- 1. Add store buffer stage

# Add StoreBuffer Stage

- "StoreBuffer" stage is between Writeback and MemoryHierarchy

- Solution:

| StageName _ | ·· ·               |  |

|-------------|--------------------|--|

| StageName _ | "MemoryHierarchy". |  |

# Add StoreBuffer Stage

#### TSO\_fillable.uarch, line 39

"StoreBuffer" stage is between Writeback and MemoryHierarchy

Solution:

StageName 3 "StoreBuffer".

StageName 4 "MemoryHierarchy".

- 7 changes needed to SC.uarch:

- 1. Add store buffer stage

- 2. Make writes go through SB before memory

# Writes Go Through SB

#### TSO\_fillable.uarch, line 55

• Modify Writes\_Path axiom so stores go WB  $\rightarrow$  SB  $\rightarrow$ MemHier

Solution:

```

Axiom "Writes Path":

forall microops "i",

IsAnyWrite i =>

AddEdges [((i, Fetch), (i, Execute), "path");

((i, Execute), (i, Writeback),

"path");

((i, _____), (i, _____), "path");

((i, _____), (i, (0, _____)

"path")

.

```

# Writes Go Through SB

#### TSO\_fillable.uarch, line 55

■ Modify Writes\_Path axiom so stores go WB  $\rightarrow$  SB  $\rightarrow$ MemHier

Solution:

```

Axiom "Writes Path":

forall microops "i",

IsAnyWrite i =>

AddEdges [((i, Fetch), (i, Execute), "path");

((i, Execute), (i, Writeback), "path");

((i, Writeback), (i, StoreBuffer), "path");

((i, StoreBuffer), (i, (0, MemoryHierarchy)),

"path")

•

```

#### 7 changes needed to SC.uarch:

- 1. Add store buffer stage

- 2. Make writes go through SB before memory

- 3. Ensure that same-core writes go through SB in order

# Same-Core Writes Go Through SB in order

TSO\_fillable.uarch, line 106

- If same-core writes go through WB in order, they should go through SB in order too

- Hint: Use Writeback\_stage\_is\_in\_order axiom as a starting point

Solution:

```

Axiom "StoreBuffer_stage_is_in_order":

forall microops "i1",

forall microops "i2",

IsAnyWrite i1 /\ IsAnyWrite i2 /\ ______ i1 i2 =>

EdgeExists ((i1, _____), (i2, _____), "") =>

AddEdge ((i1, _____), (i2, _____), "PPO",

"darkgreen").

```

# Same-Core Writes Go Through SB in order

TSO\_fillable.uarch, line 106

- If same-core writes go through WB in order, they should go through SB in order too

- Hint: Use Writeback\_stage\_is\_in\_order axiom as a starting point

Solution:

```

Axiom "StoreBuffer_stage_is_in_order":

forall microops "i1",

forall microops "i2",

IsAnyWrite i1 /\ IsAnyWrite i2 /\ SameCore i1 i2 =>

EdgeExists ((i1, Writeback), (i2, Writeback), "") =>

AddEdge ((i1, StoreBuffer), (i2, StoreBuffer), "PPO",

"darkgreen").

```

#### 7 changes needed to SC.uarch:

- 1. Add store buffer stage

- 2. Make writes go through SB before memory

- 3. Ensure that same-core writes go through SB in order

- 4. Enforce that write is released from SB only after all prior same-core writes have reached memory

# Same-Core Writes Reach Memory In Order

TSO\_fillable.uarch, line 141

- For two same-core writes in program order, first write must reach memory before second can leave store buffer

- Hint: Axiom should only apply to pairs of writes!

Solution:

```

Axiom "EnforceWriteOrdering":

forall microop "w",

forall microop "w'",

(IsAnyWrite w /\_____ w' /\_____ w w') =>

AddEdge ((w, (0, ______)), (w', _____),

"one_at_a_time", "green").

```

# Same-Core Writes Reach Memory In Order

TSO\_fillable.uarch, line 141

- For two same-core writes in program order, first write must reach memory before second can leave store buffer

- Hint: Axiom should only apply to pairs of writes!

Solution:

```

Axiom "EnforceWriteOrdering":

forall microop "w",

forall microop "w'",

(IsAnyWrite w /\ IsAnyWrite w' /\ ProgramOrder w w') =>

AddEdge ((w, (0, MemoryHierarchy)), (w', StoreBuffer),

"one_at_a_time", "green").

```

#### 7 changes needed to SC.uarch:

- 1. Add store buffer stage

- 2. Make writes go through SB before memory

- 3. Ensure that same-core writes go through SB in order

- 4. Enforce that write is released from SB only after all prior same-core writes have reached memory

- 5. Ensure that if load is reading from memory, that core's store buffer has no entries for address of load

# Only read from Mem if SB has no same addr writes

TSO\_fillable.uarch, line 169

Create a macro enforcing that all writes before instr "i" in program order to address of "i" have reached mem before "i" Executes

Solution:

# Only read from Mem if SB has no same addr writes

TSO\_fillable.uarch, line 169

Create a macro enforcing that all writes before instr "i" in program order to address of "i" have reached mem before "i" Executes

Solution:

```

DefineMacro "STBEmpty":

% Store buffer is empty for the address we want to read.

forall microop "w", (

(IsAnyWrite w /\ SamePhysicalAddress w i /\

ProgramOrder w i) =>

AddEdge ((w, (0, MemoryHierarchy)), (i, Execute),

"STBEmpty", "purple")).

```

### Only read from Mem if SB has no same addr writes TSO\_fillable.uarch, line 226

Now expand the macro in Read\_Values axiom to ensure that SB has no entries for a load's address if it is reading from memory

### Only read from Mem if SB has no same addr writes

```

Axiom "Read Values":

forall microops "i",

IsAnyRead i => (

% Uncomment the commented lines if you add the (advanced) store buff forwarding.

ExpandMacro _____ \/

%

%

ExpandMacro _____ /\

ExpandMacro BeforeAllWrites

ExpandMacro No SameAddrWrites Btwn Src And Read

ExpandMacro Before_Or_After_Every_SameAddrWrite

%

```

### Only read from Mem if SB has no same addr writes

```

Axiom "Read Values":

forall microops "i",

IsAnyRead i => (

% Uncomment the commented lines if you add the (advanced) store buff forwarding.

ExpandMacro _____ \/

%

%

ExpandMacro STBEmpty /\

ExpandMacro BeforeAllWrites

ExpandMacro No SameAddrWrites Btwn Src And Read

ExpandMacro Before_Or_After_Every_SameAddrWrite

%

```

#### 7 changes needed to SC.uarch:

- 1. Add store buffer stage

- 2. Make writes go through SB before memory

- 3. Ensure that same-core writes go through SB in order

- 4. Enforce that write is released from SB only after all prior same-core writes have reached memory

- 5. Ensure that if load is reading from memory, that core's store buffer has no entries for address of load

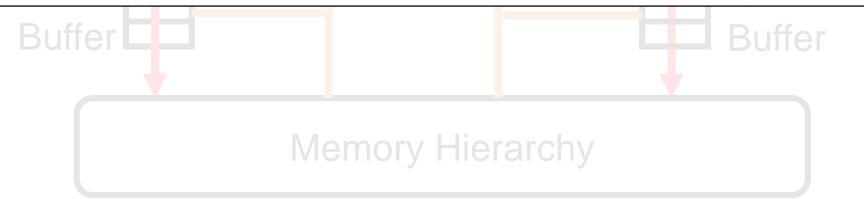

- 6. (Advanced) Allow a core to read value of a write from its store buffer before write is made visible to other cores

# Forward Value from SB (Advanced)

- Create a macro that checks for a write on the same core to forward from (Execute stage -> Execute stage), and ensures the forwarding occurs before the write reaches memory

- Macro must also check that forwarding occurs from the latest write in program order (no intervening writes)

- Solution:

# Forward Value from SB (Advanced)

# Forward Value from SB (Advanced)

```

DefineMacro "STBFwd":

% Forward from the store buffer

exists microop "w", (

IsAnyWrite w /\

SameCore w i /

SamePhysicalAddress w i /

SameData w i /\

AddEdges [((w, Execute), (i, Execute), "STBFwd", "red");

((i, Execute), (w, (0, MemoryHierarchy)), "STBFwd",

"purple")]) /\

% Ensure the STB entry is the latest one.

~exists microop "w'",

IsAnyWrite w' /\ SamePhysicalAddress w w' /\

ProgramOrder w w' /\ ProgramOrder w' i.

```

# Forward Value from SB TS0\_fillable.uarch, line 226

- Expand the macro in the Read\_Values axiom so that forwarding from the SB is an *alternative* choice to reading from memory

- Remember to uncomment lines 231-232, and line 243!

- Solution:

```

Axiom "Read Values":

TSO_fillable.uarch, line 226

forall microops "i",

IsAnyRead i =>

ExpandMacro \/

ExpandMacro STBEmpty /\

ExpandMacro BeforeAllWrites

ExpandMacro No SameAddrWrites Btwn Src And Read

ExpandMacro Before Or After Every SameAddrWrite

```

```

Axiom "Read Values":

TSO_fillable.uarch, line 226

forall microops "i",

IsAnyRead i =>

ExpandMacro STBFwd \/

ExpandMacro STBEmpty /\

ExpandMacro BeforeAllWrites

ExpandMacro No SameAddrWrites Btwn Src And Read

ExpandMacro Before Or After Every SameAddrWrite

```

#### 7 changes needed to SC.uarch:

- 1. Add store buffer stage

- 2. Make writes go through SB before memory

- 3. Ensure that same-core writes go through SB in order

- 4. Enforce that write is released from SB only after all prior same-core writes have reached memory

- 5. Ensure that if load is reading from memory, that core's store buffer has no entries for address of load

- 6. (Advanced) Allow a core to read value of a write from its store buffer before write is made visible to other cores

- 7. Implement fence operation that flushes all prior writes to memory before any succeeding instructions can perform

### Fence Instruction Orders Write-Read pairs TS0\_fillable.uarch, line 300

- Add a fence instruction that flushes all prior writes in program order to memory before the fence's execute stage

- Solution:

# Fence Instruction Orders Write-Read pairs

```

Axiom "Fence Ordering":

forall microops "f",

IsAnyFence f =>

AddEdges [((f, Fetch),

(f, Execute), "path");

((f, Execute), (f, Writeback), "path")]

/

forall microops "w",

(______ W /\

_ w f) =>

AddEdge ((w, (0, _____)), (f, _____),

"fence", "orange")

```

# Fence Instruction Orders Write-Read pairs

```

Axiom "Fence Ordering":

forall microops "f",

IsAnyFence f =>

AddEdges [((f, Fetch),

(f, Execute), "path");

(f, Writeback), "path")]

((f, Execute),

/

forall microops "w",

(IsAnyWrite w /\ ProgramOrder w f) =>

AddEdge ((w, (0, MemoryHierarchy)), (f, Execute),

"fence", "orange")

```

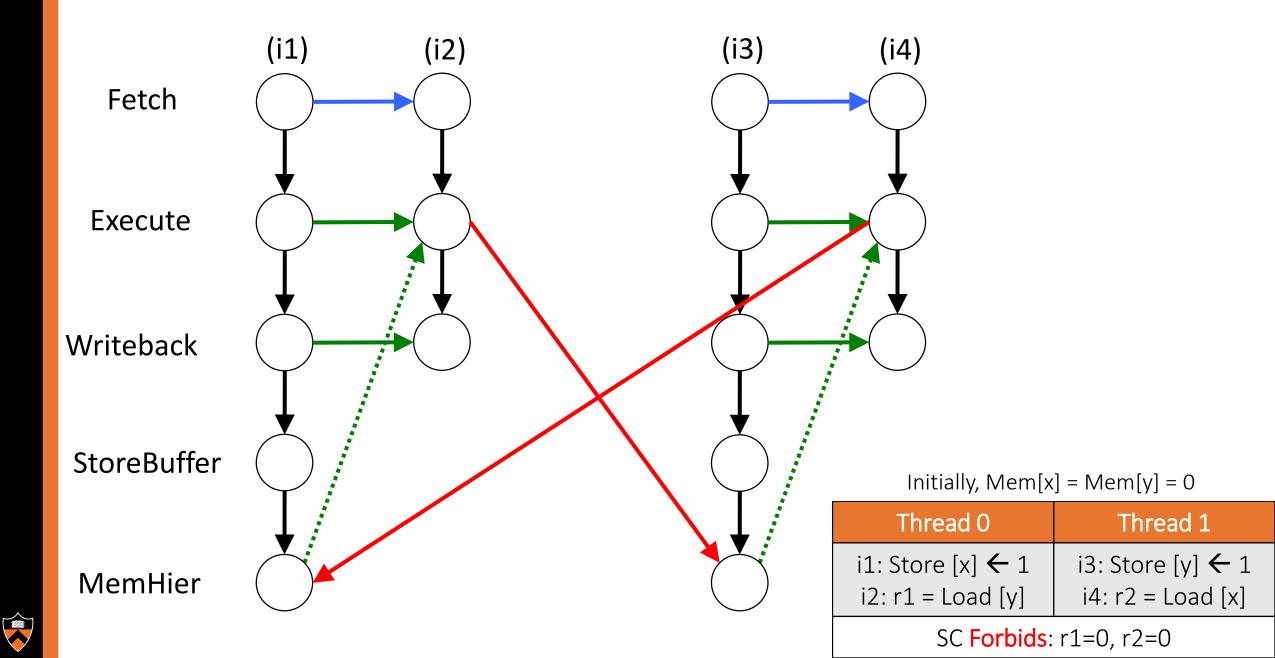

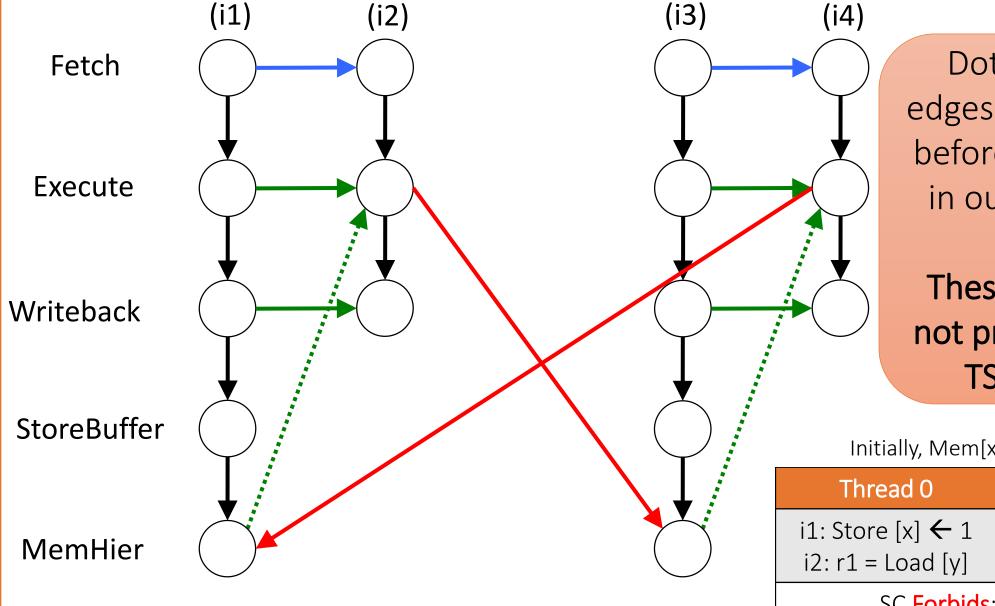

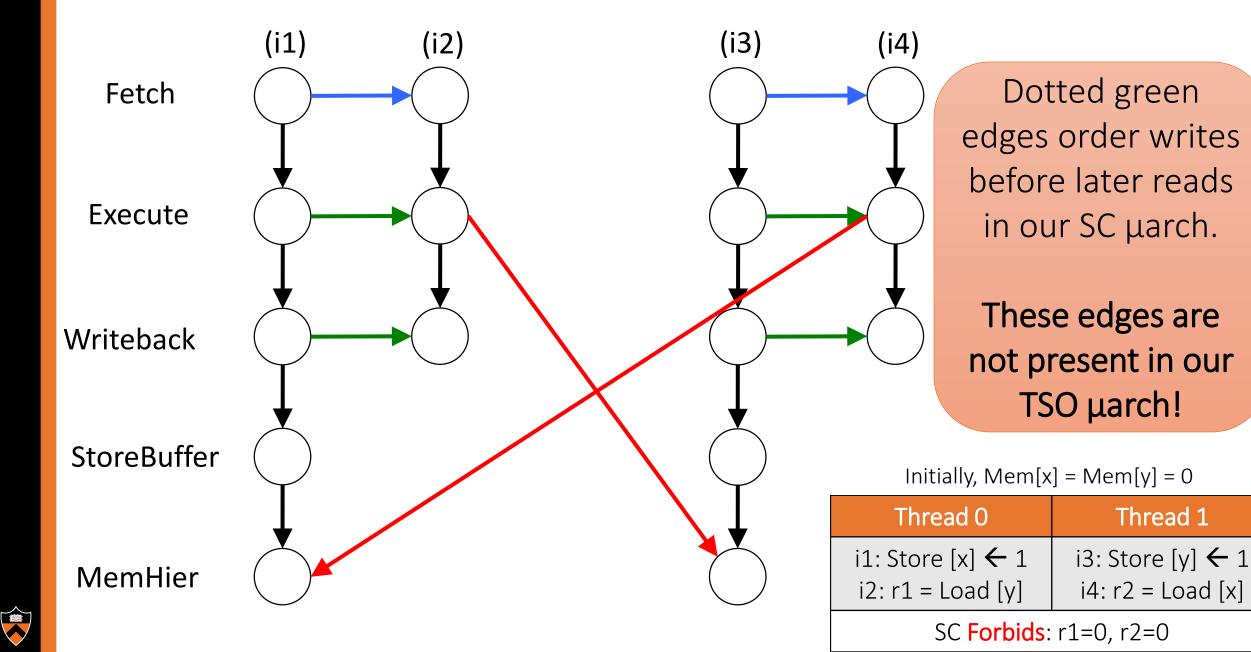

# µhb Graph for sb On TSO µarch.

# µhb Graph for sb On TSO µarch.

Dotted green edges order writes before later reads in our SC µarch.

These edges are not present in our TSO µarch!

Initially, Mem[x] = Mem[y] = 0

| Thread 0          | Thread 1          |

|-------------------|-------------------|

| i1: Store [x] ← 1 | i3: Store [y] ← 1 |

| i2: r1 = Load [y] | i4: r2 = Load [x] |

SC Forbids: r1=0, r2=0

# µhb Graph for sb On TSO µarch.

| Initially, Mem[x] = Mem[y] |  |

|----------------------------|--|

|----------------------------|--|

| · 1 i3: Store [y] ← 1<br>y] i4: r2 = Load [x] |

|-----------------------------------------------|

SC Forbids: r1=0, r2=0

### Test your completed TSO uarch!

# Assuming you are in ~/pipecheck\_tutorial/uarches/

\$ check -i ../tests/TSO\_tests/sb.test -m TSO\_fillable.uarch

# If your uarch is valid, the above will create sb.pdf in your # current directory (open pdfs from command line with evince) # To run the solution version of the TSO uarch on this test: # (Note: this will overwrite the sb.pdf in your current folder) \$ check -i ../tests/TSO\_tests/sb.test -m TSO.uarch -d solutions/

# If you get an error (cannot parse uarch, ps2pdf crashes, etc), # examine your syntax or ask for help. # If the outcome is not observable ("Strict"), compare the graphs # generated by the solution uarch to those of your uarch.

# To compare the uarches themselves:

\$ diff TSO\_fillable.uarch solutions/TSO.uarch

### Run the entire suite of TSO litmus tests!

# Assuming you are in ~/pipecheck\_tutorial/uarches/

\$ run\_tests -v 2 -t ../tests/TSO\_tests/ -m TSO\_fillable.uarch

# The above will generate \*.gv files in ~/pipecheck\_tutorial/out/ # for all TSO tests, and output overall statistics at the end. If # the count for "Buggy" is non-zero, your uarch is faulty. Look for the tests that output "BUG" to find out which tests fail.

# You can use gen\_graph to convert gv files into PDFs:

\$ gen\_graph -i <test\_gv\_file>

# Compare your uarch with the solution TSO uarch using diff to find # discrepancies:

\$ diff TSO\_fillable.uarch solutions/TSO.uarch

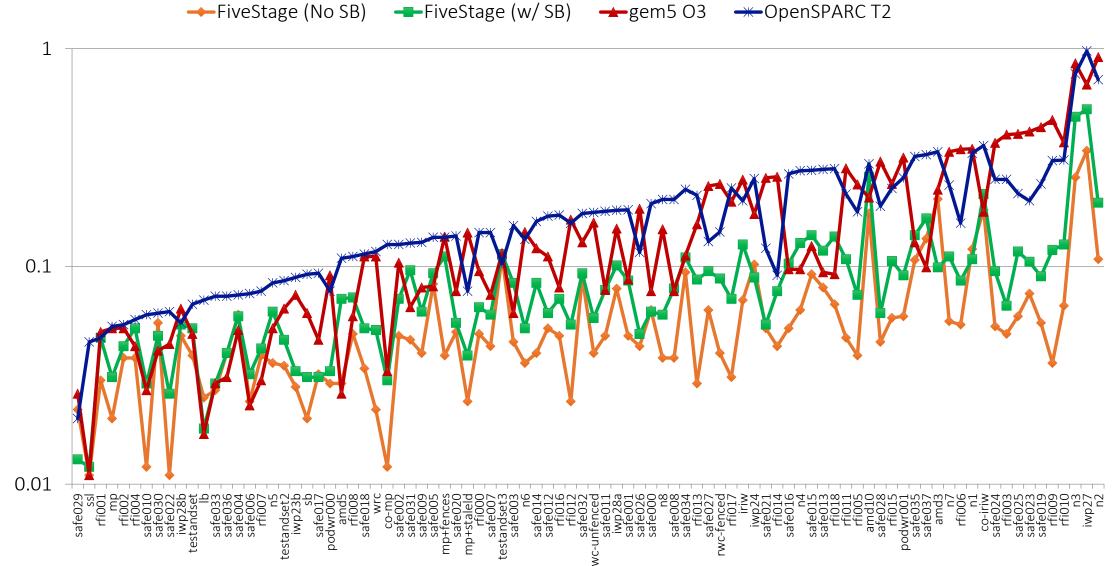

### **PipeCheck Verification Time**

Runtime (s)

### Covered the basics of what PipeCheck can do...

But there's more!

PipeCheck can handle heterogeneous pipelines:

### Covered the basics of what PipeCheck can do...

...and microarchitectural optimizations...

### Covered the basics of what PipeCheck can do...

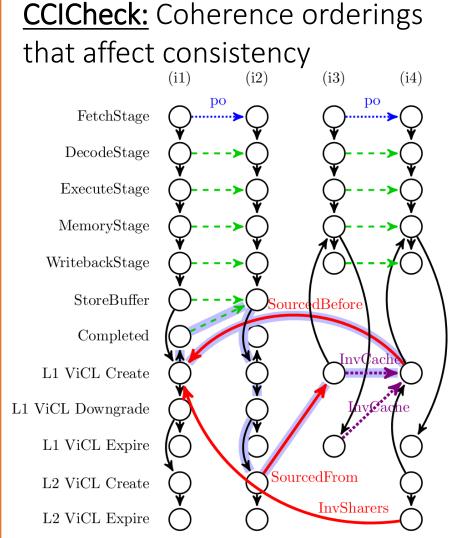

...and the methodology is extensible to other types of orderings!

<u>COATCheck:</u> Addr Translation/Virtual Memory orderings that affect consistency

### Does the µspec model match hardware?

**RTLCheck:** Validate that hardware supports µspec axioms!

### **PipeCheck Summary**

- Fast, automated verification

- Check hardware implementation against ISA spec

- Decompose HW verification into smaller per-axiom sub-problems

- Each axiom can then be each validated w.r.t RTL independently

- Open-Sourced:

https://github.com/daniellustig/coatcheck

Repo from this tutorial:

https://github.com/ymanerka/pipecheck\_tutorial

# Outline

- Introduction

- Motivating Example

- Overview of Our Work

- MCM Background & Our Approach

- PipeCheck: Verifying Hardware Implementations against ISA Specs

- Graph-based happens-before analysis of program executions on hardware

- µspec DSL for specifying axiomatic models of hardware

- TriCheck: Expanding to HW/SW Stack Interface Issues

- Looking forward: Other uses of tools and techniques

- CCICheck, COATCheck, SecurityCheck, ...

# **TriCheck:** Memory Model Verification at the Trisection of Software, Hardware, and ISA

#### Caroline Trippel, Yatin A. Manerkar, Daniel Lustig\*, Michael Pellauer\*, Margaret Martonosi

Princeton University

\*NVIDIA

ASPLOS 2017

http://check.cs.princeton.edu/

# Why is TriCheck Necessary?

- Memory model bugs are real and problematic!

- ARM Read-after-Read Hazard [Alglave et al. TOPLAS14]

- RISC-V ISA draft specification was incompatible with C11

- C11→POWER/ARMv7 "trailing-sync" compiler mapping [Batty et al. POPL '12]

This work

- C11→POWER/ARMv7 "leading-sync" compiler mapping [Lahav et al. PLDI17]

- ISAs are an important and still-fluid design point!

- Often, ISAs designed in light of desired HW optimizations

- ISA places some constraints on hardware and some on compiler

- Many industry memory models are still evolving: C11, ARMv7 vs. ARMv8

- New ISAs are designed, e.g., RISC-V CPUs, specialized accelerators

- Correctness requires cooperation of the whole stack

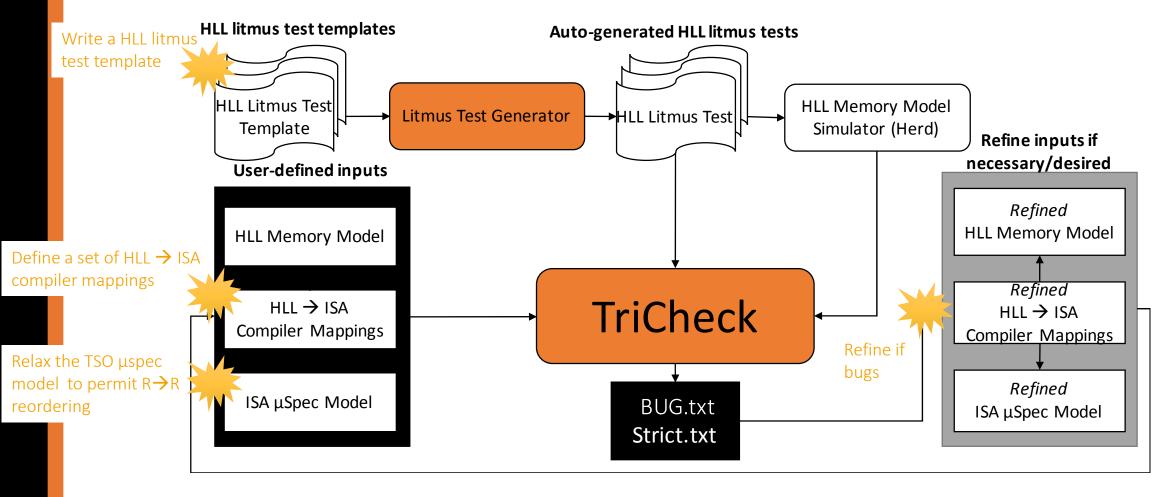

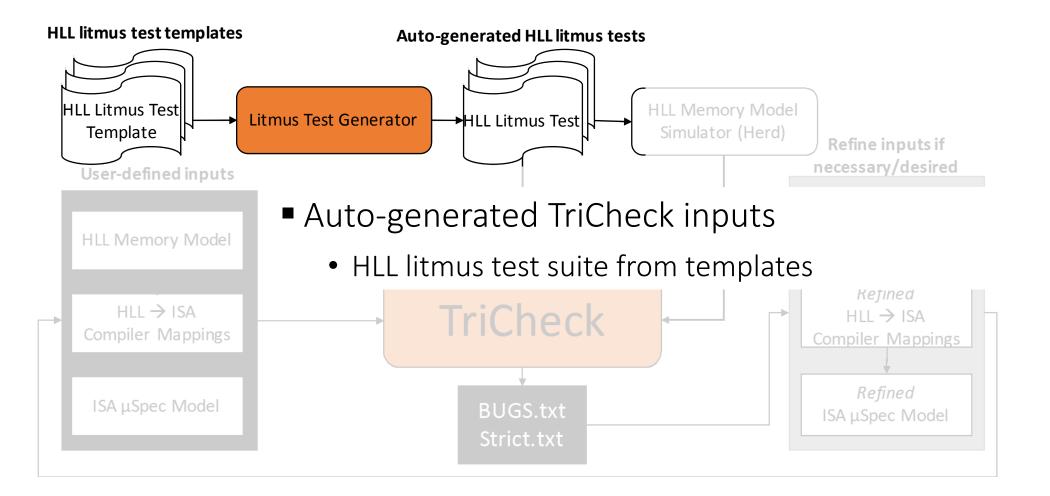

# TriCheck Key Ideas

#### First tool capable of full stack memory model verification

• Any layer can introduce real bugs

#### Litmus Tests + Auto-generators

• Comprehensive families of tests across HLL ordering options, compiler mapping variations, ISA options

#### Happens-before, graph-based analysis

- Nodes are memory accesses & ordering primitives

- Edges are event orders discerned via memory model relations

#### Efficient top-to-bottom analysis: Runtime in seconds or minutes

• Fast enough to find real bugs; Interactive design process

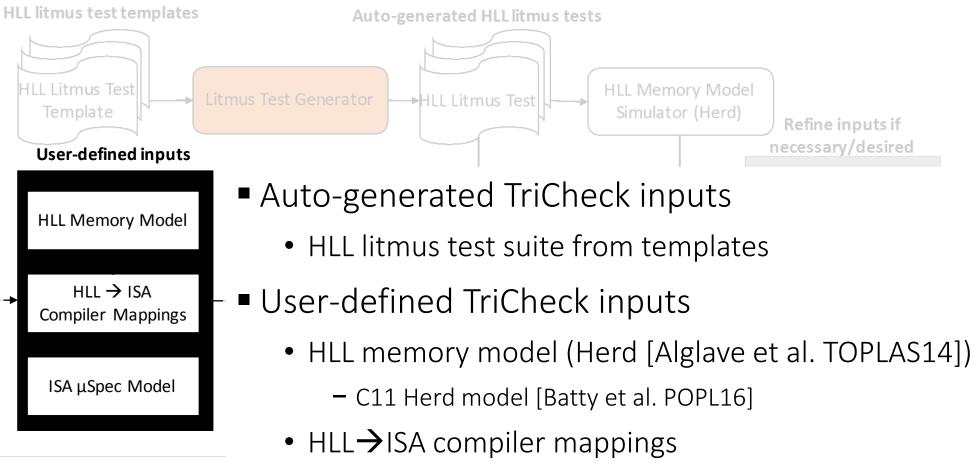

### **TriCheck Overview**

### Outline

- TriCheck Introduction

- Auto-generating HLL litmus tests

- User-defined TriCheck inputs

- Iterative ISA design example

- Bugs Found with TriCheck: RISC-V Case Study and Compiler Mappings

- Ongoing Work & Conclusions

NOTE: Before running TriCheck, define the \$TRICHECK\_HOME environment variable and install the parallel utility:

sudo apt-get update

export TRICHECK\_HOME=/home/check/TriCheck

sudo apt-get install parallel

### Auto-generating HLL litmus tests

### Litmus test templates

HLL is generally meant to compile/map to a variety of ISAs

- For a given litmus test, we want to evaluate all possible HLL-level formulations and ordering options

- Translates to evaluating a variety of compiler mapping and ISA options

- HLL litmus tests with placeholders for HLL-specific memory model ordering primitives

- E.g., C11 features the *atomic* type and allows programmers to place ordering constraints on memory accesses to *atomic* variables

- Stores to atomic variables can be specified as *relaxed, release,* or *seq\_cst*

- Loads of atomic variables can be specified as *relaxed, acquire\*, or seq\_cst*

- Litmus test templates path: \$TRICHECK\_HOME/tests/templates

### \$TRICHECK\_HOME/tests/templates/mp.litmus

```

C <TEST>

Message Passing (MP)

TΟ

Τ1

W \times \leftarrow 1 R y \leftarrow 1

[x] = 0;

W yV 1

R x ← 0

[y] = 0;

Non-SC Outcome

Forbidden

PO (atomic int* y, atomic int* x) {

atomic_store_explicit(x,1,memory_order_<ORDER_STORE>);

atomic_store_explicit(y,1,memory_order_<ORDER_STORE>);

P1 (atomic int* y, atomic int* x) {

int r0 = atomic load explicit(y,memory order <ORDER_LOAD>);

int r1 = atomic_load_explicit(x,memory_order_<ORDER_LOAD>);

Processor/Core ID

exists (0:r0=1 /\ 1:r1=0)

```

#### Exercise: \$TRICHECK\_HOME/tests/templates/sb.litmus

| C <test></test>                     | Store Buff | ering (SB)        |

|-------------------------------------|------------|-------------------|

| {                                   | PO         | P1                |

| [x] = 0;                            | W x ← 1    | ₩ y <b>←</b> 1    |

| [y] = 0;                            | R y ← 0 🖊  | R x ← 0           |

| }                                   |            | Outcome<br>hitted |

| P0 (atomic_int* y, atomic_int* x) { |            |                   |

| // store to x                       |            |                   |

| int r0 = // load of y               |            |                   |

| }                                   |            |                   |

| P1 (atomic_int* y, atomic_int* x) { |            |                   |

| // store to y                       |            |                   |

| int r1 = // load of x               |            |                   |

| }                                   |            |                   |

| exists ( )                          |            |                   |

#### Solution: \$TRICHECK\_HOME/tests/templates/sb.litmus

| C <test></test>                                                         | Store Buff | ering (SB) |  |  |

|-------------------------------------------------------------------------|------------|------------|--|--|

| {                                                                       | PO         | P1         |  |  |

| [x] = 0;                                                                | W x ← 1    | W y ← 1    |  |  |

| [x] = 0;<br>[y] = 0;                                                    | R y ← 0    | R x ← 0    |  |  |

| [y] = 0,                                                                | Non-SC (   | Outcome    |  |  |

| }                                                                       | Perm       | nitted     |  |  |

| P0 (atomic_int* y, atomic_int* x) {                                     |            |            |  |  |

| atomic_store_explicit(x,1,memory_order_< <b>ORDER_STORE&gt;</b> );      |            |            |  |  |

| int r0 = atomic_load_explicit(y,memory_order_< <b>ORDER_LOAD&gt;</b> ); |            |            |  |  |

| }                                                                       |            |            |  |  |

| P1 (atomic_int* y, atomic_int* x) {                                     |            |            |  |  |

| atomic_store_explicit(y,1,memory_order_< <b>ORDER_STORE</b> >);         |            |            |  |  |

| int r1 = atomic_load_explicit(x,memory_order_< <b>ORDER_LOAD&gt;</b> ); |            |            |  |  |

| }                                                                       |            |            |  |  |

| $\alpha_{i}$                                                            |            |            |  |  |

exists (0:r0=0 /\ 1:r1=0)

## Outline

- TriCheck Introduction

- Auto-generating HLL litmus tests

- User-defined TriCheck inputs

- Iterative ISA design example

- Bugs Found with TriCheck: RISC-V Case Study and Compiler Mappings

- Ongoing Work & Conclusions

# **User-defined Inputs**

• Hardware model (*µspec* DSL)

### User-defined input #1: HLL memory model

- For this tutorial, we will use the C11 HLL memory model, written in herd syntax from [Batty et al., POPL16]

- C11 herd model path: \$TRICHECK\_HOME/util/herd/c11\_partialSC.cat

### User-defined inputs #2 & #3: ISA

- ISA is a contract between hardware and software

- Sliding lever between what is required by compiler and what is required by microarchitecture

- TriCheck represents ISA as an input through:

- Compiler mappings

- Hardware model

### User-defined input #3: Hardware model

- Hardware model so we know primitives to use in compiler mappings

- Default TriCheck uarches path: \$TRICHECK\_HOME/uarches

#### Exercise: open \$TRICHECK\_HOME/uarches /TSO-RR.uarch

- Relax Ld-Ld order

- Enforce Ld-Ld order only for dependent operations

- Address dependencies affect Ld-Ld, Ld-St

- Data dependencies affect Ld-St

- Control dependencies affect Ld-Ld, Ld-St

# 1. Modify Execute\_stage\_is\_in\_order axiom

Modify axiom to permit Ld-Ld reordering:

"Execute stage is in order for all pairs of operations except two reads"

| Axiom "Execute_stage_is_in_order":                          |

|-------------------------------------------------------------|

| forall microops "i1",                                       |

| forall microops "i2",                                       |

| SameCore i1 i2 /\ ~( /\) /\                                 |

| <pre>EdgeExists ((i1, Fetch), (i2, Fetch), "") =&gt;</pre>  |

| AddEdge ((i1, Execute), (i2, Execute), "PPO", "darkgreen"). |

|                                                             |

# 1. Modify Execute\_stage\_is\_in\_order axiom

Modify axiom to permit Ld-Ld reordering:

"Execute stage is in order for all pairs of operations except two reads"

Axiom "Execute\_stage\_is\_in\_order": forall microops "i1", forall microops "i2", SameCore i1 i2 /\ ~(<u>IsAnyRead i1</u> /\ <u>IsAnyRead i2</u>) /\ EdgeExists ((i1, Fetch), (i2, Fetch), "") => AddEdge ((i1, Execute), (i2, Execute), "PPO", "darkgreen").

# 2. Enforce dependency order by default

- Relaxing Ld-Ld order requires axioms for address (addr) and control (ctrlisb) dependencies

- Make use of HasDependency <addr | data | ctrl | ctrlisb> <i1> <i2> predicate

"If two reads are related by a dependency of type <addr|ctrlisb>, they must execute in order"

| Axiom "Addr_Read_Rea<br>forall microops "i1",<br>forall microops "i2", | d_Dependencies":   |                                  |  |

|------------------------------------------------------------------------|--------------------|----------------------------------|--|

| SameCore i1 i2 /\                                                      | ∧                  | / HasDependency addr i1 i2 =>    |  |

| AddEdge ((i1,<br>Axiom "Ctrllsb Read Re                                |                    | _rr_dependency").                |  |

| forall microops "i1",                                                  | .uu_Dependencies . |                                  |  |

| forall microops "i2",<br>SameCore i1 i2 /\                             | $\wedge$           | ∧ HasDependency ctrlisb i1 i2 => |  |

| AddEdge ((i1,                                                          | ), (i2,), "ctrlis  |                                  |  |

## 2. Enforce dependency order by default

- Relaxing Ld-Ld order requires axioms for address (addr) and control (ctrlisb) dependencies

- Make use of HasDependency <addr | data | ctrl | ctrlisb> <i1> <i2> predicate

"If two reads are related by a dependency of type <addr|ctrlisb>, they must execute in order"

Axiom "Addr\_Read\_Read\_Dependencies": forall microops "i1", forall microops "i2", SameCore i1 i2 /\ <u>IsAnyRead i1</u> /\ <u>IsAnyRead i2</u> /\ HasDependency addr i1 i2 => AddEdge ((i1, <u>Execute</u>), (i2, <u>Execute</u>), "addr\_rr\_dependency").

Axiom "Ctrllsb\_Read\_Read\_Dependencies": forall microops "i1", forall microops "i2", SameCore i1 i2 /\ <u>IsAnyRead i1</u> /\ <u>IsAnyRead i2</u> /\ HasDependency ctrlisb i1 i2 => AddEdge ((i1, <u>Execute</u>), (i2, <u>Execute</u>), "ctrlisb").

### User-defined input #2: HLL → ISA compiler mappings

Compiler mappings have been proven correct for C11 to x86-TSO

| https://www.cl.cam.ac.uk/~pes20/cpp/cpp0xmappings.html |                        |  |

|--------------------------------------------------------|------------------------|--|

| C/C++11 Operation                                      | X86-TSO implementation |  |

| Load Relaxed:                                          | MOV                    |  |

| Load Acquire:                                          | MOV                    |  |

| Load Seq_Cst:                                          | MOV                    |  |

| Store Relaxed:                                         | MOV                    |  |

| Store Release:                                         | MOV                    |  |

| Store Seq Cst:                                         | MOV, MFENCE            |  |

#### Path to compiler mappings file: \$TRICHECK\_HOME/util/compile.txt

### User-defined input #2: HLL $\rightarrow$ ISA compiler mappings

This is how we would specify the C11 to TSO.uarch compiler mappings in compile.txt:

| C11/C++11 op  | prefix;pr | efix   suffix;suffix |

|---------------|-----------|----------------------|

| Read relaxed  | NA        | NA                   |

| Write relaxed | NA        | NA                   |

| Read acquire  | NA        | NA                   |

| Write release | NA        | NA                   |

| Read seq_cst  | NA        | NA                   |

| Write seq_cst | NA        | MMFENCE              |

### User-defined input #2: HLL $\rightarrow$ ISA compiler mappings

- <u>Exercise</u>: Modify these mappings for our new TSO-RR.uarch that relaxes Read → Read ordering.

- <u>Hint:</u> Load Acquire and Load Seq\_Cst require Read → Read order.

| C11/C++11 op  | pre | efix;prefix   suffix;suffix |

|---------------|-----|-----------------------------|

| Read relaxed  | NA  | NA                          |

| Write relaxed | NA  | NA                          |

| Read acquire  | NA  | NA                          |

| Write release | NA  | NA                          |

| Read seq_cst  | NA  | NA                          |

| Write seq_cst | NA  | MMFENCE                     |

### User-defined input #2: HLL $\rightarrow$ ISA compiler mappings

■ <u>Solution</u>: Modify these mappings for our new TSO-RR.uarch that relaxes Read → Read ordering.

• <u>Hint:</u> Load Acquire and Load Seq\_Cst require Read → Read order.

| C11/C++11 op  | prefix;pr | efix   suffix;suffix |

|---------------|-----------|----------------------|

| Read relaxed  | NA        | NA                   |

| Write relaxed | NA        | NA                   |

| Read acquire  | NA        | MMFENCE              |

| Write release | NA        | NA                   |

| Read seq_cst  | NA        | MMFENCE              |

| Write seq_cst | NA        | MMFENCE              |

## Outline

- TriCheck Introduction

- Auto-generating HLL litmus tests

- User-defined TriCheck inputs

- Iterative ISA design example

- Bugs Found with TriCheck: RISC-V Case Study and Compiler Mappings

- Ongoing Work & Conclusions

### Run TriCheck On Inputs

cd \$TRICHECK\_HOME/util

- ./release-generate-tests.py --all --fences

- ./release-run-all.py --pipecheck=/home/check/pipecheck\_tutorial/src

Path to litmus test generator: \$TRICHECK\_HOME/util/release-generate-tests.py Path to TriCheck: \$TRICHECK\_HOME/util/release-run-all.py

# **User-defined Inputs**

**HLL litmus test templates**

Auto-generated HLL litmus tests

el

**Refine inputs if** necessary/desired

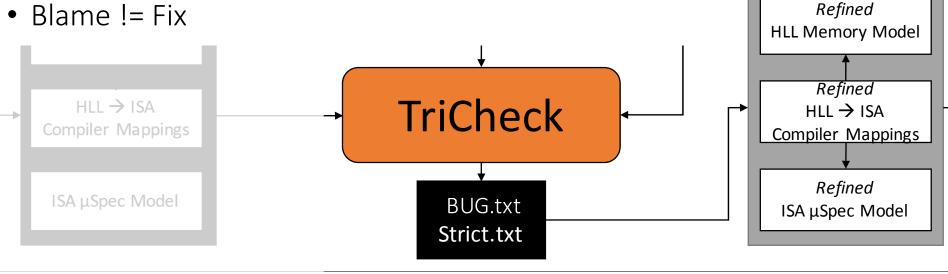

- Each iteration: bugs analyzed to identify cause

- Compiler bug, hardware implementation bug, ISA bug

- Blame may be debated

- Blame != Fix

### Create BUG.txt and Strict.txt

- cd \$TRICHECK\_HOME/util

- ./release-parse-results.py

- cat \$TRICHECK\_HOME/util/results/TSO-RR.uarch/BUG.txt

Path to TriCheck output parser: \$TRICHECK\_HOME/util/release-parse-results.py

### Create BUG.txt and Strict.txt

- cd \$TRICHECK\_HOME/util

- ./release-parse-results.py

- cat \$TRICHECK\_HOME/util/results/TSO-RR.uarch/BUG.txt

Bugs exist, so we must refine some combination of inputs and rerun...

## Analyzing a bug

- cd \$TRICHECK\_HOME/util/results/TSO-RR.uarch/corr

- gen\_graph -i corr\_R\_relaxed\_fence\_acquire\_fence\_W\_relaxed\_fence\_relaxed\_fence.test.gv

- evince corr\_R\_relaxed\_fence\_acquire\_fence\_W\_relaxed\_fence\_relaxed\_fence.test.pdf

C11 requires that all <u>same-</u> <u>address</u> reads of atomic locations execute in order.

### Fixing the bug...

- ARM fixed the bug by modifying the compiler, so we'll do the same thing here...

- Modify compiler mapping in \$TRICHECK\_HOME/util/compile.txt

| C/C++11 Operation | TSO-RR implementation |

|-------------------|-----------------------|

| Load Relaxed:     | Read, MMFENCE         |

| Load Acquire:     | Read, MMFENCE         |

| Load Seq_Cst:     | Read, MMFENCE         |

| Store Relaxed:    | Write                 |

| Store Release:    | Write                 |

| Store Seq Cst:    | Write, MMFENCE        |

| C11/C++11 op  | pre | fix;prefix   suffix;suffix |

|---------------|-----|----------------------------|

| Read relaxed  | NA  | MMFENCE                    |

| Write relaxed | NA  | NA                         |

| Read acquire  | NA  | MMFENCE                    |

| Write release | NA  | NA                         |

| Read seq_cst  | NA  | MMFENCE                    |

| Write seq_cst | NA  | MMFENCE                    |

## Run TriCheck On Refined Inputs

- cd \$TRICHECK\_HOME/util

- rm –r \$TRICHECK\_HOME/util/tests/ctests/\*/pipecheck

- ./release-generate-tests.py --all --fences

- ./release-run-all.py --pipecheck=/home/check/pipecheck\_tutorial/src

- ./release-parse-results.py

- cat \$TRICHECK\_HOME/util/results/TSO-RR.uarch/BUG.txt

### Outline

- TriCheck Introduction

- Auto-generating HLL litmus tests

- User-defined TriCheck inputs

- Iterative ISA design example

- Bugs Found with TriCheck: RISC-V Case Study and Compiler Mappings

- Ongoing Work & Conclusions

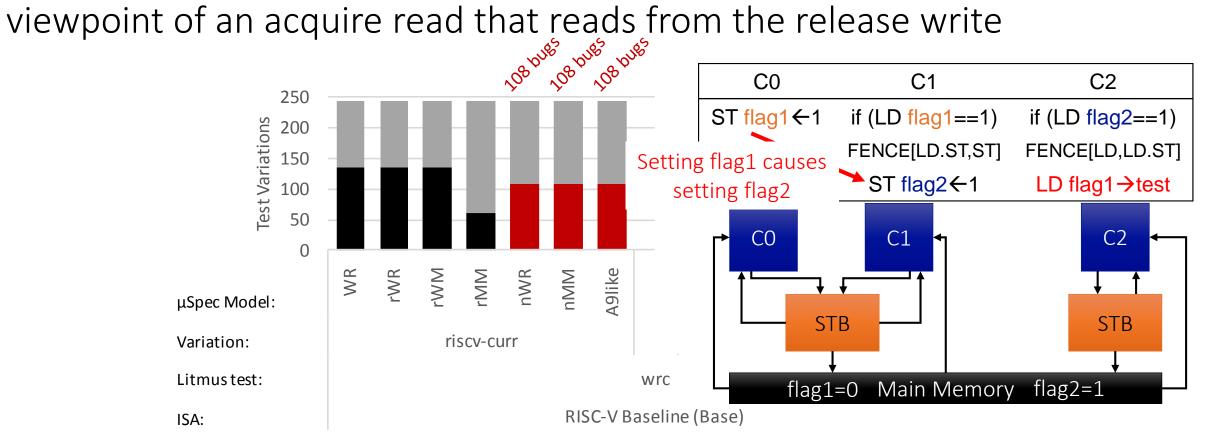

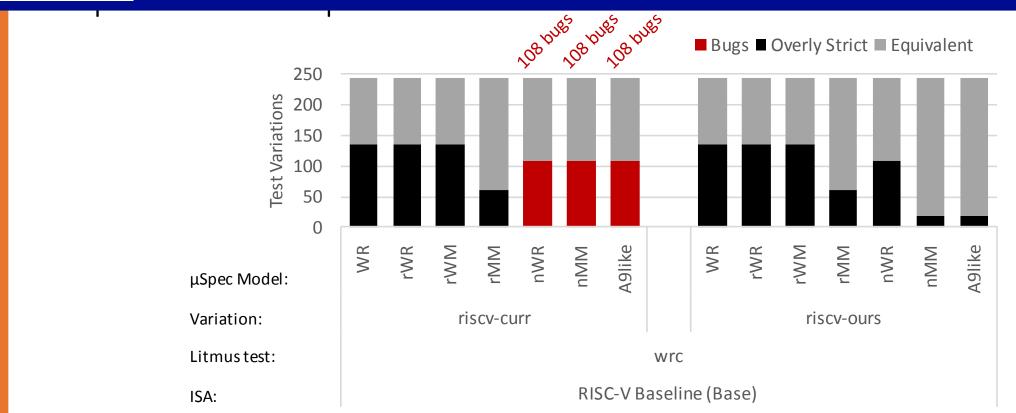

### **RISC-V** Case Study

Create µspec models for 7 distinct RISC-V implementation possibilities:

- All abide by current RISC-V spec

- Vary in preserved program order and store atomicity

- Started with stricter-than-spec microarchitecture: RISC-V Rocket Chip

- TriCheck detects **bugs**: refine for correctness

- TriCheck detects over-strictness: Performed legal (per RISC-V spec) hardware relaxations

- Impossible to compile C11 for RISC-V as originally specified

- Out of 1,701 tested C11 programs:

- RISC-V-Base-compliant design allows 144 buggy outcomes

- RISC-V-Base+A-compliant design allows 221 buggy outcomes

# **RISC-V Base:** Lack of Cumulative Fences

| <b>Initial conditions</b> : x=0, y=0                  |                |                |

|-------------------------------------------------------|----------------|----------------|

| T0                                                    | T1             | T2             |

| a: sw x1, (x5)                                        | b: lw x2, (x5) | e: lw x3, (x6) |

|                                                       | c: fence rw, w | f: fence r, rw |

|                                                       | d: sw x2, (x6) | g: lw x4, (x5) |

| <b>Forbidden HLL Outcome</b> : x1=1, x2=1, x3=1, x4=0 |                |                |

C11 acquire/release synchronization is transitive: accesses <u>before a</u> release write in program order, and <u>observed by the releasing core prior</u> to the release write must be ordered before the release from the viewpoint of an acquire read that reads from the release write

# **RISC-V Base:** Lack of Cumulative Fences

#### **Base RISC-V ISA lacks cumulative fences**

- Cumulative fence needed to enforce order between different-thread accesses

- Cannot fix bugs by modifying compiler

#### Our solution: add cumulative fences to the Base RISC-V ISA

Initial conditions: x=0, y=0

T0

T1

T2

a: sw x1, (x5)

b: lw x2, (x5)

e: lw x3, (x6)

c: fence rw, w

f: fence r, rw

d: sw x2, (x6)

g: lw x4, (x5)

Forbidden HLL Outcome: x1=1, x2=1, x3=1, x4=0

### More results in the paper:

### Both Base and Base+A:

- Lack of cumulative lightweight fences

- Lack of cumulative heavyweight fences Like tutorial example

- Re-ordering of same-address loads

- No dependency ordering, but Linux port assumes it

- Base+A only:

- Lack of cumulative releases; no acquire-release synchronization

- No roach-motel movement

Since publishing these results, a RISC-V Memory Model Working Group was formed to design a robust MCM specification for the RISC-V ISA that meets the needs of RISC-V users and supports C11.

As of a few days ago, the new MCM proposal passed the 45 day ratification period.

### Evaluating Compiler Mappings with TriCheck

- During RISC-V analysis, we discovered two counter-examples while using the "proven-correct" *trailing-sync* mappings for compiling C11 to POWER/ARMv7

- Also incorrect: the proof for the C11 to POWER/ARMv7 trailingsync compiler mappings [Manerkar et al., CoRR '16]

### **TriCheck Conclusions**

Memory model design choices are complicated =>

- Verification calls for automated analysis to comprehensively tackle subtle interplay between many diverse features.

- TriCheck uncovered flaws in the RISC-V memory model...

- But more generally, TriCheck can be used on any ISA.

- Languages and Compilers matter too...

- TriCheck uncovered bugs in the trailing-sync compiler mapping from C11 to POWER/ARMv7

### Outline

- Introduction

- Motivating Example

- Overview of Our Work

- MCM Background & Our Approach

- PipeCheck: Verifying Hardware Implementations against ISA Specs

- Graph-based happens-before analysis of program executions on hardware

- µspec DSL for specifying axiomatic models of hardware

- TriCheck: Expanding to HW/SW Stack Interface Issues

- Looking forward: Other uses of tools and techniques

- CCICheck, COATCheck, SecurityCheck, ...

## **COATCheck:** Verifying Memory Ordering at the Hardware-OS Interface

### Daniel Lustig, Geet Sethi<sup>+</sup>, Michael Pellauer<sup>\*</sup>, Margaret Martonosi, Abhishek Bhattacharjee <sup>+</sup>

Princeton University \*Rutgers University \*NVIDIA

ASPLOS 2016

http://check.cs.princeton.edu/

### Simple Motivating Example

| Initially: [x]=0, [y]=0      |                        |  |

|------------------------------|------------------------|--|

| Thread 0                     | Thread 1               |  |

| St $[x] \leftarrow 1$        | St [y] $\leftarrow$ 2  |  |

| Ld [y] $ ightarrow$ r1       | Ld [x] $ ightarrow$ r2 |  |

| Proposed outcome: r1=2, r2=1 |                        |  |

Permitted if x and y are different addresses

| Initially: [                 | x]=0, [y]=0             |

|------------------------------|-------------------------|

| Thread 0                     | Thread 1                |

| St PA1 $\leftarrow$ 1        |                         |

|                              | St PA2←2                |

|                              | Ld PA1 $\rightarrow$ r2 |

| Ld PA2 $\rightarrow$ r1      |                         |

| Outcome r1=2, r2=1 permitted |                         |

Forbidden if x and y are synonyms

| Initially: [:               | x]=0, [y]=0             |

|-----------------------------|-------------------------|

| Thread 0                    | Thread 1                |

| St PA1 $\leftarrow$ 1       |                         |

|                             | St PA1 $\leftarrow$ 2   |

|                             | Ld PA1 $\rightarrow$ r2 |

| Ld PA1 $\rightarrow$ r1     |                         |

| Outcome r1=2,r2=1 forbidden |                         |

### "Transistency Model"

- Memory ordering verification is fundamentally incomplete unless it explicitly accounts for address translation

- Superset of consistency which captures all address translation-aware sets of ordering rules

- Most prior techniques ignore the implications of virtual-to-physical address translation on memory ordering

- E.g., synonyms, and page permission updates

- Microarchitectural events and OS behavior can affect memory ordering in ways for which standard memory model analysis can be fundamentally insufficient

## Ongoing Work

- We've seen how memory model bugs can result in in correct program outcomes that are intermittent/unpredictable

- Currently, we are applying our techniques of exhaustive enumeration and checking of event orderings to other domains

- Security: Is a hardware design susceptible to a given class of security exploits?

- Hardware-aware exploit program synthesis

- We auto-synthesized programs representative of Meltdown & Spectre

- We also synthesized 2 new exploits related to Meltdown & Spectre but distinct

- <u>https://arxiv.org/abs/1802.03802</u>

- IoT: how do we reason about many concurrently acting IoT devices?

### Takeaways

- Memory consistency modes matter

- Reliability, correctness, and portability

- Performance

- Security

- Intuitive "checking" through automated verification

- Move memory model verification earlier in the design processes

- Evaluate across interfaces and design boundaries

- If interfaces are often source of bugs

- Speed of approach enables new oppertunities

- Comprehenseive and fast verification for iterative design

### http://check.cs.princeton.edu/