## Daradlel Computer Architechtures Shared Memory Ability for all processors to access all memory as global address space. Multiple processors can operate independently but share the same memory resources. Changes in a memory location effected by one processor are visible to all other processors (caching systems!) Uniform Memory Access (UMA): Equal access and access times to memory. CC-UMA - Cache Coherent UMA. Non-Uniform Memory Access (NUMA): Not all processors have equal access time to all memories. If cache coherency is maintained: CC-NUMA - Cache Coherent NUMA Virtual Shared Memory Access: Use caching techniques and software to create a VSM (Hagersten et al.)

2009-08-17

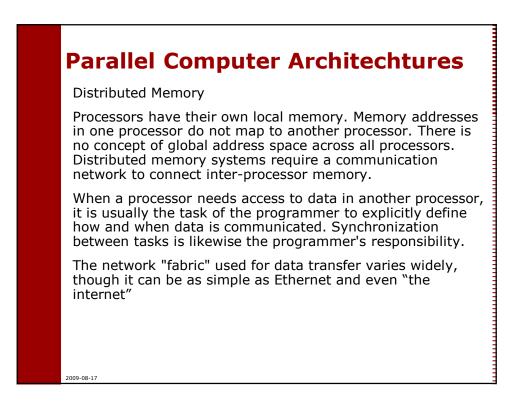

| Distributed Memory Models                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Distributed Memory / Message Passing Model                                                                                                                                                                                                             |

| A set of tasks that use their own local memory during computation. Multiple tasks can reside on the same physical machine and/or across an arbitrary number of machines. Tasks exchange data through communications by sending and receiving messages. |

| Data transfer usually requires cooperative operations to be performed by each process. For example, a send operation must have a matching receive operation.                                                                                           |

| Implementations:                                                                                                                                                                                                                                       |

| A library of subroutines. Calls to these subroutines are imbedded in source code. The programmer is responsible for determining all parallelism.                                                                                                       |

| MPI is the "de facto" industry standard for message passing.<br>Not all implementations include everything in MPI-1, MPI-2 or<br>MPI-3.                                                                                                                |

| 2009-08-17                                                                                                                                                                                                                                             |

2009-08-17